# ALTAIP 8800

# **OPERATORS MANUAL**

.

a a

## ALTAIR 8800 OPERATOR'S MANUAL

#### TABLE OF CONTENTS

PART ONE: Introduction.....2

(Logic, Electric Logic, Number Systems, The Binary System, The Octal System, Computer Programming, A Simple Program, Computer Languages)

PART TWO: Organization of the Altair.....19

(Central Processing Unit, Memory, Clock, Input/Output)

PART THREE: Operation of the Altair.....28

(Front Panel Switches and LED's, Loading a Sample Program, Using the Memory, Memory Addressing, Operating Hints)

PART FOUR: Altair 8800 Instruction Set.....42

(Command Instructions, Single Register Instructions, Register Pair Instructions, Rotate Accumulator Instructions)

• MITS, Inc., 1975

PRINTED IN U.S.A.

6328 LINN, N.E., P.O. BOX 8636, ALBUQUERQUE, N.M. 87108 U.S.A. 505/265-7553

#### PART 1 INTRODUCTION

2

Remarkable advances in semiconductor technology have made possible the development of the *ALTAIR 8800*, the most economical computer ever and the first available in both kit and assembled form. The heart of the *ALTAIR 8800* is Intel Corporation's Model 8080 Microcomputer, a complete Central Processing Unit on a single silicon chip. Fabricated with N-channel large scale integrated circuit (LSI) metal-oxidesemiconductor (MOS) technology, Intel's 8080 Microcomputer on a chip represents a major technological breakthrough.

This operating manual has been prepared to acquaint both the novice and the experienced computer user in the operation of the *ALTAIR 8800*. The computer has 78 machine language instructions and is capable of performing several important operations not normally available with conventional mini-computers. After reading this manual, even a novice will be able to load a program into the *ALTAIR 8800*.

Users of the *ALTAIR 8800* include persons with a strong electronics background and little or no computer experience and persons with considerable programming experience and little or no electronics background. Accordingly, this manual has been prepared with all types of users in mind. Part 1 of the manual prepares the user for better understanding computer terminology, technology, and operation with an introduction to conventional and electronic logic, a description of several important number systems, a discussion of basic programming, and a discourse on computer languages.

Parts 2 and 3 in the manual describe the organization and operation of the *ALTAIR 8800*. Emphasis is placed on those portions of the computer most frequently utilized by the user. Finally, Part 4 of the manual presents a detailed listing of the *ALTAIR 8800's* 78 instructions. An Appendix condenses the instructions into a quick reference listing.

Even if you have little or no experience in computer operation and organization, a careful reading of this manual will prepare you for operating the *ALTAIR 8800*. As you gain experience with the machine, you will soon come to understand its truly incredible versatility and data processing capability. Don't be discouraged if the manual seems too complicated in places. Just remember that a computer does only what its programmer instructs it to do.

#### A. LOGIC

George Boole, a ninteenth century British mathematician, made a detailed study of the relationship between certain fundamental logical expressions and their arithmetic counterparts. Boole did not equate mathematics with logic, but he did show how any logical statement can be analyzed with simple arithmetic relationships. In 1847, Boole published a booklet entitled <u>Mathematical Analysis of Logic</u> and in 1854 he published a much more detailed work on the subject. To this day, all practical digital computers and many other electronic circuits are based upon the logic concepts explained by Boole.

Boole's system of logic, which is frequently called Boolean algebra, assumes that a logic condition or statement is either true or false. It cannot be both true and false, and it cannot be partially true or partially false. Fortunately, electronic circuits are admirably suited for this type of dual-state operation. If a circuit in the ON state is said to be true and a circuit in the OFF state is said to be false, an electronic analogy of a logical statement can be readily synthesized.

With this in mind, it is possible to devise electronic equivalents for the three basic logic statements: AND, OR and NOT. The AND statement is true if and only if either or all of its logic conditions are true. A NOT statement merely reverses the meaning of a logic statement so that a true statement is false and a false statement is true.

It's easy to generate a simple equivalent of these three logic statements by using on-off switches. A switch which is ON is said to be true while a switch which is OFF is said to be false. Since a switch which is OFF will not pass an electrical current, it can be assigned a numerical value of O. Similarly, a switch which is ON does pass an electrical current and can be assigned a numerical value of 1.

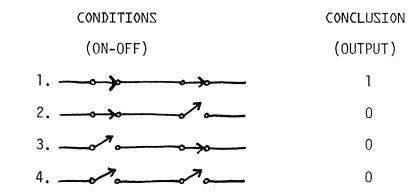

We can now devise an electronic equivalent of the logical AND statement by examining the various permutations for a two condition AND statement:

| CONDITIONS         | CONCLUSION |

|--------------------|------------|

| (Inputs)           | (Output)   |

| 1. True AND True   | True       |

| 2. True AND False  | False      |

| 3. False AND True  | False      |

| 4. False AND False | False      |

The electronic ON-OFF switch equivalent of these permutations is simply:

Similarly, the numerical equivalents of these permutations is:

| CONDITIONS | CONCLUSION |

|------------|------------|

| (Inputs)   | (Output)   |

| 1. 1 AND 1 | 1          |

| 2. 1 AND 0 | 0          |

| 3. 0 AND 1 | 0          |

| 4. 0 AND 0 | 0          |

Digital design engineers refer to these table of permutations as <u>truth tables</u>. The truth table for the AND statement with two conditions is usually presented thusly:

| А | В | OUT |

|---|---|-----|

| 1 | 1 | 1   |

| 0 | 1 | 0   |

| 1 | 0 | 0   |

| 0 | 0 | 0   |

FIGURE 1-1. AND Function Truth Table

It is now possible to derive the truth tables for the OR and NOT statements, and each is shown in Figures 1-2 and 1-3 respectively.

| Α | В      | OUT |

|---|--------|-----|

| 1 | ٦<br>٦ | 1   |

| 0 | 1      | 1   |

| 1 | 0      | 1   |

| 0 | 0      | 0   |

FIGURE 1-2. OR Function Truth Table

| А | OUT |

|---|-----|

| 1 | 0   |

| 0 | ]   |

FIGURE 1-3. NOT Function Truth Table

5

.

#### B. ELECTRONIC LOGIC

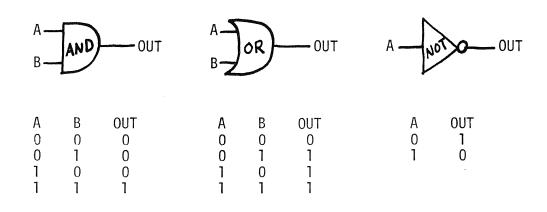

All three of the basic logic functions can be implemented by relatively simple transistor circuits. By convention, each circuit has been assigned a symbol to assist in designing logic systems. The three symbols along with their respective truth tables are shown in Figure 1-4.

FIGURE 1-4. The Three Main Logic Symbols

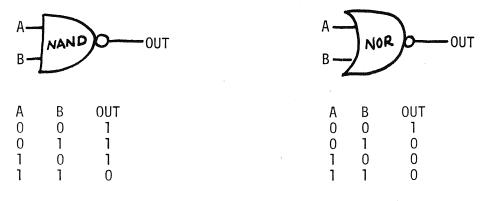

The three basic logic circuits can be combined with one another to produce still more logic statement analogies. Two of these circuit combinations are used so frequently that they are considered basic logic circuits and have been assigned their own logic symbols and truth tables. These circuits are the NAND (NOT-AND) and the NOR (NOT-OR). Figure 1-5 shows the logic symbols and truth tables for these circuits.

FIGURE 1-5. The NAND and NOR Circuits

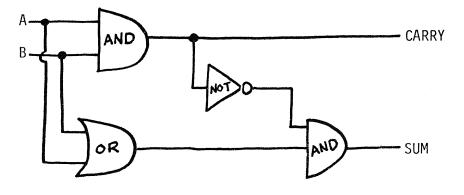

Three or more logic circuits make a logic system. One of the most basic logic systems is the EXCLUSIVE-OR circuit shown in Figure 1-6.

FIGURE 1-6. The EXCLUSIVE-OR Circuit

The EXCLUSIVE-OR circuit can be used to implement logical functions, but it can also be used to add two input conditions. Since electronic logic circuits utilize only two numerical units, 0 and 1, they are compatible with the binary number system, a number system which has only two digits. For this reason, the EXCLUSIVE-OR circuit is often called a binary adder.

7

Various combinations of logic circuits can be used to implement numerous electronic functions. For example, two NAND circuits can be connected to form a bistable circuit called a flip-flop. Since the flip-flop changes state only when an incoming signal in the form of a pulse arrives, it acts as a short term memory element. Several flip-flops can be cascaded together to form electronic counters and memory registers.

Other logic circuits can be connected together to form monostable and astable circuits. Monostable circuits occupy one of two states unless an incoming pulse is received. They then occupy an opposite state for a brief time and then resume their normal state. Astable circuits continually switch back and forth between two states.

#### C. NUMBER SYSTEMS

Probably because he found it convenient to count with his fingers, early man devised a number system which consisted of ten digits. Number systems, however, can be based on any number of digits. As we have already seen, dual-state electronic circuits are highly compatible with a two digit number system, and its digits are termed <u>bits</u> (<u>binary digits</u>). Systems based upon eight and sixteen are <u>also</u> compatible with complex electronic logic systems such as computers since they provide a convenient shorthand method for expressing lengthy binary numbers.

#### D. THE BINARY SYSTEM

Like virtually all digital computers, the *ALTAIR 8800* performs nearly all operations in binary. A typical binary number processed by the computer incorporates 8-bits and may appear as: 10111010. A fixed length binary number such as this is usually called a word or byte, and computers are usually designed to process and store a fixed number of words (or bytes).

A binary word like 10111010 appears totally meaningless to the novice. But since binary utilizes only two digits (bits), it is actually much simpler than the familiar and traditional decimal system. To see why, let's derive the binary equivalents for the decimal numbers from 0 to 20. We will do this by simply adding 1 to each successive number until all the numbers have been derived. Counting in any number system is governed by one basic rule: Record successive digits for each count in a column. When the total number of available digits has been used, begin a new column to the left of the first and resume counting.

Counting from 0 to 20 in binary is very easy since there are only two digits (bits). The binary equivalent of the decimal 0 is 0. Similarly, the binary equivalent of the decimal 1 is 1. Since both available bits have now been used, the binary count must incorporate a new column to form the binary equivalent for the decimal 2. The result is 10. (Incidentally, ignore any resemblance between binary and decimal numbers. Binary 10 is not decimal 10!) The binary equivalent of the decimal number 3 is 11. Both bits have been used again, so a third column must be started to obtain the binary equivalent for the decimal number 4 (100). You should now be able to continue counting and derive all the remaining binary equivalents for the decimal numbers 0 to 20:

| DECIMAL | BINARY |

|---------|--------|

| 0       | 0      |

| 1       | 1      |

| 2       | 10     |

| 3       | 11     |

| DECIMAL | BINARY |

|---------|--------|

| 4       | 100    |

| 5       | 101    |

| 6       | 110    |

| 7       | 111    |

| 8       | 1000   |

| 9       | 1001   |

| 10      | 1010   |

| 11      | 1011   |

| 12      | 1100   |

| 13      | 1101   |

| 14      | 1110   |

| 15      | 1111   |

| 16      | 10000  |

| 17      | 10001  |

| 18      | 10010  |

| 19      | 10011  |

| 20      | 10100  |

|         |        |

A simple procedure can be used to convert a binary number into its decimal equivalent. Each bit in a binary number indicates by which power of two the number is to be raised. The sum of the powers of two gives the decimal equivalent for the number. For example, consider the binary number 10011:

$10011 = [(1x2^4) + (0x2^3) + (0x2^2) + (1x2^1) + (1x2^0)]$

= [(16) + (0) + (0) + (2) + (1)]

= 19

#### E. THE OCTAL SYSTEM

12

Since the binary system has only two bits, it doesn't take long to accumulate a long string of Os and ls. For example, a six-digit decimal number requires 19 bits.

Lengthy binary numbers can be simplified by dividing them into groups of three bits and assigning a decimal equivalent to each 3-bit group. Since the highest 3-bit binary number corresponds to the decimal 7, eight combinations of Os and 1s are possible (0-7).

The basic ALTAIR 8800 accepts a binary input, and any binary number loaded into the machine can be simplified into octal format. Of course the octal numbers must be changed back to binary for entry into the computer, but since only eight bit patterns are involved the procedure is both simple and fast. A typical binary instruction for the ALTAIR 8800 is: 11101010. This instruction can be converted to octal by first dividing the number into groups of three bits beginning with the least significant bit: 11 101 010. Next, assign the decimal equivalent to each of the three bit patterns:

#### 11 101 010

#### 3 5 2

Therefore, 11 101 010 in binary corresponds to 352 in octal. To permit rapid binary to octal conversion throughout the remainder of this manual, most binary numbers will be presented as groups of three bits.

#### F. COMPUTER PROGRAMMING

As will become apparent in Part 2, the Central Processing Unit (CPU) of a computer is essentially a network of logic circuits and systems whose interconnections or organization can be changed by the user. The computer can therefore be thought of as a piece of <u>variable hardware</u>. Implementation of variations in a computer's hardware is achieved with a set of programmed instructions called software.

The software instructions for the *ALTAIR 8800* must be loaded into the machine in the form of sequential 8-bit words called <u>machine language</u>. This and other more advanced computer languages will be discussed later.

The basics of computer programming are quite simple. In fact, often the most difficult part of programming is defining the problem you wish to solve with the computer. Below are listed the three main steps in generating a program:

- 1. Defining the Problem

- 2. Establishing an Approach

- 3. Writing the Program

Once the problem has been defined, an approach to its solution can be developed. This step is simplified by making a diagram which shows the orderly, step-by-step solution of the problem. Such a diagram is called a <u>flow diagram</u>. After a flow diagram has been made, the various steps can be translated into the computer's language. This is the easiest of the three steps since all you need is a general understanding of the instructions and a list showing each instruction and its machine language equivalent.

The *ALTATR 8800* has an extensive programming capability. For example, a program can cause data to be transferred between the computer's memory and the CPU. The program can even cause the computer to make logical decisions. For example, if a specified condition is met, the computer can jump from one place in the program to any other place and continue program execution at the new place. Frequently used special purpose programs can be stored in the computer's memory for later retrieval and use by the main program. Such a special purpose program is called a subroutine. The *ALTAIR 8800* instructions are described in detail in Part 4 of this manual.

· .

•

.

#### G. A SIMPLE PROGRAM

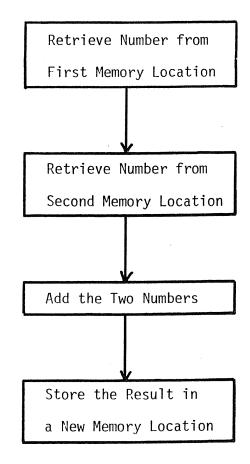

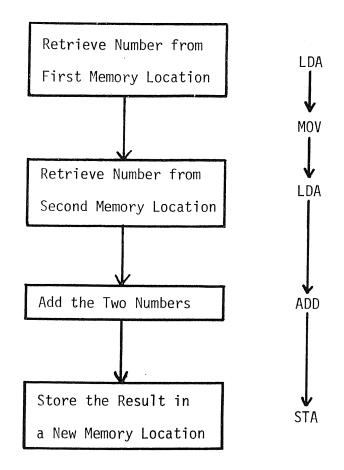

Assume you wish to use the *ALTAIR 8800* to add two numbers located at two different memory locations and store the result elsewhere in the memory. Of course this is a very simple problem, but it can be used to illustrate several basic programming techniques. Here are the steps used in generating a program to solve this problem:

1. Define the Problem--Add two numbers located in memory and store the result elsewhere in memory.

2. Establish an Approach--A flow diagram can now be generated:

3. Write the Program--Translating the flow diagram into a language or format suitable for use by the computer may seem complicated at first. However, a general knowledge of the computer's organization and operation makes the job simple. In this case, the four part flow diagram translates into five separate instructions:

These instructions may seem meaningless now, but their meaning and application will become much clearer as you proceed through this manual. For example, the need for the extra instruction (MOV) will become more obvious after you learn that the computer must temporarily store the first number retrieved from memory in a special CPU memory called a register. The first number is stored in the register until it can be added to the second number.

#### H. COMPUTER LANGUAGES

The software for any computer must be entered into the machine in the form of binary words called <u>machine lan-guage</u>. Machine language programs are generally written with the help of <u>mnemonics</u> which correspond to the bit patterns for various instructions. For example, 10 000 111 is an add instruction for the *ALTAIR 8800* and the corresponding mnemonic is ADD A. Obviously the mnemonic ADD A is much more convenient to remember than its corresponding machine language bit pattern.

Ultimately, however, the machine language bit pattern for each instruction must be entered into the computer one step at a time. Some instructions may require more than one binary word. For example, an *ALTAIR 8800* instruction which references a memory address such as JMP requires one word for the actual instruction and two subsequent words for the memory address.

Machine language programs are normally entered into the *ALTAIR 8800* by means of the front panel switches. A computer terminal can be used to send the mnemonics signal to the computer where it is converted into machine language by a special set of instructions (software) called an assembler.

Even more flexibility is offered by a highly complex software package called a <u>compiler</u> which converts higher order mnemonics into machine language. Higher order mnemonics are a type of computer language shorthand which automatically replace as many as a dozen or more machine language instructions with a single, easily recognized mnemonic. Advanced computer languages such as FORTRAN, BASIC, COBAL, and others make use of a compiler.

The higher computer languages provide a great deal of simplification when writing computer programs, particularly those that are lengthy. They are also very easy to remember. The potential versatility of machine language programming should not be underestimated, however, and an excellent way to realize the full potential of a higher language is to learn to apply machine language.

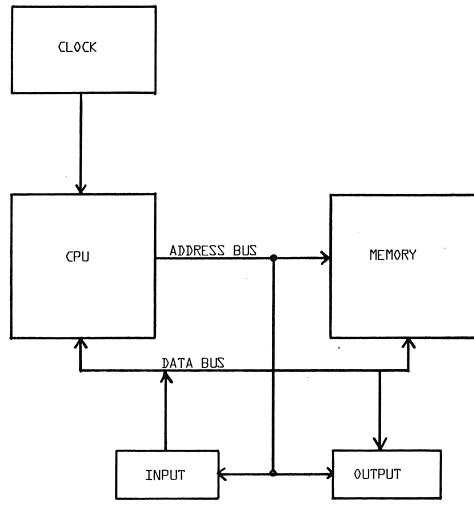

### PART 2 ORGANIZATION OF THE ALTAIR 8800

A block diagram showing the organization of the *ALTAIR* 8800 is shown in Figure 2-1. It is not necessary to understand the detailed electronic operation of each part of the computer to make effective use of the machine. However, a general understanding of each of the various operating sections is important.

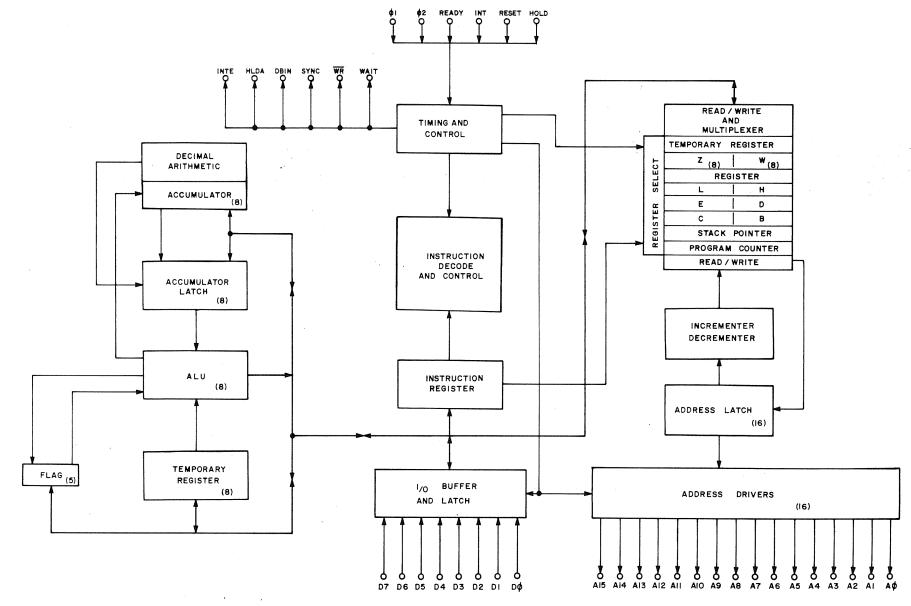

FIGURE 2-2. CPU Diagram

# A. CENTRAL PROCESSING UNIT (CPU)

The Central Processing Unit (CPU) performs all arithmetic calculations, makes all logical decisions, controls access to the computer by input and output devices, stores and retrieves data from the memory, and coordinates the orderly execution of a program. The CPU is quite literally the heart of the computer.

Of course it is important to remember that the CPU is only as intelligent as the programmer, for the CPU must be instructed in precise terms just how to perform a particular operation. But since the CPU in the *ALTAIR 8800* can execute a complete instruction cycle in only 2 microseconds\*, the computer can solve a highly complex problem in an incredibly brief time. In fact, the *ALTAIR 8800* can execute a six instruction addition program approximately 30,000 times in one second.

The compact size and economy of the *ALTAIR 8800* is in large part due to the CPU. Thanks to large scale integrated circuit techniques (LSI), the CPU used in the *ALTAIR 8800* is fabricated on a tiny silicon chip having a surface area of only a fraction of an inch. This chip, the Intel 8080, is installed in a protective dual-in-line mounting package having 40 pins.

The CPU is by far the most complex portion of the *ALTAIR* 8800. A complete block diagram of the CPU is shown in Figure 2-2, and while it is not necessary to possess a detailed understanding of this diagram it is important to understand the role of some of the CPU's more important systems. The interrelationship of each of these systems and their contribution to the operation of the CPU will then become more obvious.

1. TIMING AND CONTROL--The timing and Control System receives timing signals from the clock and distributes them to the appropriate portions of the CPU in order to insure coordinated instruction execution. The Timing and Control System also activates several front panel status indicators (HOLD, WAIT, INTE, STACK, OUT, IN, INP, MI MENR, HLTA, WO, INT).

\*A microsecond is one millionth of a second.

2. INSTRUCTION REGISTER--Binary machine language instructions are temporarily stored in the Instruction Register for decoding and execution by the CPU.

3. ARITHMETIC--The Arithmetic System performs both binary and decimal arithmetic. All arithmetic operations are performed by addition. Multiplication is implemented by repetitive addition. Subtraction and division are implemented by inverse addition.

4. WORKING REGISTERS--The CPU contains seven 8-bit Working Registers. The most important of these is the Accumulator, the register into which the results of many operations are eventually loaded. In addition to acting as a primary storage point for results of many program operations, numerous arithmetic and logical operations can be performed with the Accumulator and any specified register or memory address.

The six remaining registers, which are arranged in pairs to permit 16-bit operation when necessary, are "scratchpad" registers. This simply means they are used to store temporary data or addresses on a regular basis and are available for numerous program operations.

Figure 2-3 shows the arrangement and classification of the seven Working Registers. The additional register adjacent to the Accumulator, the Status Bit Register, is a special purpose register used to store the status of certain operations.

| Register Pair B>     | В | С |

|----------------------|---|---|

| Register Pair D ———> | D | Ē |

| Register Pair H>     | Н | L |

| Register Pair PSW —> | * | А |

\*Status Bit Register (See Text)

FIGURE 2-3. The Working Registers

5. STATUS BIT REGISTER--The Status Bit Register is a special purpose register which stores the status of five conditions which may or may not be affected by the result of a data operation. This register contains 8-bit positions, but only 5-bits are used to store the status information. The five status bits are:

a. Carry Bit--This bit is set to 1 if a carry has occurred. The Carry Bit is usually affected by such operations as addition, subtraction, rotation, and some logical decisions. The bit is set to 0 if no carry occurs.

b. Auxiliary Carry Bit--If set to 1, this bit indicates a carry out of bit 3 of a result. O indicates no carry. This status bit is affected by only one instruction (DAA).

c. Sign Bit--This bit is set to show the sign of a result. If set to 1, the result is minus; if set to 0 the result is plus. The Sign Bit reflects the condition of the most significant bit in the result (bit 7). This is because an 8-bit byte can contain up to the decimal equivalent of from -128 to +127 if the most significant bit is used to indicate the polarity of the result.

d. Zero Bit--This bit is set to 1 if the result of certain instructions is zero and reset to 0 if the result is greater than zero.

e. Parity Bit--Certain operations check the parity of the result. Parity indicates the odd or even status of the l bits in the result. Thus if there is an even number of l bits, the Parity Bit is set to l, and if there is an odd number of l bits, the Parity Bit is set to 0.

L. PROGRAM COUNTER--The Program Counter is a special 16bit register which stores the address of the next program step to be executed. The Program Counter is automatically advanced to the next sequential program address upon completion of a step execution. Sometimes called the P-Counter, the Program Counter is directly accessible to the programmer via machine language instructions which implement JUMP, CALL, and RETURN instructions.

7. STACK POINTER--The Stack Pointer is another special 16-bit register. A section of memory reserved for the temporary storage of data or addresses is called the <u>stack</u>.

Data can be pushed onto the stack for temporary storage and popped out of the stack via several instructions.

The Stack Pointer is used to store the contents of the Program Counter during the execution of subroutines. A RETURN instruction transfers the contents of the Stack Pointer to the Program Counter and sequential execution of the main program continues. The programmer selects the location of the stack in memory by loading the Stack Pointer with the desired memory address via a special instrution (LXI).

The interrelationship of the Working Registers, Program Counter, Stack Pointer, Arithmetic System, Instruction Register, and Timing and Control System should now be more meaningful. The Working Registers incorporate six scratchpad registers and an Accumulator into which numerous operation results are temporarily stored. The Program Counter causes sequential execution of a program by keeping track of the memory address of the next instruction to be executed. The Timing and Control System supplies timing pulses which coordinate orderly program execution. The Stack Pointer is used for temporary storage of the data contained in any register pair. The Stack Pointer also saves the address in the Program Counter for retrieval after a subroutine has been executed. All these operations combine to provide an enormously flexible and versatile CPU. B. MEMORY

Though the Working Registers, Program Counter, and Stack Pointer certainly perform memory roles, the CPU does not contain memory as it is normally defined in a computer application. The primary memory in a computer is external to the CPU.

Simple programs can be implemented with a few dozen words of memory or even less, but more complex applications such as video processing require more memory. The *ALTAIR 8800* is expandable to 65,536 8-bit words of memory.

Access to the memory is always controlled by the CPU.\* 16 address lines called the Address Bus connect the CPU to the Memory. These lines permit the CPU to input or output data to or from any memory address. The addresses are specified by two 8-bit bytes. The CPU processes each address as two sequential (serial) cycles, each containing 8-parallel bits. Data stored in the Memory is exchanged between the Memory and CPU via 8 data lines called the Data Bus. This interconnection format permits parallel operation. Thus, when data is inputted or outputted in or from Memory by the CPU, it is transmitted as a complete 8-bit word.

The basic Memory in the *ALTAIR 8800* contains up to eight 256 x 4 bit random access memories (RAMs). However, any conventional memory can be used in the computer if input loading on the buss does not exceed 50 TTL loads and if the buss is driven by standard TTL loads.

\*An exception to this is when the computer is connected to a Direct Memory Access Controller. DMA takes control of the address and data lines from the CPU for direct transfers of blocks of data. These transfers can take place internally (from one memory location to another) or externally (from memory to an external device).

# C. CLOCK

Orderly execution of a program by the CPU is controlled by a 2-MHz crystal controlled clock. Crystal control is used to permit the clock to operate at the maximum permissible CPU speed. A clock without crystal regulation might occassionally speed up beyond the CPU's capability and program execution errors would result.

#### D. INPUT/OUTPUT

The *ALTAIR 8800* can be interfaced with a great many external devices. Generally, these devices provide input information to the computer and accept output information from the computer. The CPU monitors the status of program execution and Input/Output devices and provides the necessary signals for servicing external devices. The programmer can instruct the CPU to either ignore or respond to interrupt signals provided by an external device. These interrupt signals, when accepted by the CPU, cause the program execution to be temporarily halted while the external device has been serviced, the program resumes normal execution. The *ALTAIR 8800* will service up to 256 Input and 256 Output devices.

This concludes the description of the organization of the *ALTAIR 8800*. The overall operation of the computer as a powerful and efficient data processing system will become more apparent in Part 3, a discussion of the operation of the *ALTAIR 8800*.

### PART 3. OPERATION OF THE ALTAIR 8800

Access to the basic *ALTAIR 8800* is achieved via the front panel, and at first glance the array of 25 toggle switches and 36 indicator and status LEDs may appear confusing. Actually, operation of the *ALTAIR 8800* is very straightforward and most users learn to load a program into the machine and run it in less than an hour. If you are a typical user, you will spend far more time developing and writing programs than actually operating the machine.

This part of the *ALTAIR 8800* Operating Manual explains the purpose and application of the front panel switches and indicator and status LEDs. A sample program is then loaded into the machine and run. A detailed discussion of the role and efficient use of memory is included next. Finally, several operating hints which will help you edit and "debug" programs are included.

#### A. THE FRONT PANEL SWITCHES AND LEDS

Though the front panel contains 25 toggle switches and 36 indicator and status LEDs, most routine operations of the basic *ALTAIR 8800* (256 words of memory) can be performed with only 15 switches and by monitoring only 16 LEDs. The function of all the switches and LEDs is explained below:

ON-OFF Switch--The ON position applies power to the computer. The OFF position cuts off power and also erases the contents of the memory.

STOP-RUN Switch--The STOP position stops program execution. The RUN position implements program execution.

SINGLE STEP Switch--This switch implements a single machine language instruction each time it is actuated. A single machine language instruction may require as many as 5 machine cycles.

EXAMINE-EXAMINE NEXT Switch--The EXAMINE position displays the contents of any specified memory address previously loaded into the DATA/ADDRESS Switches (see below) on the 8 data LEDs. The EXAMINE NEXT position displays the contents of the next sequential memory address. Each time EXAMINE NEXT is actuated, the contents of the next sequential memory address are displayed.

DEPOSIT-DEPOSIT NEXT Switch--The DEPOSIT position causes the data byte loaded into the 8 DATA Switches to be loaded into the memory address which has been previously designated. The DEPOSIT NEXT position loads the data byte loaded into the 8 DATA Switches into the next sequential memory address. Each time DEPOSIT NEXT is actuated, the data byte loaded into the 8 DATA Switches is loaded into the next sequential memory address. The data byte loaded into the 8 DATA Switches can be changed before actuating DEPOSIT or DEPOSIT NEXT.

RESET-CLR Switch--The RESET position sets the Program Counter to the first memory address (0 000 000 000 000 000). RE-SET provides a rapid and efficient way to get back to the first step of a program which begins at the first memory address. CLR is a CLEAR command for external input/output equipment.

PROTECT-UNPROTECT Switch--The PROTECT position prevents memory contents from being changed. The UNPROTECT position

permits the contents of the memory to be altered.

AUX Switches--The basic *ALTAIR 8800* includes two auxiliary switches which are not yet connected to the computer. These switches will be used in conjunction with peripherals add-ed to the basic machine.

DATA/ADDRESS Switches--The DATA Switches are those designated 7-0. The ADDRESS Switches are those designated 15-0. A switch whose toggle is in the UP position denotes a 1 bit. A switch whose toggle is in the DOWN position denotes a 0 bit. In the basic *ALTAIR 8800* (256 word memory), the ADDRESS Switches designated 8-15 are not used and should be set to 0 when an address is being entered.

2. INDICATOR LEDS

(NOTE: When machine is stopped, a glowing LED denotes a l bit or an active status of a specified condition; and a non-glowing LED denotes a 0 bit or inactive status. While running a program, however, LEDs may appear to give erroneous indications.)

ADDRESS--The ADDRESS LEDs are those designated A15-A0. The bit pattern shown on the ADDRESS LEDs denotes the memory address being examined or loaded with data.

DATA--The DATA LEDs are those designated D7-D0. The bit pattern shown on the DATA LEDs denotes the data in the specified memory address.

INTE--An interrupt has been enabled when this LED is glowing.

PROT--The memory is protected when this LED is glowing.

WAIT--The CPU is in a WAIT state when this LED is glowing.

HLDA--A HOLD has been acknowledged when this LED is glowing.

#### 3. STATUS LEDS

(NOTE: A glowing LED denotes an active status for the designated condition.)

LED DEFINITION MEMR The memory bus will be used for memory read data. INP The address bus containing the address of an input device. The input data should be placed on the data bus when the data bus is in the input mode. M1 The CPU is processing the first machine cycle of an instruction. OUT The address contains the address of an output device and the data bus will contain the output data when the CPU is ready. HLTA A HALT instruction has been executed and acknowledged. The address bus holds the Stack Pointer's push-STACK down stack address. WO Operation in the current machine cycle will be a WRITE memory or OUTPUT function. Otherwise. a READ memory or INPUT operation will occur. INT An interrupt request has been acknowledged.

#### B. LOADING A SAMPLE PROGRAM

In Section G of Part 1, a simple addition program in machine language mnemonics is presented. The program is designed to retrieve two numbers from memory, add them together, and store the result in memory. The exact program in mnemonic form can be written thusly:

0. LDA

1. MOV  $(A \rightarrow B)$

2. LDA

3. ADD (A+B)

4. STA

5. JMP

The mnemonics for all 78 of the *ALTAIR 8800* instructions are explained in detail in Part 4 of this manual. For now, the following definitions will suffice:

1. LDA--Load the accumulator with the contents of a specified memory address.

2. MOV  $(A \rightarrow B)$ --Move the contents of the accumulator into register B.

3. ADD (B+A)--Add the contents of register B to the contents of the accumulator and store the result in the accumulator.

4. STA--Store the contents of the accumulator in a specified memory address.

5. JMP--Jump to the first step in the program.\*

\*Once the computer has executed the program it will search its memory for something else to do. To maintain control of the CPU, we can end our sample program with a JMP instruction (followed by the memory address of the first instruction). The computer will "jump" back to the first instruction in the sample program and execute the program over and over again. Notice how precise and specific each of these instructions is. The computer is instructed <u>exactly</u> how to solve the problem and where to place the result. Each of these machine language instructions requires a single byte bit pattern to implement the basic instruction. LDA and STA require two additional bytes to provide the necessary memory addresses.

To load this program into the *ALTAIR 8800*, you must first determine the memory addresses for the two numbers to be added, the result, and the program itself. In most cases, it's more convenient to store a new program by beginning at the first memory address (0). Therefore, the memory addresses for the data (the two numbers to be added and the result) should be placed at any arbitrary addresses higher in memory. Since the basic *ALTAIR 8800* has 256 words of memory, let's select a location for data addresses beginning at memory address 128. The first number to be added will be located at memory address 128 (10 000 000), the second at memory address 129 (10 000 001), and the result at memory address 130 (10 000 010). Now that the memory addresses have been specified, the program can be converted into its machine language bit patterns:

| MNEMONIC     | BIT PATTERN | EXPLANATION                     |

|--------------|-------------|---------------------------------|

| 0. LDA       | 00 111 010  | Load Accumulator with contents  |

|              | 10 000 000  | of: Memory address 128 (2 bytes |

|              | 00 000 000  | required for memory addresses)  |

| 1. MOV (A→B) | 01 000 111  | Move Accumulator to Register B  |

| 2. LDA       | 00 111 010  | Load Accumulator with contents  |

|              | 10 000 001  | of: Memory address 129          |

|              | 00 000 000  |                                 |

| 3. ADD (B+A) | 10 000 000  | Add Register B to Accumulator   |

| MNEMONIC | BIT PATTERN | EXPLANATION                |

|----------|-------------|----------------------------|

| 4. STA   | 00 110 010  | Store Accumulator contents |

|          | 10 000 010  | at: Memory address 130     |

|          | 00 000 000  |                            |

| 5. JMP   | 11 000 011  | Jump to Memory location O. |

|          | 00 000 000  |                            |

|          | 00 000 000  | · ·                        |

Usually the individual bit patterns of a machine language program are sequentially numbered to reduce the chance for error when entering them into the computer. Also, the octal equivalents of each bit pattern are frequently included since it is very easy to load octal numbers into the front panel switches. All that is necessary is to remember the binary / octal equivalents for the decimal numbers 0-7.

The resulting program may appear thusly:

| STEP  | MNEMONIC         | BIT PATTERN | OCTAL EQUIVALENT |

|-------|------------------|-------------|------------------|

|       |                  |             |                  |

| 0.    | LDA              | 00 111 010  | 072              |

| 1. (a | ddress)          | 10 000 000  | 200              |

| 2. (a | ddress)          | 00 000 000  | 0 0 0            |

| 3.    | MOV (A→B)        | 01 000 111  | 107              |

| 4.    | LDA              | 00 111 010  | 072              |

| 5. (a | ddress)          | 10 000 001  | 201              |

| 6. (a | d <b>d</b> ress) | 00 000 000  | 0 0 0            |

| 7.    | ADD (B+A)        | 10 000 000  | 2 0 0            |

| 8.    | ATZ              | 00 110 010  | 062              |

| STEP  | MNEMONIC | BIT PATTERN | <u>OCTAL</u> | EQUIVALENT |

|-------|----------|-------------|--------------|------------|

| 9.(   | address) | 10 000 010  | 2            | 02         |

| 10. ( | address) | 00 000 000  | 0            | 0 0        |

| 11.   | JMP      | 11 000 011  | 3            | 03         |

| 12. ( | address) | 00 000 000  | 0            | 0 0        |

| 13. ( | address) | 00 000 000  | 0            | 0 0        |

The program can now be entered into the computer by means of the front panel switches. To begin loading the program at the first memory address (0), actuate the RESET switch. The Program Counter is now loaded with the first memory address. The program is then entered into the DATA/ADDRESS switches 7-0 one step at a time. After the first step is entered, actuate the DEPOSIT switch to load the bit pattern into the memory. Then enter the second step into the DATA/ADDRESS switches and actuate the DEPOSIT NEXT switch. The bit pattern will be automatically loaded into the next sequential memory address (1). Continue loading the steps into the front panel switches and actuating DEPOSIT NEXT. The complete program loading procedure can be summarized as follows:

| SWITCH           | CONTROL | SWITCHES D-7               | <u>STE</u> P |

|------------------|---------|----------------------------|--------------|

| LOADA Reg.       | RESET   | <b>0 7 2</b><br>00 111 010 | 0            |

|                  | DEPOSIT | r o o                      |              |

| 126 ADDROSS      |         | 10 000 000                 | 1            |

| ر <del>م</del> و | DEPOSIT | 000 000 00                 | 2            |

| NEXT MONE A 3B   | DEPOSIT | • • <b>1</b><br>01 000 111 | 3            |

| <u>STEP</u> | SWITCHES D-7                 | CONTROL SWITCH             |

|-------------|------------------------------|----------------------------|

| 4           | <b>6 7 2</b><br>00 111 010   | DEPOSIT NEXT               |

| 5           | <b>2 0 1</b><br>10 000 001   | DEPOSIT NEXT               |

| 6           | 00 000 000                   | TX3N TI2093D               |

| 7           | <b>2 6 6</b><br>10 000 000   | DEPOSIT NEXT               |

| 8           | <b>6 6 2</b><br>00 110 010   | DEPOSIT NEXT<br>Stoftim A. |

| 9           | <b>2 5 2</b><br>10 000 010   | DEPOSIT NEXT<br>128        |

| 10          | <b>6 6 5</b><br>00 000 000   | DEPOSIT NEXT               |

| 11          | <b>3 6 3</b><br>11 000 011   | DEPOSIT NEXT               |

| 12          | <b>3 0 0 0 0 0 0 0 0 0 0</b> | DEPOSIT NEXT               |

| 13          | <b>) () ()</b><br>00 000 000 | DEPOSIT NEXT               |

|             |                              | DEPOSIT NEXT               |

37

in march

The program is now ready to be run, but first it is necessary to store data at each of the two memory addresses which are to be added together. To load the first address, set the DATA/ADDRESS switches to 10 000 000 and actuate EXAMINE. You can now load any desired number into this address by loading the DATA/ADDRESS switches as appropriate. When the number has been loaded into the switches, actuate DEPOSIT to load it into the memory. To load the next address, enter the second number on the DATA/ADDRESS switches and actuate DEPOSIT NEXT. Since sequential memory addresses were selected, the number will be automatically loaded into the proper address (10 000 001). If non-sequential memory addresses had been selected, the procedure for finding the first address would have to be followed (load the address into the DATA/ADDRESS switches and actuate EXAMINE; then load the number into the DATA/ADDRESS switches and actuate DEPOSIT).

Now that the two memory addresses referenced in the program have been loaded with two numbers to be added together, the program can be run. This is accomplished by simply actuating the RESET switch and then the RUN switch. Wait a moment and then actuate the STOP switch. To see the result stored in memory, actuate the appropriate DATA/ADDRESS switches with the bit pattern for the address into which the result was stored (10 000 010) and then actuate the EXAMINE switch. The result will then be displayed on the DATA LEDs.

To test your ability to load and run this program, try changing the memory addresses for the numbers to be added and the result and then load and run the program again.

# SAMPLE PROGRAM FOR BINARY MULTIPLY

•

| MNEMONIC | ADDRESS           | OCTAL<br>CODE     | EXPLANATION                                          |

|----------|-------------------|-------------------|------------------------------------------------------|

| MVIA     | 000<br>001        | 076<br>002        | Multiplier to A Register                             |

| MVID     | 002<br>003        | 026<br>003        | Multiplicand to D_E Registers                        |

| MVIE     | 004<br>005        | 036<br>000        |                                                      |

| LXIH     | 006<br>007<br>010 | 041               | Clear H,L Registers to initialize<br>Partial Product |

| MVIB     | 011<br>012        | 006<br>010        | Iteration Count to B Register                        |

| DADH     | 013               | 051               | Shift Partial Product left into Carry                |

| RAL      | 014               | 027               | 38a<br>Rotate Multiplier Bit to Carry                |

| JNC      | 015<br>016<br>017 | 322<br>023<br>000 | Test Multiplier at Carry                             |

| DADD     | 020               | 031               | Add Multiplicand to Partial Product<br>if Carry = 1  |

| ACI      | 021<br>022        | 316<br>000        |                                                      |

| DCRB     | 023               | 005               | Decrement Iteration Counter                          |

| JNZ      | 024<br>025<br>026 | 302<br>013<br>000 | Check Iterations                                     |

| SHLD     | 027<br>030<br>031 | 042<br>100<br>000 | Store Answer in Locations 100,101                    |

| JMP      | 032<br>033<br>034 | 303<br>000<br>000 | Restart                                              |

÷

.

# C. USING THE MEMORY

By now it is probably apparent that the memory plays a vital role in the efficient operation of a computer. Higher language compilers generally include a software package which automatically keeps track of the various memory addresses. Machine language operation, however, requires the programmer to keep track of the memory. Otherwise, valuable data or program instructions might be accidentally erased or replaced by other data or instructions.

You can keep track of what is stored in the *ALTAIR 8800*'s memory by means of a simple technique called <u>memory mapping</u>. This technique merely assigns various types of data to certain blocks of memory reserved for a specific purpose. The technique effectively organizes the available memory into an efficient and readily accessible storage medium.

A typical memory map for the *ALTAIR 8800* with 256 words of memory might assign programs to the first 100 words, subroutines to the second 100 words, and data to the remaining 56 words. Of course the various blocks of memory can be modified at will, and the main purpose of memory mapping is to provide a cohesive organization of the available memory.

You can make a memory map each time you change the program in the *ALTAIR 8800*. After the program is written, decide how much memory space should be reserved for the program itself, the subroutines (if any), and the data. Then make a table or chart to record where various items are stored in the memory. Be sure to update the table when the memory organization is modified.

#### D. MEMORY ADDRESSING

The machine language instruction set for the *ALTAIR 8800* provides several methods for addressing the memory. They include direct addressing, register pair addressing, Stack Pointer addressing, immediate addressing, and stack addressing of subroutines. Each of these addressing methods will be described below.

O<sup>1</sup> -1. Direct Addressing--The instruction supplies the specified memory address in the form of two bytes immediately following the actual instruction byte.

2. Register Pair Addressing--The contents of a register pair can contain a memory address. The H and L registers must be used for this purpose in most instructions. The H register contains the most significant 8 bits and the L register the least significant 8 bits (H is high and L is low). Two instructions (STAX and LDAX) permit the B and C or D and E register pairs to contain memory addresses.

3. Stack Pointer Addressing--There are only two stack operations: PUSH and POP. PUSHing data onto the stack causes two bytes (16 bits) of data to be stored in a special block of memory reserved by the programmer and called the stack. POPing data from the stack causes this data to be retrieved. The PUSH and POP instructions are explained in detail in Part 4 of this manual. For now it is important to know that the programmer <u>must</u> reserve the stack location in memory by loading a memory address into the Stack Pointer. This is accomplished by means of the LXI instruction (see Part 4). The programmer should always make note of the stack's address on his memory map.

4. Immediate Addressing--Immediate instructions contain data which is loaded into memory during program loading. Since the data is loaded along with the program in a sequential fashion, it is stored in the block of memory reserved for programming by the operator. There is no need to make any changes to the memory map when loading immediate data.

5. Stack Addressing of Subroutines--When a subroutine is CALLed by a program, the address of the next sequential instruction in the main program is automatically saved by being PUSHed onto the stack. When the subroutine has been executed, a RETURN instruction POPs the address from the stack and the main program continues execution.

#### E. OPERATING HINTS

As you gain experience in the operation of the *ALTAIR 8800*, you will devise methods for improving both the efficiency of your programs and the operation of the computer. Listed below are several helpful hints which you will find quite useful as you learn to operate the machine.

1. Proofreading Programs--To be safe, always proofread a program after it has been entered into the computer. This is done by returning to the first address in memory at which the program begins (actuate RESET if the program begins at memory location 0; otherwise, set the address on the ADDRESS switches and actuate EXAMINE). Check the DATA LEDs to make sure the first program step has been correctly entered. Then actuate EXAMINE NEXT and check the second step against the DATA LEDs. Continue proofreading in this fashion until the entire program has been checked. If an error is found, simply reenter the correct bit pattern on the DATA switches, actuate DEPOSIT, and continue proofreading by means of the EXAMINE NEXT switch.

2. Using NOPs--NOP is an instruction which specifies "No Operation" and is seemingly of little value. However, by scattering NOP instructions throughout a complicated program, considerable time can be saved if a program error requiring the addition of a new step or steps is found. The new instruction or data is simply entered into the program in place of the NOP instruction during the program proofreading. Always be sure to use the appropriate number of NOPs if it is felt a particular new instruction might be necessary. For example, if you think it might be necessary to add an LDA instruction to the program if it fails to execute properly, use 3 NOPs in a row at the required location. Three NOPs are required since the LDA instruction requires three separate bytes.

3. Debugging Programs--Occassionally it will be neccessary to "debug" a program. The need for debugging occurs when a program fails to execute properly because of errors (bugs). Debugging can be enhanced by use of the SINGLE STEP switch. This switch steps the computer through the program in machine cycles rather than complete program steps and permits you to observe the condition of the eight STATUS LEDs. This procedure will permit you to detect illegal entries, improper program organization, and other programming errors.

#### PART 4. ALTAIR 8800 INSTRUCTION SET

The *ALTAIR 8800* has 78 basic machine language instructions. Since many of the instructions can be modified to affect different registers or register pairs, more than 200 variances of the basic instructions are possible.

A detailed description of the *ALTAIR 8800* instruction set is provided in the remainder of this operating manual. For the purpose of this description, the 78 basic machine language instructions have been grouped into seven major subdivisions:

A. Command Instructions

B. Single Register Instructions

C. Register Pair Instructions

D. Accumulator Instructions

E. Data Transfer Instructions

F. Immediate Instructions

G. Branching Instructions

Each instruction is presented as a standardized <u>mnemonic</u> or machine language code. Instructions may occupy from one to three sequential (serial) bytes, and the appropriate bit patterns are included. A condensed summary of the complete instruction set showing the mnemonics and instructions in both binary and octal is included as an Appendix.

#### A. COMMAND INSTRUCTIONS

The ALTAIR 8800 has nine special purpose command instructions which are used to service the remaining instructions. These special purpose instructions occupy four catagories: Input/Output Instructions (IN, OUT), Interrupt Instructions (EI, DI, HLT, RST), Carry Bit Instructions (STC, CMC), and the No Operation Instruction (NOP).

#

There are two Input/Output Instructions and each occupies two bytes. The first byte is the instruction, and the second byte is the Input/Output device number.

| IN | (INPUT) | 11 011 011 | (Byte 1) |

|----|---------|------------|----------|

|    |         |            |          |

(Device No.) (Byte 2)

Operation: An 8-bit data byte is loaded from the specified external device into the Accumulator.

Status Bits: Unaffected.

Example: Assume an input device contains the following data byte: 00 001 000. Implementation of the IN instruction (including device number) will cause the data byte to replace the contents of the Accumulator.

| OUT (OUTPUT) | 11 010 011 | (Byte 1) |

|--------------|------------|----------|

|--------------|------------|----------|

(Device No.) (Byte 2)

Operation: An 8-bit data byte is loaded from the Accumulator into the specified output device.

Status Bits: Unaffected.

Example: Assume the Accumulator contains the following data byte: 00 001 000. Implementation of the OUT instruction (plus device number) will cause the data byte to be sent to the specified external device.

43

# 2. INTERRUPT INSTRUCTIONS

There are two specific Interrupt instructions (EI and DI) and two auxiliary Interrupt instructions. Interrupt instructions permit implementation of a program by a computer to be temporarily interrupted so that input/output interfacing may take place. For example, <u>interrupts may be</u> <u>utilized by a computer's output device while an input device</u> is entering data or a program.

EI (ENABLE INTERRUPTS) 11 111 011 (Byte 1)

Operation: Implementation of the EI instruction sets the interrupt flip-flop. This alerts the computer to the presence of interrupts and causes it to respond accordingly.

Status Bits: Unaffected.

DI (DISABLE INTERRUPTS) 11 110 011 (Byte 1)

Operation: Implementation of the DI instruction resets the interrupt flip-flop. This causes the computer to ignore any subsequent interrupt signals.

Status Bits: Unaffected.

#### HLT (HALT INSTRUCTION) 01 110 110 (Byte 1)

Operation: Implementation of the HLT instruction steps the Program Counter to the next instruction address and stops the computer until an interrupt occurs. The HLT instruction should not normally be implemented when a DI instruction has been executed. Since the DI instruction causes the computer to ignore interrupts, the computer will not operate again until the main power switch is turned off and then back on.

Status Bits: Unaffected.

RST (RESTART INSTRUCTION) 11 (esp) 111 (Byte 1)

Operation: The data byte in the Program Counter is pushed onto the stack. This provides an address for subsequent use by a RETURN instruction. Program execution then continues at memory address: 00 000 000 00 (exp) 000 where exp ranges from 000 to 111.

The RST instruction is normally used to service interrupts. The external device may cause a RST instruction to be executed during an interrupt. Implementation of RST then calls a special purpose subroutine which is stored in up to eight 8-bit bytes in the lower 64 words of memory. A RETURN instruction is included to return the computer to the original program.

Status Bits: Unaffected.

Example: Assume the following RST instruction is present: 11 001 111. Implementation of the instruction will cause the Program Counter data byte to be pushed onto the stack. The program will then continue execution at the subroutine located at memory address: 00 000 000 00 001 000. Upon completion of the subroutine, a RETURN instruction will return the computer to the next step in the main program.

3. CARRY BIT INSTRUCTIONS

There are two instructions which can be used to directly modify the status of the Carry Bit. Each instruction requires one 8-bit byte.

CMC (COMPLEMENT CARRY) 00 111 111 (Byte 1)

Operation: The Carry Bit is complemented. If it is initially 0, it is set to 1. If it is initially 1, it is reset to 0.

Status Bit Affected: Carry.

STC (SET CARRY) 00 110 111 (Byte 1)

Operation: The Carry Bit is set to 1.

Status Bit Affected: Carry.

4. NO OPERATION INSTRUCTION

3.18

There is one NO OPERATION instruction. It occupies a single 8-bit byte.

NOP (NO OPERATION) 00 000 000 (Byte 1) Operation: No operation occurs, and the Program Counter e de la composition d

proceeds to the next sequential instruction. Program execution then continues.

Status Bits: Unaffected.

#### **B. SINGLE REGISTER INSTRUCTIONS**

or

The *ALTAIR 8800* has four single register instructions. Each instruction occupies a single byte. Two of the instructions, INR and DCR, have eight variances each. The variances are specified according to any desired register, and the following register bit patterns apply:

| Register           | Bit Pattern |

|--------------------|-------------|

| В                  | 000         |

| C                  | 001         |

| D                  | 010         |

| E                  | 011         |

| H many With        | 100         |

| L Nenny Low        | 101         |

| Memory Reference M | 110         |

| A                  | 111         |

If Memory Reference M <u>(110</u>) is specified in the instruction byte, the memory byte addressed by the contents of the H and L registers is processed. The H register contains the most significant 8 bits of the memory address and the L register contains the least significant 8 bits of the

address.

INR (INCREMENT REGISTER OR MEMORY) 00 (reg) 100 (Byte 1)

Operation: The specified byte is incremented by one.

Status Bits Affected: Zero, Sign, Parity, and Auxiliary Carry.

Example: Assume the following instruction is present: 00 000 100. According to the table of register bit patterns given above, the byte in register B is to be incremented by 1. If the initial byte is 00 000 000, the incremented byte will be 00 000 001.

DCR (DECREMENT REGISTER OR MEMORY) 00 (reg) 101 (Byte 1)

Operation: The specified byte is decremented by one.

Status Bits Affected: Zero, Sign, Parity, and Auxiliary Carry.

Example: Assume the following instruction is present: 00 001 101. According to the table of register bit patterns given above, the byte in register C is to be decremented by 1. If the initial byte is 00 000 001, the decremented byte will be 00 000 000.

CMA (COMPLEMENT ACCUMULATOR) 00 101 111 (Byte 1)

Operation: Each bit in the accumulator is complemented (1s become Os and Os become 1s).

Status Bits: Unaffected.

Example: Assume the accumulator byte is 11 001 100. The instruction CMA will complement each bit in the accumula-tor byte as shown below:

11 001 100 Accumulator

00 110 011 Complemented Accumulator

DAA (DECIMAL ADJUST ACCUMULATOR) 00 100 111 (Byte 1)

Operation: The 8-bit accumulator byte is converted into two 4-bit BCD (binary-coded-decimal) numbers. The instruction affected by the Auxiliary Carry Bit.

The DAA instruction performs two operations:

1. If the least significant 4 bits in the accumulator byte (bits 0-3) represent a BCD digit greater than 9 or if the Auxiliary Carry Bit is set to 1, the four bits are automatically incremented by 6. If not, the accumulator is unaffected.

2. If the most significant 4 bits in the accumulator byte (bits 4-7) represent a BCD digit greater than 9 or if the Carry Bit is set to 1 after the previous operation, the four bits are automatically incremented by 6. If not, the accumulator is unaffected.

Status Bits Affected: Zero, Sign, Parity, Carry, and Auxiliary Carry.

Example: Assume the accumulator byte is 10 100 100. The DAA instruction will automatically consider the byte as two 4-bit bytes: 1010 0100. Since the value of the least significant 4 bits is less than 9, the accumulator is initially unaffected. The value of the most significant 4 bits is greater than 9, however, so the 4 bits are incremented by 6 to give 1 0000. The most significant bit sets the Carry Bit to 1, and the accumulator now contains: 00 000 100.

# C. REGISTER PAIR INSTRUCTIONS

The *ALTAIR 8800* has eight register pair instructions. Each instruction occupies a single byte. Five of the instructions, PUSH, POP, DAD, INX, and DCX, have four variances each. The variances are specified according to any desired register pair, and the following register pair bit patterns apply:

| Register Pair | Bit Pattern |

|---------------|-------------|

| B and C       | 00          |

| D and E       | 01          |

| H and L       | 10          |

| Flags and A   | 11          |

|               |             |

PUSH (PUSH DATA ONTO STACK)

11 (rp)0 101 (Byte 1)

Operation: The contents of the specified register pair (rp) are stored in two bytes of memory at an address indicated by the Stack Pointer. The contents of the first register are PUSHed into the address one less than the address in the Stack Pointer. The contents of the second register are PUSHed into the address two less than the address in the Stack Pointer.

If the Status Bit Register and Accumulator (register pair PSW) pair is specified, the first byte PUSHed into memory is the Status Bit Register. This byte has the following format:

| Bit Position | Contents                     |

|--------------|------------------------------|

| 7            | Sign Bit                     |

| 6            | Zero Bit                     |

| 5            | 0                            |

| 4            | Auxiliary Car <b>r</b> y Bit |

| 3            | C                            |

| 2            | Parity Bit                   |

| 1            | 1                            |

Bit Position

#### Contents

0

# Carry Bit

For example, if the Carry Bit is set to 1 and all remaining status bits are reset to 0, the Status Bit Register will contain the following byte: 00 000 011.

After the PUSH instruction is implemented, the Stack Pointer is automatically decremented by two.

Status Bits: Unaffected.

Example: Assume PUSH BC is implemented. The instruction byte will have the following format: 11 000 101. The contents of register pair BC will be stored in memory thusly: B will be stored at the address in the Stack Pointer less one; C will be stored at the address in the Stack Pointer less two. The Stack Pointer will then be decremented by two.

POP (POP DATA OFF STACK)

11 (rp)0 001 (Byte 1)

Operation: The contents of the specified register pair (rp) are retrieved from the two bytes of memory at an address indicated by the Stack Pointer. The contents of the memory byte at the Stack Pointer address are loaded into the second register of the pair, and the contents of the byte at the Stack Pointer address plus one are loaded into the first register of the pair.

If the Status Bit Register and Accumulator (register pair PSW) pair is specified, the contents of the byte at the Stack Pointer address plus one are used to set or reset the status bits according to the format provided in the description of the PUSH instruction.

After the POP instruction is implemented, the Stack Pointer is automatically incremented by two.

Status Bits Affected: None unless register pair PSW is specified.

Example: The inverse of the example provided under the PUSH instruction will illustrate operation of the POP instruction.

DAD (DOUBLE ADD)

Operation: The 16-bit number formed by the two bytes in the specified register pair (rp) is added to the 16-bit number formed by the two bytes in the H and L registers. The result is stored in the H and L register pair.

Status Bits Affected: Carry.

Example: Assume the 16-bit number formed by the two bytes in register pair BC is 00 101 111 01 111 111. Assume the contents of the H and L register pair form the 16-bit number 01 100 000 00 100 101. The instruction DAD BC (00 001 001) will add the two numbers and store the result in the H and L register pair. The result of the addition is: 10 001 111 10 100 100. Since no carry occurred, the Carry Bit is reset to 0.

INX (INCREMENT REGISTER PAIR)

00 (rp)0 011 (Byte 1)

Operation: The 16-bit number formed by the two bytes in the specified register pair (rp) is incremented by one.

Status Bits: Unaffected.

52

Example: Assume the INX instruction 00 100 011 is present. According to the table of register pair bit patterns, the 16-bit number formed by the two bytes in the H and L register pair will be incremented by one. If the initial 16bit number is 10 001 111 10 100 100, the new 16-bit number will be 10 001 111 10 100 101.

DCX (DECREMENT REGISTER PAIR) 00 (rp)1 011 (Byte 1)

Operation: The 16-bit number formed by the two bytes in the specified register pair is decremented by one.

Status Bits: Unaffected.

Example: Assume the DCX instruction 00 101 011 is present. According to the table of register pair bit patterns, the 16-bit number formed by the two bytes in the H and L register pair will be decremented by one. If the initial 16-bit number is 10 001 111 10 100 101, the new 16-bit number will be 10 001 111 10 100 100.

# XCHG (EXCHANGE REGISTERS)

11 101 011 (Byte 1)

53

Operation: The 16-bit number formed by the contents of the H and L registers is exchanged with the 16-bit number formed by the contents of the D and E registers.

Status Bits: Unaffected.

Example: Assume the H register byte is 10 001 111 and the L register byte is 10 000 011. Assume the D and E register bytes are both 60 000 000. Implementation of the XCHG instruction will exchange the contents of the two register pairs so that the H and L register bytes are both 00 000 000 and the D and E register bytes are, respectively, 10 001 111 and 10 000 011.

XTHL (EXCHANGE STACK) 11 100 011 (Byte 1)

Operation: The byte stored in the L register is exchanged with the memory byte addressed by the Stack Pointer. The byte stored in the H register is exchanged with the memory byte at the address one greater than that addressed by the Stack Pointer.

Status Bits: Unaffected.

Example: The example provided under the XCHG instruction is similar to the operation which occurs when the XTHL instruction is implemented.

SPHL (LOAD SP FROM H AND L) 11 111 001 (Byte 1)

Operation: The 16-bit contents of the H and L registers replace the contents of the Stack Pointer without affecting the contents of the H and L registers.

Example: Assume the H register byte is 10 001 111 and the L register byte is 10 000 011. Assume the Stack Pointer address is 00 001 100 01 111 111. Implementation of the SPHL instruction will load the Stack Pointer with: 10 001 111 10 000 011. The contents of the H and L registers will remain unchanged.

D. ROTATE ACCUMULATOR INSTRUCTIONS

This is a special set of four instructions which apply only to the *ALTAIR 8800*'s accumulator. Only one byte of instruction is required, and no memory or register variances apply.

RLCR 07

RLC (ROTATE ACCUMULATOR LEFT) 00 000 111 (Byte 1)

Operation: The accumulator byte is rotated one bit position to the left. The 7 bit position now occupies the 0 bit position and the Carry Bit is set with the value of the 7 bit before rotation.

Status Bits Affected: Carry.

Example: Assume the accumulator byte is 10 001 000 and the RLC instruction is present. The Carry Bit is set to equal the value of the accumulator byte's 7 bit (1), and the contents of the accumulator are rotated one bit position to the left. The 7 bit now occupies the 0 bit: 00 010 001.

RRC (ROTATE ACCUMULATOR RIGHT) 00 001 111 (Byte 1)

Operation: The accumulator byte is rotated one bit position to the right. The O bit position now occupies the 7 bit position and the Carry Bit is set with the value of the O bit before rotation.

Status Bits Affected: Carry.

Example: Assume the accumulator byte is 10 001 000 and the RRC instruction is present. The Carry Bit is set equal to the value of the accumulator byte's 0 bit (0), and the contents of the accumulator are rotated one bit position to the right. The 0 bit now occupies the 7 bit: 01 000 100.

REAR IT RAL (ROTATE ACCUMULATOR LEFT THROUGH CARRY) 00 010 111

Operation: The accumulator byte is rotated one bit position to the left through the Carry Bit. The 7 bit position then occupies the Carry Bit and the Carry Bit occupies the 0 bit position.

Status Bits Affected: Carry.

Example: Assume the accumulator byte is 10 001 000, the Carry Bit is 1, and the RAL instruction is present. The contents of the accumulator are rotated one bit left through

the Carry Bit. The 7 bit now occupies the Carry Bit (1) and the Carry Bit now occupies the 0 bit: 00 010 001.

# RRA IF RAR (ROTATE ACCUMULATOR RIGHT THROUGH CARRY) 00 011 111

Operation: The accumulator byte is rotated one bit position to the right through the Carry Bit. The O bit position now occupies the Carry Bit and the Carry Bit occupies the 7 bit position.

Status Bits Affected: Carry.

Example: Assume the accumulator byte is 10 001 000, the Carry Bit is 1, and the RAR instruction is present. The contents of the accumulator are rotated one bit position right through the Carry Bit. The 0 bit now occupies the Carry Bit, and the Carry Bit now occupies the 7 bit: 11 000 100.

55

#### E. DATA TRANSFER INSTRUCTIONS

Data can be conveniently transferred between registers or between the memory and registers of the *ALTAIR 8800*. Certain of these operations are direct data transfers and no other operation is involved. For example, the MOV instruction causes a byte of data to be transferred from one register (the <u>source register</u>) to another register (the <u>destination register</u>). Other data transfers are accompanied by an arithmetic or logical operation. For example, the ADD instruction adds the contents of a specified register to the contents of the accumulator.

Still another class of data transfer instructions concerns only the accumulator and the H and L register pair. For example, the STA instruction causes the contents of the accumulator to replace the byte of data stored at a specified memory address.

This section describes fifteen separate data transfer instructions, but it is important to note that many other instructions also involve the transfer of data (e.g. PUSH, POP, DAD, XCHG, XTHL, SPHL, etc.). However, it is more appropriate to the efficient organization of this operating manual to describe these instructions elsewhere.

The data transfer instructions described in this section are grouped into three subdivisions. The first subdivision is Data Transfers (MOV, STAX, and LDAX). The second is Register/Memory to Accumulator Transfers (ADD, ADC, SUB, SBB, ANA, XRA, ORA, and CMP). And the third is Direct Addressing Transfers (STA, LDA, SHLD, and LHLD).

### 1. DATA TRANSFER INSTRUCTIONS

There are three data transfer instructions and each is unconditional. Each of the three instructions has at least two variances. The variances are determined by register or memory addresses which are specified by the programmer.

MOV (MOVE DATA)

01 DDD SSS (Byte 1)

Operation: The contents of SSS (the source register) are moved to DDD (the destination register). The contents of SSS remain unchanged. The following bit patterns for the source and destination registers apply:

| Register           | Bit Pattern |

|--------------------|-------------|

| В                  | 000         |

| C                  | 001         |

| D                  | 010         |

| E                  | 011         |

| Н                  | 100         |

| L                  | 101         |

| Memory Reference M | 110         |

| A                  | 111         |

The source and destination registers cannot both equal 110.

Status Bits: Unaffected.

Example: Assume it is necessary to transfer the contents of register E to the accumulator. By referring to the register bit pattern table provided above, an appropriate MOV instruction can be formulated: 01 111 011.

STAX (STORE ACCUMULATOR) 00 0X0 010 (Byte 1)

Operation: The contents of the accumulator are stored in a memory address specified by registers B and C or registers D and E. Registers B and C are specified by a O at the 4 bit position (X). Registers D and E are specified by a 1 at the 4 bit position (X).

Status Bits: Unaffected.

Example: Assume it is necessary to store the contents of the accumulator at a memory address specified by registers D and E. The appropriate STAX instruction is: 00 010 010.

LDAX (LOAD ACCUMULATOR) 00 0X1 010 (Byte 1)

Operation: The contents of the memory address specified by registers B and C or by registers D and E replace the contents of the accumulator. Registers B and C are specified by a O at the 4 bit position (X). Registers D and E are specified by a 1 at the 4 bit position (X).

57

واحار اليوريان بالمتحاد بالمتحا المعطفهم

# Status Bits: Unaffected.

Example: Assume it is necessary to load the accumulator with the contents of a memory address specified by registers B and C. The appropriate LDAX instruction is: 00 001 010.

# 2. REGISTER/MEMORY TO ACCUMULATOR TRANSFERS

There are eight Register/Memory to Accumulator Transfers and each is unconditional. Each of the eight instructions has eight variances determined by registers specified by the programmer. The following bit patterns for each of the registers apply:

| Register         | Bit Pattern |

|------------------|-------------|

| В                | 000         |

| С                | 001         |

| D                | 010         |

| Е                | 011         |

| H .              | 100         |

| L                | 101         |

| Memory Address M | 110         |

| A                | 111         |

Four of the instructions involve arithmetic (add or subtract) operations. The remaining four involve logical operations.

ADD (ADD REGISTER/ACCUMULATOR TO MEMORY) 10 000(reg) (Byte 1)

Operation: The contents of the specified register (reg) are added to the contents of the accumulator.

Status Bits Affected: Carry, Sign, Zero, Parity, and Auxiliary Carry.

Example: Assume it is necessary to add the contents of register B to the accumulator. Referring to the register bit pattern table given above, the appropriate instruction

is: 10 000 000. If the data bytes at register B and the accumulator are 11 010 100 and 01 100 010 respectively, the following addition will be performed:

Since the new accumulator byte has nine bits, the Carry Bit will be set to 1 to indicate a carry has occurred.

ADC (ADD REGISTER/MEMORY AND CARRY TO ACCUMULATOR) 10 001 (reg)

Operation: The contents of the specified register (reg) and the content of the Carry Bit are added to the accumulator.

Status Bits Affected: Carry, Sign, Zero, Parity, and Auxiliary Carry.

Example: Assume it is necessary to add the contents of register C and the content of the Carry Bit to the accumulator. Referring to the register bit pattern table given above, the appropriate instruction is: 10 001 001. If the data bytes at register C and the accumulator are 00 100 011 and 01 011 100 and the Carry Bit is 1, the following addition will be performed:

| 00 100 011 | Register C Byte      |

|------------|----------------------|

| 01 011 100 | Accumulator Byte     |

| 1          | Carry Bit            |

|            |                      |

| 10 000 000 | New Accumulator Byte |

If the new accumulator byte had nine bits, the extra bit would set the Carry Bit to 1.

SUB (SUBTRACT REGISTER/MEMORY FROM ACCUMULATOR) 10 010 (reg)

Operation: The contents of the specified register are subtracted from the contents of the accumulator. The *ALTAIR* 8800 achieves subtraction by means of a simple addition process called two's complement arithmetic. If there are only

eight bits in the result, no carry bit is present. This means a borrow occurred, and the Carry Bit is set to 1. Note that this operation is the inverse of what occurs in an ADD instruction.

Status Bits Affected: Carry Sign, Zero, Parity, and Auxiliary Carry.

Example: Assume it is necessary to clear the accumulator of its contents. An efficient way to achieve this requirement is to implement a SUB A instruction (10 010 111) where A specifies the accumulator variance of the SUB instruction. Implementation of this instruction will cause the contents of the accumulator to be subtracted from itself.

SBB (SUBTRACT REGISTER/MEMORY FROM ACCUMULATOR WITH BORROW)

10 011 (reg) (Byte 1)