**IBM**

Large Systems Technical Support Technical Bulletin

IBM 3090 Processor Complex: Planning and Installation Reference

D. D. Boos B. E. Kasch

National Technical Support Washington Systems Center

**GG66-3090-01 November 1987**

LZB

Washington Systems Center Gaithersburg, MD Technical Bulletin

IBM 3090 Processor Complex: Planning and Installation Reference

D. D. Boos B. E. Kasch The information contained in this document has not been submitted to any formal IBM test and is distributed on an "as is" basis without any warranty either expressed or implied. The use of this information or the implementation of any of these techniques is a customer responsibility and depends on the customer's ability to evaluate and integrate them into the customer's operational environment. While each item may have been reviewed by IBM for accuracy in a specific situation, there is no guarantee that the same or similar results will be obtained elsewhere. Customers attempting to adapt these techniques to their own environments do so at their own risk.

Reference to PTF numbers that have not been released through the PUT process does not imply general availability. The purpose of including these reference numbers is to alert IBM CPU customers to specific information relative to the implementation of the PTF when it becomes available to each customer according to the normal IBM PTF distribution rules.

Performance data contained in this document was determined in a controlled environment; and therefore, the results which may be obtained in other operating environments may vary significantly. Users of this document should verify the applicable data for their specific environment.

In this document, any references made to an IBM licensed program are not intended to state or imply that only IBM's licensed program may be used; any functionally equivalent program may be used instead.

It is possible that this material may contain reference to, or information about, IBM products (machines and programs), programming, or services that are not announced in your country. Such references or information must not be construed to mean that IBM intends to announce such IBM products, programming, or services in your country.

Publications are not stocked at the address given below; requests for IBM publications should be made to your IBM representative or to the IBM branch office serving your locality.

A form for reader's comments is provided at the back of this publication. If the form has been removed, comments may be addressed to: Washington Systems Center, 18100 Frederick Pike, Gaithersburg, MD 20879.

IBM may use or distribute any of the information you supply in any way it believes appropriate without incurring any obligation whatever. You may, of course, continue to use the information you supply.

### **Abstract**

This Technical Bulletin contains information pertinent to the IBM 3090 family of processors. It is intended for IBM and Customer personnel who have planning responsibilities for the installation of any of these processors.

The overall design of this document is to provide information about each of the processors and the operating systems and major products that support these processors.

This document is structured into seven major chapters: Family Comparisons, Logical Components, Software Considerations, Installation Topics, Partitioning Topics, Virtual Storage Considerations and Bibliography.

A brief description of each chapter follows:

- 1. Family Comparisons This chapter contains a single page on each of the processors in the IBM 3090 family listing the standard and optional features of each. Also included are comparison summaries of the various models.

- 2. Logical Components This chapter focuses on the logical components of the IBM 3090 processor family. A description of each of these components and how they are implemented in each member of the IBM 3090 processor family is provided. The unique implementations include: uniprocessor (120E, 150, 150E, 180, 180E), two-way (dyadic) processor (200, 200E), three-way (triadic) processor (300E), four-way processor (400, 400E), and six-way processor (600E).

- 3. Software Considerations This chapter contains an overview of the supporting software for the 3090 family. It describes the changes incorporated into MVS/XA 2.1.3, MVS/XA 2.1.7, MVS/XA 2.2.0, MVS/370 1.3.5, VM/XA Systems Facility, VM/High Performance Option, VM/XA System Product, and the major supporting products (JES, EREP, IOCP, and RMF).

- 4. Installation Topics This chapter focuses on the major installation considerations that are pertinent to all models of the IBM 3090 family.

- 5. Partitioning Topics This chapter contains considerations that are primarily applicable to the "partitionable" processors in the 3090 family. These are the Models 400, 400E, and 600E.

- 6. Virtual Storage Assessment This chapter provides considerations for the use of virtual storage, why it is important not to run out, some recommendations for the current use of virtual storage, a list of IBM products that provide Virtual Storage Constraint Relief (VSCR), and the highlights of the amount of relief expected from some of these products.

- 7. Bibliography This chapter contains a bibliography for the 3090 family of processors. There is a description of each document that should assist the reader in choosing which documents should be used for specific points of reference.

## **Preface**

The primary intent of this document is to serve as a composite source of planning and installation reference material for IBM 3090 Processors. The document does not obsolete previously available Systems Center technical bulletins on 3090 processors. Information contained in this document consists of original material and material obtained from other sources, including technical bulletins, flashes, and standard IBM publications.

The approach taken by the authors in the preparation of this document was to provide a handy reference for 3090 processor planning and installation information that would suffice for most situations. If additional detail on a particular topic is required, then existing Systems Center technical bulletins and standard IBM publications should be used. A list of such documents is provided in Chapter 7, Bibliography.

## **Summary of Amendments**

This edition contains additional information, since the April 1987 version, about the IBM 3090 family of processors. These additions fall into the following categories:

- New 3090 Models and features:

- 3090 Model 120E

- Additional Expanded Storage on Models 200E, 300E, 400E, and 600E

- 4.5Mb/sec Block Channel Support for all 3090 models

- The Multiple High Performance Guests Support Feature on all E-models

- New Software Support:

- VM/SP System Product Releases 1 and 2

- MVS/SP 2.2.0 VIO support for Expanded Storage

- IOCP support for additional channels and 4.5Mb/sec channel support

- SEC 223630 Contents:

- Function and Features

- Operational Enhancements and Changes

- Miscellanous changes:

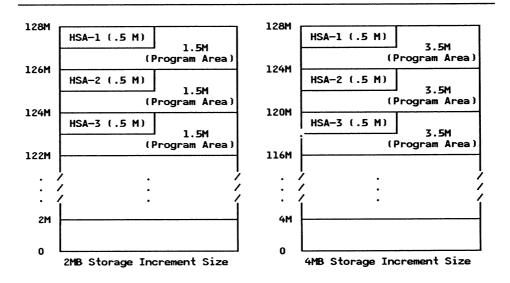

- HSA Expansion

- Increased Extended SQA Requirements

- Setting Machine Check Thresholds for Storage Errors

- Procedures for attaching 3480 to Processor Controller (PCE)

- Steps required to enable 4.5Mb/sec channel support

- Partitioning the 3090 with an MSS attached

- Additions to the Bibliography:

- Technical Bulletins

- Operations Guides

- Recovery Guides

- Educational Offerings

# **Contents**

| Chapter 1. IBM 3090 Family Comparisons 1 |

|------------------------------------------|

| Model 150 1                              |

| Model 180 2                              |

| Model 200 3                              |

| Model 400 4                              |

| Model 120E 5                             |

| Model 150E 6                             |

| Model 180E 7                             |

| Model 200E 8                             |

| Model 300E 9                             |

| Model 400E                               |

| Model 600E                               |

| Comparison Summaries                     |

|                                          |

| Chapter 2. IBM 3090 Logical Components   |

| Logical Components                       |

| Central Processors                       |

| Instruction Element                      |

| Execution Element                        |

| Buffer Control Element                   |

| Vector Facilities                        |

| Multiple High Performance Guests Support |

| System Control Element                   |

| Processor Storage                        |

| Central Storage                          |

| Expanded Storage                         |

| Channels 23                              |

| Status-Verification Facility             |

| Processor Controller                     |

| PCE Attached Devices                     |

| PCE Operating States - Single Image      |

| PCE Operating States - Partitioned       |

| Remote Support Facility                  |

| Problem Analysis 30                      |

| Service Update 30                        |

| System Status Recording                  |

| Single Points of Failure 3               |

| Logical Components Summary               |

| _                                        |

| Chapter 3. Software Considerations 3.    |

| MVS/XA Support 3                         |

| MVS/SP 2.1.3 3                           |

| Overview                                 |

| Expanded Storage Support                 |

| Operator Command Changes 3               |

| Frame Deallocation                       |

| Dispatcher Enhancement 4                 |

| Available Frame Queue Management         |

| Spin-Loop Recording 4                    |

| SMF Changes 4                            |

| RMF 3.3                                        | 45 |

|------------------------------------------------|----|

| MVS/SP 2.1.3 VFE (Vector Facility Enhancement) |    |

| MVS/SP 2.1.7                                   |    |

| Compatibility                                  |    |

|                                                |    |

| Dispatcher Change                              | 57 |

| Supporting Products                            | 58 |

| MVS/XA DFP                                     | 58 |

| JES2                                           | 58 |

| JES3                                           |    |

| IOCP                                           |    |

| EREP                                           | 59 |

| RMF 3.4.1                                      | 59 |

| Miscellaneous                                  | 60 |

| MVS/SP 2.2.0                                   |    |

| VIO to Expanded Storage                        |    |

| MVS/370 Support                                |    |

| Overview                                       |    |

| Frame Deallocation                             |    |

| Expanded Storage                               |    |

| Vector Facility                                |    |

|                                                |    |

| VM Support                                     |    |

| VM/XA Systems Facility                         |    |

| Basic Processor Support                        |    |

| Expanded Storage Support                       | 67 |

| Virtual Extended Channel Support               | 67 |

| Vector Facility Support                        | 67 |

| VM/XA System Product                           | 68 |

| VM/XA System Product Release 1                 | 68 |

| VM/XA System Product R1 Enhancement            | 71 |

| VM/XA System Product Release 2                 | 73 |

| VM/SP High Performance Option                  | 74 |

| Basic Processor Support                        | 74 |

| Extended Channel Support                       | 74 |

| Expanded Storage Support                       | 75 |

| System Generation of Expanded Storage          | 76 |

| Other Changes for Expanded Storage             |    |

| Vector Facility Support                        | 77 |

| ,,,,,,,,,,,,,,,,,,,                            |    |

| Chapter 4. Installation Topics                 | 79 |

| IOCP Support                                   | 79 |

| I/O Configuration Datasets                     | 80 |

| Active IOCDS Dataset Considerations            | 81 |

| IOCP Macros                                    | 82 |

| 3090/308X IOCP Compatibility                   |    |

| Combined SVSCEN/IOCD Input Street              | 83 |

| Combined SYSGEN/IOCP Input Stream              | 84 |

| I/O Configuration                              | 85 |

| Considerations for Single-Image Operation      | 86 |

| Console Considerations                         | 88 |

| Miscellaneous Topics                           | 89 |

| DCCF System Console Support                    |    |

| Processor Identification                       |    |

| TOD Clock Setting                              | 91 |

| 3180 Model 140/145 Setup Consideration         | 91 |

| HSA Expansion                                           | 92         |

|---------------------------------------------------------|------------|

| Increased Extended SQA (ESQA) Requirement               | 93         |

| Potential Real Storage Usage Increase                   | 93         |

| Error Recovery Enhancements                             | 94         |

| Setting Machine Check Threshholds for Storage Errors    | 96         |

| SEC 223620                                              | 97         |

| Operational Enhancements/Changes                        | 97         |

| Support for 3480 Attachment to the Processor Controller | 98         |

| 5DC 225050                                              | 100        |

| Talletion/Teatare Support                               | 100<br>101 |

| Operational Educations of Charles                       | 101        |

| 1.51vio/500 Biook Charmer Support                       | 102        |

| Tareware rivationity                                    | 102        |

| 4.5Mb Channel Configuration Guidelines                  | 103        |

| Reduced Diameter Channel (Blue) Cables                  | 103        |

| Interfaces and Switches                                 | 104        |

| Software Requirements                                   | 104        |

| PCE Stall Detect                                        | 105        |

| Functions Not Available                                 | 106        |

| Considerations after a PCE Stall                        | 107        |

|                                                         |            |

| Chapter 5. Partitioning Topics                          | 109        |

| Partitioning Considerations                             | 109        |

| Channel Paths                                           | 111        |

| Processors                                              | 111        |

| Processor Storage                                       | 111        |

| Specifying the RSU Parameter                            | 112        |

| Operational Considerations                              | 114        |

| Program Properties Table                                | 115<br>116 |

| DFHSM (Data Facility Hierarchical Storage Manager)      | 117        |

| Partitioning the 3090 with an MSS Attached              | 118        |

| MSS EC Requirements (MVS/XA Operation)                  | 118        |

| WISS EC Requirements (WVS/AA Operation)                 | 110        |

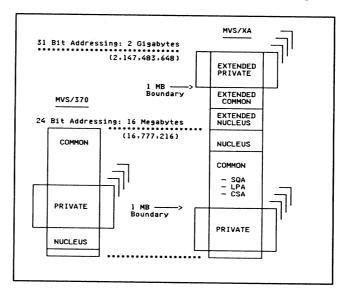

| Chapter 6. Virtual Storage Assessment                   | 119        |

| Virtual Storage Review                                  | 119        |

| Virtual Storage Considerations                          | 120        |

| Some Products Providing VSCR                            | 122        |

| Some Product Highlights (MVS/XA Systems)                | 123        |

|                                                         |            |

| Chapter 7. Bibliography                                 | 125        |

| Related Reference Materials                             | 125        |

| IBM 3090 Processor Complex Documentation:               | 125        |

| Technical Bulletins:                                    | 126        |

| Operations:                                             | 128        |

| Recovery:                                               | 129        |

| Related Education Offerings:                            | 129        |

| Automatic Distribution of Technical Bulletins           | 133        |

| •                                                       | 135        |

# **Figures**

| 1.       | Standard and Optional Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ) |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| 2.       | Miscellaneous Hardware Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | , |

| 2.<br>3. | Modes of Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |

|          | System Control Program Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |

| 4.       | System Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |

| 5.       | Bystem requiremes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |

| 6.       | Woder Opprace raths (ripproximate time in system)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |

| 7.       | Table hayout of I am I carated I location of the life of the land |   |

| 8.       | William Required Faines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | • |

| 9.       | Options Requiring Additional Frames                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |

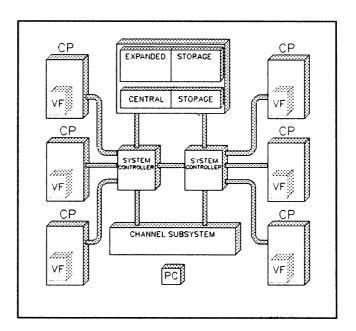

| 10.      | Logical Components of IBM 3090 Model 600E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |

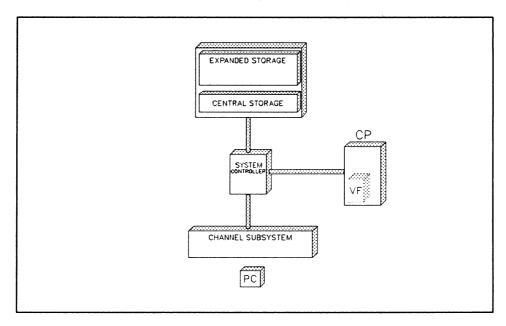

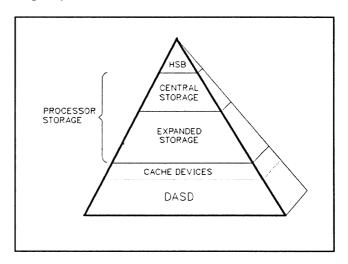

| 11.      | Storage Hierarchy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |

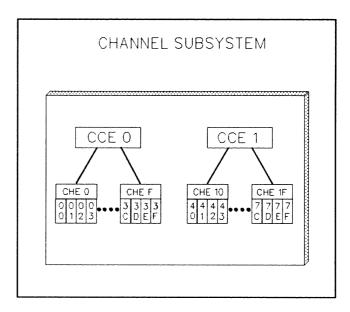

| 12.      | Channel Subsystem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3 |

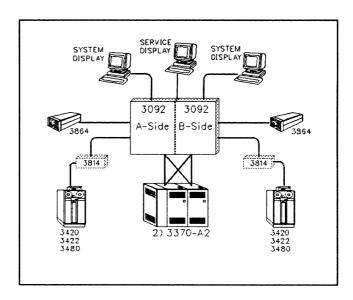

| 13.      | Processor controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |

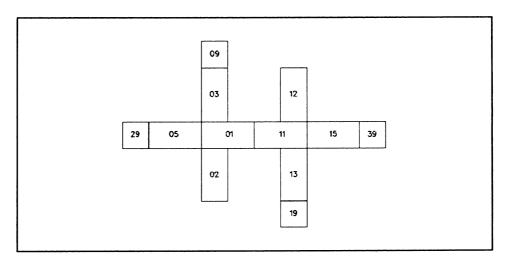

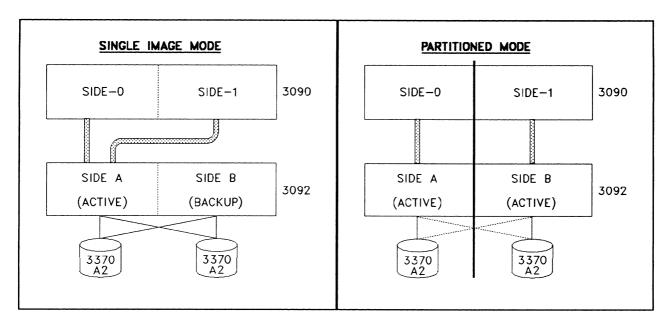

| 14.      | PCE Operating states of a 3092 Model 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |

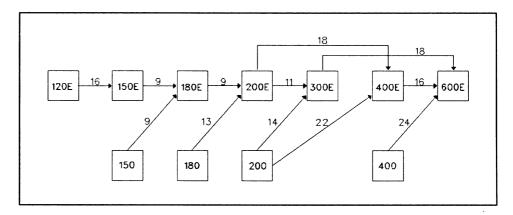

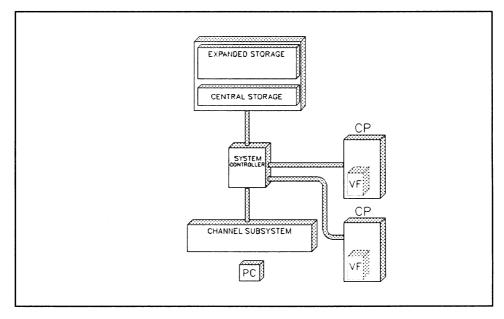

| 15.      | Uniprocessor Design - Models 120E, 150/150E, 180/180E 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2 |

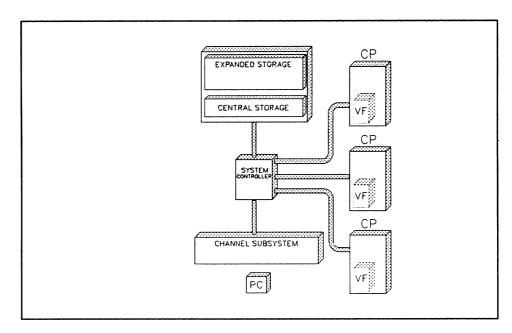

| 16.      | Two-Way (Dyadic) Processor Design - Models 200/200E 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2 |

| 17.      | Three-Way (Triadic) Processor Design - Model 300E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |

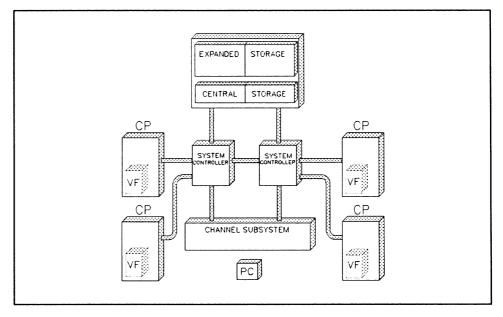

| 18.      | Four-Way Processor Design - Models 400/400E 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3 |

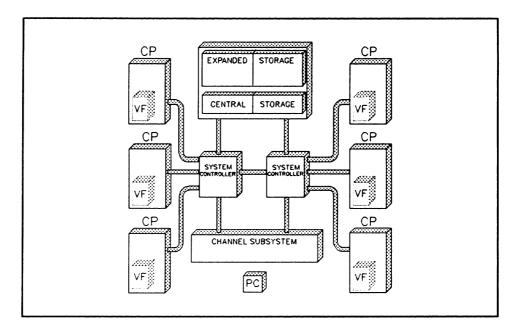

| 19.      | Six-Way Processor Design - Model 600E 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4 |

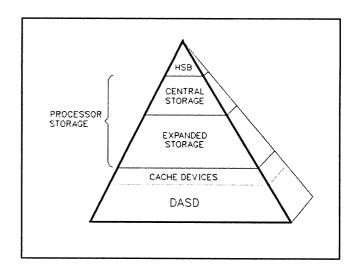

| 20.      | Storage Hierarchy 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 7 |

| 21.      | Sample I/O Queueing Activity Report for 3090 processor 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5 |

| 22.      | Sample I/O Device Activity Report 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5 |

| 23.      | Sample Paging Activity Report (Main Storage Paging Rates) 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 6 |

| 24.      | Sample Monitor II Paging (SPAG) Report                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 9 |

| 25.      | Sample Monitor II Address Space Data (ASD) Report 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0 |

| 26.      | MVS/SP 2.1.7 Dispatcher Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 7 |

| 27.      | 3090 Channel Path Grouping 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5 |

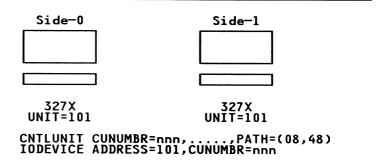

| 28.      | Example of Invalid Single-Image Console Definition 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 7 |

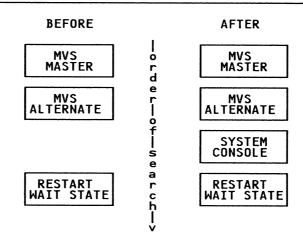

| 29.      | DCCF Message Display - Order of Search                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 9 |