# ICL Technical Journal

Volume 2 Issue 4

November 1981

## ICL Technical Journal

# Contents

## Volume 2 Issue 4

| Architecture of the ICL System 25<br>A. Walton                                                                                                                 | 319 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Designing for the X.25 telecommunications standard K.J. Turner                                                                                                 | 340 |

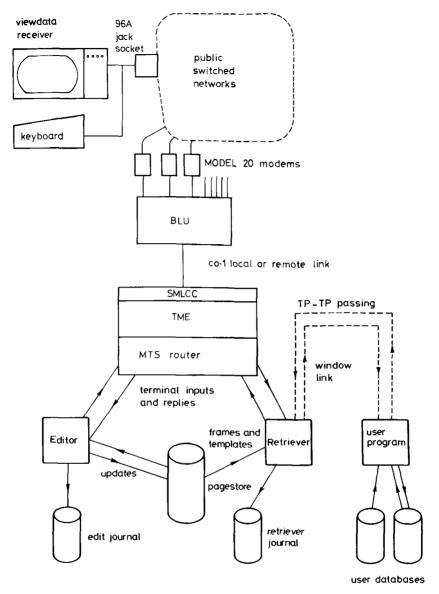

| Viewdata and the ICL Bulletin System<br>D.R.Olivey and R.Sugden                                                                                                | 365 |

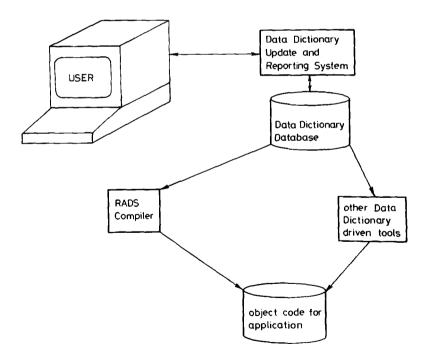

| Development philosophy and fundamental processing concepts<br>of the ICL Rapid Application Development System RADS<br>A.P.G.Brown, H.G.Cosh and D.J.L.Gradwell | 379 |

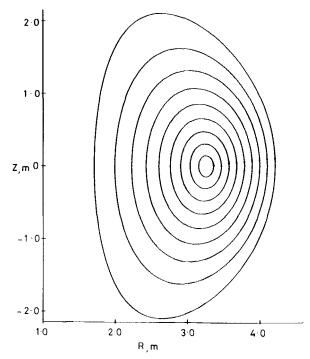

| A moving-mesh plasma equilibrium problem on the ICL Distributed<br>Array Processor<br><i>P.Kirby</i>                                                           | 403 |

|                                                                                                                                                                |     |

#### **Editorial Board**

Professor Wilkes retired from his Chair at Cambridge in the autumn of 1980 and is now living in America; he has decided to resign from the Editorial Board, on grounds of practicality. The Board and the management of ICL take this opportunity to record their very warm appreciation of the great amount he has done for the Technical Journal. His wisdom and his advice, based on his unrivalled experience as one of the pioneers of the computer age, and his insistence as a scientist and a scholar on high but realistic standards have been invaluable. The Board sends its thanks and good wishes to a colleague who is greatly respected and whose company has always been enjoyed.

It is the Board's good fortune that Mr. Donald Davies of the National Physical Laboratory has accepted the Company's invitation to become a member. He too has experience going back to the earliest days of the digital computer, for whilst Professor Wilkes was building one classic machine, EDSAC, at Cambridge, he was one of the team which was building another, ACE, at NPL. The Board welcomes Mr. Davies with this issue of the Journal.

## ICL Technical Journal

The ICL Technical Journal is published twice a year by Peter Peregrinus Limited on behalf of International Computers Limited

| Editor<br>J.Howlett<br>ICL House, Putney, London SW15 1SW, England |  |

|--------------------------------------------------------------------|--|

| Editorial Board                                                    |  |

| Deltonia Dolla                        |                |

|---------------------------------------|----------------|

| J. Howlett (Editor)                   | D.W. Kilby     |

| D.W.Davies                            | K.H. Macdonald |

| (National Physical Laboratory)        | B.M. Murphy    |

| D.P.Jenkins                           | J.M. Pinkerton |

| (Royal Signals & Radar Establishment) | E.C.P. Portman |

| C.H.Devonald                          |                |

|                                       |                |

All correspondence and papers to be considered for publication should be addressed to the Editor

Annual subscription rate: £10 (cheques should be made out to 'Peter Peregrinus Ltd.', and sent to Peter Peregrinus Ltd., Station House, Nightingale Road, Hitchin, Herts, SG5 1RJ, England. Telephone: Hitchin 53331 (s.t.d. 0462 53331).

The views expressed in the papers are those of the authors and do not necessarily represent ICL policy

## Publisher

Peter Peregrinus Limited PO Box 8, Southgate House, Stevenage, Herts SG1 1HQ, England

This publication is copyright under the Berne Convention and the International Copyright Convention. All rights reserved. Apart from any copying under the UK Copyright Act 1956, part 1, section 7, whereby a single copy of an article may be supplied, under certain conditions, for the purposes of research or private study, by a library of a class prescribed by the UK Board of Trade Regulations (Statutory Instruments 1957, No. 868), no part of this publication may be reproduced, stored in a retrieval system or transmitted in any form or by any means without the prior permission of the copyright owners. Permission is however, not required to copy abstracts of papers or articles on condition that a full reference to the source is shown. Multiple copying of the contents of the publication without permission is always illegal.

© 1981 International Computers Ltd

Printed by A.McLay & Co. Ltd., London and Cardiff

ISSN 0142-1557

# **Architecture of the ICL System 25**

## Alan Walton

ICL Distributed Systems Division, Bracknell, Berks., UK

#### Abstract

The organisation and operation of the hardware of the ICL System 25 small-business machine is described. The relation to the existing System Ten, with which it is compatible, is indicated.

#### 1 Introduction

System 25 is a physically small, powerful and versatile computer aimed primarily at the needs of commercial data-processing. It is compatible with the ICL System Ten which has proved a very popular and successful small-business machine and of which approaching 10,000 are in use world-wide. System Ten was designed in 1968, since which time there have been considerable advances in both physical technology and concepts of computer architecture. The design of System 25 exploits these advances to give a machine which is in every sense more powerful and versatile than System Ten while retaining all the good features of the earlier machine, especially its ease of use. In essence, the aim of the new design is to provide in a single small system, and simultaneously if required, all the various services which are being requested in business operations, such as batch, transaction and distributed processing, word processing, and control of such devices as Point-of-Sale and Factory Data Collection terminals.

The machine is shown in Plate 1.

Particular features of System 25 architecture are as follows:

- (i) Features derived from the Primitive Level Interface, which is the definition of the prime interface between the software and the hardware and includes the instruction set, store map, data and arithmetic standards etc. It is based on that for System Ten with extensions for handling 8-bit data and new high-capacity discs, maintaining exact compatibility wherever possible so as to allow direct transfer of programs. The main features here are:

- (a) Partitioned store, to allow multi-programming with guaranteed independence and protection for the programs

- (b) Decimal arithmetic and decimal addressing; this allows computation on input data without the need for time-consuming decimal-tobinary conversion, and also makes the use of the machine easier and more natural.

- (c) Variable-length store-to-store operations, to allow efficient use of main-store space.

- (ii) Support for a number of communication protocols, allowing System 25 to be used as a secondary station to ICL and IBM mainframes or as a primary station driving remote peripherals.

- (iii) Means for supporting a wide range of peripherals via either System 25 standard interfaces (carried over from System Ten) or various Industry Standard interfaces. The main slow peripheral interface, for example, will allow the connection of up to 10 peripherals at distances of up to 1500m.

- (iv) The System 25 Bus, which is the key feature of the hardware organisation and on which the above features depend. It is a set of physically separate bussed highways, used to interconnect the modules which make up the system. Each highway is designed for its particular purpose, resulting in cost-effective system modules and efficient transfer of data within the system; and the architecture provides ample scope for the incremental introduction of future enhancements.

The present paper describes in some detail the organisation and operation of the hardware and the means by which these and other features are realised. It concludes with a short note on the main software packages which are provided for support of the hardware; these will be dealt with in more detail in a second paper, to be published in the next issue of this Journal.

## 2 Hardware Organisation

## 2.1 Summary

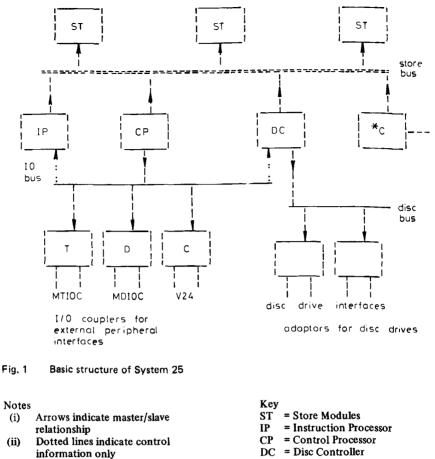

The key to the System 25 hardware organisation is a set of bussed highways collectively known as the System 25 Bus, which is used to interconnect a number of modules to create a system as shown in Fig. 1.

A system contains at least one of the following system modules, each of which consists of one or more boards interconnected via the backplane containing the System 25 Bus:

- a Control Processor which is responsible for the overall supervision of the system and for data transfers from slow peripherals

- an Instruction Processor which executes the System 25 Instruction Set

- a Store module

- a Disc Controller plus its associated Disc Adaptor which is responsible for fast I/0 transfers

- a Slow Peripheral Coupler to drive, an external slow peripheral interface for the connection of peripherals such as VDUs, printers.

There are two external slow peripheral interfaces supported by System 25, which have been carried over from System Ten. The main slow peripheral interface is the MTIOC interface (Multi Terminal Input Output Channel), which allows connection of up to ten slow peripherals onto a single twisted pair. The MDIOC interface

- (iii) MTIOC etc. explained in text

- \*C = Other Controllers T = T Coupler - MTIOC Interface

- D = D Coupler = MDIOC Interface

- C = C Coupler Communication Lines

(Multi Device Input Output Channel) allows connection of Point-of-Sale and Factory Data Collection terminals carried over from System Ten.

System 25 also supports a number of local disc drive interfaces which are specific to the particular disc drive; and a variety of communications lines and their associated protocols.

#### 2.2 System 25 Bus

The System 25 Bus consists of two main bussed highways – the Store Bus and the I/O Bus – and a subsidiary Disc Bus. There are two lines common to all modules; a

System Reset line and a System Fail line.

The System 25 Bus is tracked in the back plane. The common lines, Store Bus and I/O Bus are tracked to all board locations. The Disc Bus is only tracked to those locations which house a Disc Controller and its associated Disc Adaptors.

On any of the highways, transfers across the highway can only be initiated by a master module. The other module involved in the transfer is a slave module.

2.2.1 Store Bus: The Store Bus is used to transfer either one or five bytes of data between one of the master modules and one of the store modules (a slave module) and consists of

- 23 Address lines (7 bit binary Block Address and a 4 digit decimal Byte Address within a block)

- 40 Bidirectional Data lines (5 bytes)

- 2 Store Function lines

- 1 Store Mode line

- 3 Interface Control lines

- 1 Master Clock line (4 MHz, equivalent to a clock period of 250nsec)

Transfers on the Store Bus occur in synchronism with the Master Clock.

A 'daisy-chain' Bus Request line is used to resolve contention for use of the Store Bus. When a master module obtains access to the Store Bus, it will set Bus Reserved to inhibit the contention logic for one slot time. At the same time the master module enables the address and data onto the bus lines. The store module will respond with data in time to be latched into the master module at the end of the second slot. Thus a single transfer takes two clock periods.

During the second slot contention can take place for the next store cycle.

The store is defined to have two modes of operation. In Word mode, 5 bytes of data are transfered in parallel across the bus. In Byte mode, a multiplexor in the store module is used to transfer a single byte of data on the lowest numbered byte data lines.

The store cycle is 500ns (two clock periods) giving bandwidth of 10Mbyte/s in Word mode and 2Mbytes/s in Byte mode.

2.2.2 I/O Bus: The I/O Bus is driven by the Control Processor (the master module) and is used as the transfer path for control information to other modules and as a byte multiplexing interface for the transfer of data to or from I/O Couplers. It consists of

- 8 Bidirectional data lines

- 2 Function lines

- 2 Function Qualifier lines

- 5 Interface Control lines

- 1 Strobe Line

The transfer of a single byte of data takes a minimum of 8 interactions on the I/O Bus.

The I/O Bus provides for up to 64 Input/Output Channels (IOCs) which are independent logical transfer paths, a single coupler may have more than one IOC.

Each IOC is defined to have a set of 4 output registers which are written to by the Control Processor and a set of 4 input registers which are read by the Control Processor. Access to these registers is controlled by the Function and Function Qualifier lines.

The Control Processor can select a particular IOC by writing the IOC number to one of the output registers (Come On Line) and the selected IOC will then remain 'On Line' until 'Offline' is set or another IOC is selected.

The Control Processor will initiate the transfer of a block of data by writing to the Control Word register of the selected IOC. Thereafter the transfers of the command, data and status bytes for the block of data are initiated by an interrupt from the IOC.

There is a single bussed interrupt line which is set by an IOC requesting service. A 'daisy chained' Interrupt Acknowledge line will cause the highest priority interrupting IOC to place its IOC number on the data lines.

The Control Processor will bring the interrupting IOC Online and read from the input registers the interrupt type, associated data and the assigned partition number. The Control Processor will then write any output data to the output registers. Finally, the Control Processor will clear the interrupt by writing to the Clear Interrupt register and set the IOC Offline.

2.2.3 Disc Bus: The Disc Bus is driven by the Disc Controller and is used as the transfer path for control information to Disc Adaptors, and as a block multiplexing interface for the transfer of data to or from Disc Adaptors. It consists of

- 8 Bussed Bidirectional Data lines

- 1 Bussed Control line

- 1 Select line to each Adaptor

- 1 Service Request line from each Disc Adaptor

- 1 Strobe line.

The Disc Bus consists of one or more physically separate segments, each driven by one Disc Controller.

Each Disc Adaptor contains a buffer which is used to store the disc transfer parameters sent across the data lines by the Disc Controller.

When the Disc Adaptor is ready to transfer a block of data, it requests service from the Disc Controller. The Disc Controller will initiate a data transfer operation and the block of data is transferred across the disc bus in synchronism with the Strobe line at 3Mbytes/s.

## 2.3 External Peripheral Interfaces

2.3.1 MTIOC Interface: The MTIOC interface (Multi Terminal Input Output Channel) is the main interface for connecting slow peripherals onto System 25, and has been carried over from System Ten. Up to 10 terminals may be multi-dropped onto a single twisted pair cable which can be up to 1500m long.

Data is transmitted bit-serially as 7 data bits and two check bits at a bit rate of 28kHz or 56kHz, using frequency modulated encoding. The equivalent byte rate is nominally 1500 or 2700 characters transferred per second. Successful transmission of a byte of data in one direction is followed by an Acknowledge transmission in the other direction. If no acknowledgment is detected, the data byte is automatically retransmitted.

The protocol of the MTIOC interface allows for four commands:- Read, Write, Read Control and Write Control. Interpretation of the commands depends on the particular peripheral. In between transfers, the terminals are polled in sequence. The selected terminal will acknowledge the poll if it requires service.

Electrical isolation of the interface is achieved by transformer coupling at the terminal.

2.3.2 MDIOC Interface: The MDIOC interface (Multi Device Input Output Channel) is used for connecting Point-of-Sale or Factory Data Collection terminals into System 25 via the D coupler (see Fig. 1). It allows the connection of a single terminal up to 12000m from System 25 via a single twisted pair. The data transfer rate depends on the direction of the transfer and length of line and can be set to the following data rates (in characters per second).

| Output to<br>Terminal | Input from<br>Terminal | Maximum<br>Line Length |

|-----------------------|------------------------|------------------------|

| 120                   | 1200                   | 12000m                 |

| 1200                  | 3600                   | 6000m                  |

| 2400                  | 4800                   | 1000m                  |

Data is transmitted as 7 data bits and one parity bit using an asynchronous transmission protocol. Optical couplers in the D Coupler give electrical isolation. The terminal provides the line current which is modulated by the terminal for input data, and the impedance at the D Coupler is modulated for output data.

The coupler contains a multiplexor for the connection of up to 16 lines into a single IOC, and two IOCs with a total connection capability of 32 lines.

2.3.3 Communication Interfaces: CCITT V24 interfaces are provided for the connection of modems and associated communications lines. System 25 will support a variety of protocols, including:

| ICL CO1  |                              |

|----------|------------------------------|

| ICL CO3  | binary synchronous protocols |

| IBM 3270 | · · ·                        |

| IBM SNA  | SDLC                         |

| X25      | HDLC                         |

There is a special binary synchronous protocol for the connection of remote System 25 or System Ten video terminals.

2.3.4 Other External Interfaces: Other external interfaces can be supported by the use of special-purpose couplers, for example:

RS 232 interface for special purpose printers. Cartridge Magnetic Tape Drive interface.

## 2.4 System Modules

2.4.1 Instruction Processor: The Instruction Processor is a master module on the Store Bus and a slave module on the I/O Bus. It is responsible for execution of the System 25 Order Code.

Instruction execution is initiated by commands on the I/O bus from the Control Processor and continues until an I/O instruction is encountered or it is commanded to switch to another partition by the Control Processor. For I/O instructions, the relevant real addresses are computed and stored in the control store and the Control Processor is informed by an interrupt on the I/O Bus.

When commanded to switch partition it will continue processing until the next successful branch instruction before suspending operations and informing the Control Processor.

2.4.2 Control Processor: The Control Processor is a master module on the Store Bus and *the* master module of the I/O bus. It is responsible for the overall control of the system and for transferring data between Slow Peripherals (via the I/O Bus) and main store (via the Store Bus).

It initiates processing by the Instruction Processor and controls switching between partitions.

It initiates slow peripheral operations by translating the I/O instruction into commands which are then routed to the appropriate coupler. It maintains the store address and counts associated with the transfer, and operates as a byte multiplexor for the transfer of data between the I/O Bus and Store Bus. It initiates transfers to fast peripherals which then proceed autonomously under the control of a disc controller. At the end of the transfer the Control Processor will initiate a partition switch to the originating partition.

It uses a configuration table in the control store to translate logical device numbers into real device numbers.

2.4.3 Store Modules: A store module is a slave on the Store Bus and provides a five-byte-wide random access store. It will generate parity when writing to store, and check the stored parity when reading from store.

2.4.4 Disc Controllers: A disc controller is a master module on the Store Bus, is a slave module on the I/O Bus and is *the* master module of a Disc Bus.

It is responsible for scheduling disc operations and for transferring data between Disc Adaptors (via the Disc Bus) and Main Store (via the Store Bus). It initiates disc operations at the request of the Control Processor by translating commands contained within the Control Block associated with a Disc I/O instruction and routing the information to the appropriate Disc Adaptor.

It maintains the store address associated with the transfer, and operates as a block multiplexor for the transfer of data between the Disc Bus and Store Bus.

A Disc Adaptor is responsible for interfacing the disc drives into System 25 and for transforming the protocols and data formats used within System 25 into commands and data across the disc drive interfaces. There is a different Disc Adaptor for each type of disc drive.

2.4.5 Slow Peripheral Couplers: A Slow Peripheral Coupler is a slave on the I/O Bus and controls one or more external peripheral interfaces of communications lines. It is responsible for driving the external interface and for transforming the protocols and data formats used by the peripherals or communications lines into those used within System 25.

Each Slow Peripheral Coupler consists of one or more logical Input Output Channels (IOC). There is a different Slow Peripheral Coupler for each type of external interface as follows:

- T Coupler for MTIOC interfaces

- D Coupler for MDIOC interfaces

- C Coupler for communications lines

- R Coupler for Cartridge Magnetic Tape

- V Coupler for special interfaces

## 3 System 25 Primitive Level Interface

The Primitive Level Interface of a system is the main interface between the hardware of the system and the software running in the system. It consists of a definition of the Instruction Set plus a definition of associated data standards, store map, arithmetic standards, etc.

The System 25 Primitive Level Interface is based on that of System Ten, with a limited number of extensions to support the new high capacity discs, to improve performance and to handle 8-bit data.

## 3.1 Data Standards

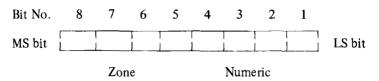

3.1.1 Data Codes: Data is stored within System 25 as 8-bit bytes as follows:

The bits are numbered from 1 to 8; bit 8 is the most significant bit and bit 1 the least. Bits 8 to 5 contain the Zone code of the byte and have a value in the range 0 to 15. Bits 4 to 1 contain the Numeric code of the byte and have a value in the range 0 to 15.

The characters assigned to the codes are given in Table 1 for Zone codes 0-7 and correspond to the ISO 7 bit set. Zone codes 8-15 do not have assigned characters.

The 6 bit subset which is compatible with System Ten consists of Zone codes 2-5 (i.e. bits 8 and 6 are ignored).

3.1.2 Numeric Data: Numeric data is stored as variable length Binary Coded Decimal (BCD) byte strings in sign and modulus form. The Numeric code of each byte has a value in the range 0-9. For positive numbers each byte has a Zone code of 3, so that numbers are stored as their character code.

For negative numbers each byte except the least significant byte has a Zone code of 3. The least significant byte has a Zone code of 5. Thus the character representation of the least significant byte for the numerals 0 to 9 is P to Y, as in the following table:

Numeral 2 3 5 7 8 9 Positive number 0 1 4 6 V W X Y Negative number Character P 0 R S Т U

Example: -1234 is stored as 123T.

3.2 Store Map

The Main Store is divided into a number of areas as shown in Fig. 2.

- (a) Control Store from 0 to 2999, which contains I/O control and configuration data for use by the Control Processor.

- (b) Common Store from absolute address 3000 which contains information accessible to all partitions. Write access is prohibited to locations 0 to 299 of Common. This area is called Protected Common.

- (c) Partition Store. An area of store for each partition which contains the partition program, data and Index Registers.

|     |   |   | C | olun | nn O | 1   | 2  | 3 | 4 | 5 | 6 | 7   | Bit |              |

|-----|---|---|---|------|------|-----|----|---|---|---|---|-----|-----|--------------|

|     |   |   |   |      | 0    | 0   | 0  | 0 | 0 | 0 | 0 | 0   | 8   |              |

|     |   |   |   |      | 0    | 0   | 0  | 0 | 1 | 1 | 1 | 1   | 7   | ZONE<br>CODE |

|     |   |   |   |      | 0    | 0   | 1  | 1 | 0 | 0 | 1 | 1   | 6   | CODE         |

| Bit | 4 | 3 | 2 | 1    | 0    | 1   | 0  | 1 | 0 | 1 | 0 | 1   | 5   |              |

|     | 0 | 0 | 0 | 0    | NUL  | DLE | SP | 0 | @ | Р | ١ | р   |     |              |

|     | 0 | 0 | 0 | 1    | SOH  | DC1 | !  | 1 | Α | Q | а | q   |     |              |

|     | 0 | 0 | 1 | 0    | STX  | DC2 | "  | 2 | B | R | b | r   |     |              |

|     | 0 | 0 | 1 | 1    | ETX  | DC3 | £  | 3 | С | S | c | S   |     |              |

|     | 0 | 1 | 0 | 0    | EOT  | DC4 | \$ | 4 | D | Т | d | t   |     |              |

|     | 0 | 1 | 0 | 1    | ENQ  | NAK | %  | 5 | Ε | U | e | ս   |     |              |

|     | 0 | 1 | 1 | 0    | ACK  | SYN | &  | 6 | F | v | f | v   |     |              |

|     | 0 | 1 | 1 | 1    | BEL  | ETB | ,  | 7 | G | W | g | w   |     |              |

|     | 1 | 0 | 0 | 0    | BS   | CAN | (  | 8 | Н | Х | h | x   |     |              |

|     | 1 | 0 | 0 | 1    | HT   | ЕМ  | )  | 9 | 1 | Y | i | у   |     |              |

|     | 1 | 0 | 1 | 0    | LF   | SUB | *  | : | J | Z | j | z   |     |              |

|     | 1 | 0 | 1 | 1    | VT   | ESC | +  | ; | K | [ | k | {   |     |              |

|     | 1 | 1 | 0 | 0    | FF   | FS  | ,  | < | L | ١ | 1 | I   |     |              |

|     | 1 | 1 | 0 | 1    | CR   | GS  | -  | = | М | ] | m | }   |     |              |

|     | 1 | 1 | 1 | 0    | SO   | RS  | •  | > | N | ۸ | n | -   |     |              |

|     | 1 | 1 | 1 | 1    | SI   | US  | /  | ? | 0 | - | 0 | DEL | -   |              |

|     |   |   |   |      |      |     |    |   |   |   |   |     |     |              |

Character codes

Table 1

3.2.1 Control Store: The lowest numbered area of main store is called the Control Store which has been added for System 25. This area of store is not accessible to the partitions, except from Partition 0 in special circumstances, and is used to hold control information for Input/Output operations and for general system operation.

A duplicate set of A and B registers hold the control words in absolute address form and other registers are used by the Control Processor to progress the state of I/Otransfers.

An area of control store is used to hold a translation table for the mapping of the logical device numbers within an 1/O Instruction into real device numbers and IOC numbers.

| 20000                 | PARTITION 1<br>STORE | 0000P                 |

|-----------------------|----------------------|-----------------------|

| 19999                 |                      | 6999P                 |

|                       | PARTITION 0<br>STORE |                       |

| 13000                 |                      | 0000P                 |

| 12999                 |                      | 9999C                 |

|                       | COMMON<br>STORE      |                       |

| 3000                  |                      | 0000C                 |

| 2999                  |                      | 2999                  |

|                       | CONTROL<br>STORE     |                       |

| 0                     |                      | 0000                  |

| Absolute<br>Addresses |                      | Relative<br>Addresses |

Fig. 2 Main store layout

3.2.2 Common Store: There is an area of Main Store accessible to all programs called Common. The size of Common is set during Initial Program Load to a value in the range 10000 to 80000 bytes, in units of 1000 bytes.

The first 300 bytes are called Protected Common and write access is inhibited. It is used to hold the Program Pointer (P register -5 bytes) and Input/Output Control Words (A and B registers -5 bytes each) for each partition.

The next 700 bytes are used for entry points to supervisory routines, tables controlling shared resources (such as disc), and a Mailbox for communication between partitions.

The remainder of Common is used to hold shared routines (e.g. housekeeping routines) and buffer areas for the bulk transfer of data between partitions.

3.2.3 Partition Store: Each program in System 25 operates within its own area of main store called a Partition and the System 25 architecture allows for up to 20 partitions. The size of each partition is set during Initial Program Load to a value in the range 0 to 80000 bytes, in units of 1000 bytes.

There is no defined structure within the partition store and its use is determined by the user program. However, bytes 11-14, 21-24, 31-34 are used as index registers by the instructions, and bytes 40-44 are used to hold the contents of the P Register when a Program Check occurs.

#### 3.3 Arithmetic operations

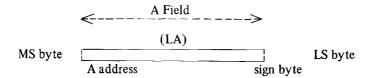

Arithmetic operations use two operands called the A operand and the B operand,

which are fetched from the A and B Fields. The result is stored in the B Field.

The basic arithmetic functions are Add, Subtract, Multiply and Divide, with these conventions:

Add – the A Operand is added to the B Operand. Subtract – the A Operand is subtracted from the B Operand. Multiply – the A Operand is multiplied by the B Operand. Divide – the B Operand is divided by the A Operand.

3.3.1 Numeric Fields: Numeric data is stored in variable length fields of up to 10 bytes.

The A Operand is contained within the A Field as shown below

The length of the A Field is defined by the contents of the LA field in the instruction.

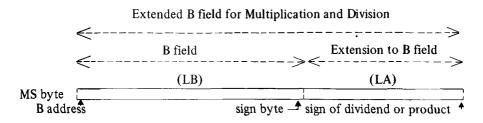

The B Operand is contained in the B Field or the Extended B Field as shown below

The length of the B Field is defined by the contents of the LB Field in the instruction and the length of the extension to the B Field is defined by the contents of the LA Field.

3.3.2 Addition and subtraction: Addition and subtraction of numeric data is performed digit by digit starting with the least significant bytes of the two operands. The result of each byte is stored before the next more significant bytes are accessed.

The arithmetic operations performed on the two numeric parts of the bytes depend upon the Zone codes of the least significant bytes as defined in the table below. Zone codes 0-3 and 8-11 are treated a. a positive, codes 4-7 and 12-15 are treated as negative. The zone code of the result is set to 3 or 5.

| Function | B operand | A operand | Operation   | Result   |           |

|----------|-----------|-----------|-------------|----------|-----------|

|          |           | f<br>k    | 1<br>1<br>1 | Sign     | Zone Code |

| ADD      | +         | ı +       | B + A       | <br>  +  | 3         |

|          | +         |           | B - A       | +        | 3         |

| l        |           | ,<br>i +  | B-A         | ;  _     | 5 1       |

| 1        | -         | -         | B + A       | -        | 5         |

| SUBTRACT | '<br>! +  | . +       | B- A        | ;<br>; + |           |

|          | ; +       | -<br>-    | B+A         | +        | 3         |

|          | -<br>I –  | +         | B+A         | -        | 5         |

| <br>1    | l _<br>L  | -<br>     | B - A       |          | 5         |

If the value of A is greater than the value of B, and the operation is B - A, then the sum is complemented and the sign of the result is inverted.

If the A operand is shorter than the B operand, it is effectively extended with zeros on the left during the operation.

If the A operand is longer than the B operand, it is truncated from the left and the truncated part is ignored.

3.3.3 Multiplication: Multiplication is performed by a sequence of additions of the A operand, extended with a zero digit, to the extended B field. The number of additions is determined by the value of the digits of the B operand.

The zone of the least significant byte of the extended B-field is set according to the signs of the A and B operands. Zone codes 0-3 and 8-11 are treated as positive signs.

| Operan | d Signs | Resi | ult       |

|--------|---------|------|-----------|

| A      | В       | Sign | Zone Code |

|        | +       | +    | 3         |

| +      | -       |      | 5         |

| -      | +       | -    | 5         |

| _<br>  |         | +    | 3         |

The result of using overlapped operands is undefined.

3.3.4 Division: Division is performed by a sequence of subtractions of the A operand (divisor), extended with a zero digit, from the extended B field which contains the B operand (dividend).

The result (quotient) is stored in the B field and the remainder is stored in the extension to the B field.

The Zone code of the least significant byte of the B field is set according to the signs of the A and B operands.

| d Signs | Quotient                              |           |  |  |

|---------|---------------------------------------|-----------|--|--|

| В       | Sign                                  | Zone Code |  |  |

| +       | +                                     | 3         |  |  |

| +<br>-  | -<br>-<br>+                           | 5         |  |  |

|         | d Signs<br>B<br>+<br>-<br>+<br>-<br>+ |           |  |  |

The sign of the B operand is not changed and becomes the sign of the remainder.

The result of using overlapped operands is not defined.

## 3.4 Address format

The addresses on System 25 are represented as decimal numbers in the range 00000 to 79999, the first digit being a page number in the range 0 to 7. The whole address is stored in part of a 4-byte address word, together with a marker C which takes the value 0 if the address is relative to a partition base and 1 if it is relative to the Common base.

The format is as follows:

The decimal digits d3, d2, d1, d0 giving the address within the page with d3 the most significant (thousands) and d0 the least significant (units), are binary-coded in bits 4 to 1 of the four bytes. Bit 4 is the most significant, bit 1 the least.

The page number p is stored in inverse form in bit 5 of each of bytes 1, 2, 3 with the most significant bit in byte 3.

The marker C is stored in bit 7 of byte 4 and its inverse in bit 6.

The remaining bits - that is, bits 6 to 8 of bytes 1 to 3 and bit 5 of byte 4 - are not used by address computation.

| -           |    |    | <u> </u> |                 |                    |

|-------------|----|----|----------|-----------------|--------------------|

| Byte<br>Bit |    | 0  | 1        | 2               | 3                  |

| Bit         | 8  | *  | *        | *               | 0                  |

|             | 7  | *  | *        | *               | C                  |

|             | 6  | *  | *        | *               | 0<br><u>C</u><br>* |

|             | 5  | PO | P1       | $\overline{P2}$ | *                  |

|             | 4  |    |          |                 |                    |

|             | 3  | D3 | D3       | D1              | DO                 |

|             | 32 |    |          |                 |                    |

|             | 1  |    |          |                 |                    |

The layout is shown in the diagram below.

\*not used

The convention used here and in the following paragraphs is that a capital letter indicates a field and the corresponding lower-case letter the content of that field: thus p is the number of the page stored in the page-number field P, and the sub-field D3 of the address field contains the decimal digit d3.

#### 3.5 Instruction format

3.5.1 General description: System 25 uses 2-address instructions of the form

#### F, A, B

where F is the function code and A,B are operand addresses. The interpretation of the contents of the address fields depends on the contents of other fields stored in the instruction word, as follows:

| LA, LB   | give the lengths of the operands   |

|----------|------------------------------------|

| AC, BC   | are address markers                |

| IA, IB   | concern indexing                   |

| EIX      | concerns extended indexing         |

| IDA, IDB | concern direct/indirect addressing |

These are explained in the succeeding paragraphs.

An instruction occupies 10 bytes, which we number conventionally 0 to 9 from the left. The A,B addresses, in binary coded decimal, are held in bytes 1 to 4 and 6 to 9, respectively, with the format described in Section 3.4. The decimal digits are coded in bits 4 to 1 of the respective bytes, with bit 4 as the most significant bit. They must be in the range 0 to 9; a value in the range 10 to 15 will cause a Program Check.

The detailed layout of the instruction is shown in the diagram below, where the columns are the bytes and the rows the bits within the bytes. Bit 8 of each byte is always zero and bit 6, which normally contains the inverse of bit 7, is ignored.

| Byte |                                      | 0                         | 1                         | 2                         | 3                         | 4                        | 5                          | 6                          | 7                          | 8                          | 9                         |

|------|--------------------------------------|---------------------------|---------------------------|---------------------------|---------------------------|--------------------------|----------------------------|----------------------------|----------------------------|----------------------------|---------------------------|

| Bit  | 8<br>7<br>6<br>5<br>4<br>3<br>2<br>1 | 0<br>F3<br>*<br>IDA<br>LA | 0<br>F2<br>*<br>PA0<br>A3 | 0<br>F1<br>*<br>PA1<br>A2 | 0<br>F0<br>*<br>PA2<br>A1 | 0<br>AC<br>*<br>F4<br>A0 | 0<br>IA1<br>*<br>IDB<br>LB | 0<br>IA0<br>*<br>PB0<br>B3 | 0<br>IB1<br>*<br>PB1<br>B2 | 0<br>IB0<br>*<br>PB2<br>B1 | 0<br>BC<br>*<br>EIX<br>B0 |

3.5.2 F, the Function: The function field F comprises 5 bits F0 to F4 located as follows:

F3 to F0 in bit 7 of each of bytes 0 to 3 respectively F4, inverted, in bit 5 of byte 4

3.5.3 A and B, the Addresses (cf. Section 3.4): An address is specified by the combination of the P field (bits 5 of bytes 1-3 or 6-8) and four decimal digits (binary coded in bits 4-1 of bytes 1-4 or 6-9). The P field gives the page number in the range 0-7, stored in inverse form, and the decimal digits the adress of a byte within a page.

For the A address for example the P field is stored as follows:

| bit 5 byte 1<br>2<br>3 | $\begin{array}{c c} \overline{PA0} & 1 \\ \hline PA1 & 1 \\ \hline PA2 & 1 \end{array}$ | 0<br>1<br>1 | 1<br>0<br>1 | 0<br>0<br>1 | 1 | 0<br>1<br>0 | 1<br>0<br>0 | 0<br>0<br>0 |

|------------------------|-----------------------------------------------------------------------------------------|-------------|-------------|-------------|---|-------------|-------------|-------------|

| page number            | 0                                                                                       | 1           |             | 3           | - | _           | 6           | 7           |

and similarly for B.

In the decimal address, A3 is the most significant digit (i.e. the thousands digit) and A0 the least (i.e. the units digit).

3.5.4 LA and LB, the Operand Lengths: These fields are normally used to define the lengths of the operands in bytes; their contents can have values in the range 0 to 9, with the value 0 indicating a length of 10 bytes.

For some instructions the two fields are used together to give a single operand length in the range 1 to 100 bytes; in this case LA is the tens digit and LB the units, with 00 indicating a length of 100 bytes.

$3.5.5 \ AC$  and BC, the Address Markers: These are used to indicate whether the address is relative to Common base or to a partition base. If AC is set to 1, the A address is in Common; if to 0, it is in the partition store and therefore relative to the current partition base.

3.5.6 IA, IB and  $\overline{EIX}$ : Indexing: The IA, IB fields are used to specify whether or not the relevant addresses are to be indexed and if so, which index registers are to be used. For the A address the interpretation is as follows:

| IA1 | IA0 | Index Register |

|-----|-----|----------------|

| 0   | 0   | No indexing    |

| 0   | 1   | 11P to 14P     |

| 1   | 0   | 21P to 24P     |

| 1   | 1   | 31P to 34P     |

and similarly for B. The location of the index registers is given in Section 3.2.3.

The EIX field concerns *extended indexing*, explained in Section 3.6.1 below. This is a 1-bit field, stored in inverse form in bit 5 of byte 9. If this bit is set to 0, extended indexing is specified.

3.5.7  $\overline{IDA}$  and  $\overline{IDB}$ : Indirect Addressing: These fields are used to indicate whether the contents of an address field (possibly indexed) are to be used as the operand

address directly, or whether they point to another 4-digit field which contains the required address in relative address format but not aligned to a boundary.

The instruction contains the values of the field in inverse form; the interpretation is

$\overline{IDA}$  = 1 indicates direct addressing for A  $\overline{IDA}$  = 0 indicates indirect addressing for A

and similarly for B. The operation is explained further in Section 3.6.

## 3.6 Address Computation

3.6.1 Operand Relative Address: The relative address of the A Operand is evaluated in two stages as follows:

First, if indirection is specified ( $\overline{IDA} = 0$ ), the A field in the instruction (PA, A3, A2, A1, A0 and AC) is used to fetch the four byte field containing the indirect address, which is then used in place of the A field.

Second, if indexing is specified (IA  $\neq$  0), the contents of the specified index register are added.

If extended indexing is not specified ( $\overline{EIX} = 1$ ), the addition is performed modulo 10000.

If extended indexing is specified ( $\overline{\text{EIX}} = 0$ ), the addition is performed modulo 80000.

3.6.2 A Operand Address Marker, ac: The address marker of the A operand, ac, is evaluated in two stages in parallel with the evaluation of the operand relative address as follows:

First, if indirection is specified ( $\overline{IDA} = 0$ ), bit 7 of byte A+3 (of the indirect address field) is fetched and used in place of the AC field.

Second, if indexing is specified  $(IA \neq 0)$  and extended indexing also is specified, bit 7 of the least significant byte of the specified index register is combined (logical OR) with the AC field to generate the address marker.

3.6.3 A Operand Absolute Address: If ac = 0, the A operand is in Partition and the A operand absolute address is formed by adding the A operand relative address to the partition base address

If ac = 1, the A operand is in Common and the A operand absolute address is formed by adding the A operand relative address to the Common base address (3000).

3.6.4 B Operand Address: The B operand address is formed in a similar manner using the PB, B3, B2, B1, B0 and BC fields in conjunction with IDB and IB.

|               | Mnemonic  | :      | Instruction Name                   | Funct<br>Code | ion     |

|---------------|-----------|--------|------------------------------------|---------------|---------|

| Computational | A         |        | Add                                |               | 4       |

| Instructions  | S<br>M    |        | Subtract                           |               | 7       |

|               | M<br>D    |        | Multiply<br>Divide                 |               | 6<br>5  |

|               | C         |        |                                    |               | 5<br>14 |

|               | IC        | *      | Compare<br>Indirect Length Compare |               | 30      |

|               | ic        |        | Logical Instructions:              | LA            | 20      |

|               | AND       | *      | – And                              | 3<br>2        | 20      |

|               | OR        | *      | - Or                               | 1             |         |

|               | NEQ       | *      | – Not Equivalent                   | 2             |         |

| Address       | MA        |        | Move Address                       |               | 3       |

| Arithmetic    | _         |        | Modify Address                     |               | Ũ       |

| Instructions  |           |        | Instructions:                      | LA            | 2       |

|               | AAI       |        | - Add Address Immediate            | 0             | -       |

|               | AA        |        | - Add Address                      | 1             |         |

|               | SAI       | *      | - Subtract Address                 |               |         |

|               |           |        | Immediate                          | 2             |         |

|               | SA        | *      | - Subtract Address                 | 3             |         |

|               | CA        | *      | - Compare Address                  | 4             |         |

| Data          | MC        |        | Move Character                     |               | 8       |

| Transfer      | IM        | *      | Indirect Length Move               |               |         |

| Instructions  |           |        | Character                          |               | 24      |

|               | MN        |        | Move Numeric                       |               | 9       |

|               | FN        |        | Form Numeric                       |               | 13      |

|               | X         | *      | Exchange                           |               | 15      |

|               | PK<br>UPK | *<br>* | Pack                               |               | 31      |

|               | E         |        | Unpack<br>Edit                     |               | 29      |

| Control       |           |        |                                    |               | 12      |

| Instructions  | B<br>SM   |        | Branch<br>Set Mode                 |               | 11      |

| listituctions | 2141      |        | Set Mode                           |               | 10      |

| Input/Output  | R         |        | Read                               |               | 0       |

| Instructions  | W         |        | Write                              |               | 1       |

|               | SR        | *      | Start Read                         |               | 16      |

|               | SW        | *      | Start Write                        |               | 17      |

|               | TS        | *      | Test 10 Status                     |               | 18      |

|               |           |        |                                    |               |         |

\*New Instructions for System 25

## 4 Input/Output Operations

## 4.1 General:

System 25 Input/Output normally operates in a strictly synchronous manner in

that when a Read or Write Instruction is encountered, the partition is suspended until the I/O transfer is complete.

However, use of the Start Read and Start Write instructions will allow the partition to continue processing until the next I/O instruction is given. Use of the Test IO Status instruction allows the progress of the I/O transfer to be monitored.

In System 25, peripherals are divided into two types:-

slow peripherals which are assigned to a single partition and can only be driven by that partition.

fast peripherals which are shared between all partitions and can be driven by any partition.

The System 25 I/O instructions provide direct control of all the peripherals assigned to a partition, although disc transfers are normally controlled by invoking supervisory routines.

## 4.2 Slow Peripheral Control:

Up to 10 slow peripheral devices may be driven by a single partition and the IO instruction contains the logical device number, the address of an area of store for the data transfer and a count of the number of bytes to be transferred.

There are four I/O operations:

Read – Transfers up to 10000 bytes of data from the peripheral into store Write – Transfers up to 10000 bytes of data from main store to the peripheral Read Control is reserved for loading programs.

Write Control was used by System Ten to generate control codes outside the 64 character set across the MTIOC interfaces and for compatibility, this is retained on System 25. However on System 25 the 8 bit store allows control characters to be sent with a Write Instruction.

#### 4.3 Fast Peripheral Control

For fast peripherals (discs and magnetic tapes) the logical device number is replaced by a Fast Access Channel (FAC) number. Specific numbers have been allocated for different types of fast peripherals as follows:

- 0 is used for discs.

- 1 to 4 are used to address up to four tape drives.

- 5 to 9 are not used.

4.3.1 Disc Control: System 25 Discs are organised as a logical set of sequential 512 byte sectors. The mapping of logical sectors into real track, head, sector numbers is performed by the Disc Adaptor and is dependent on the particular disc characteristics. System Ten discs are organised as logical 100 byte sectors.

The B field in the IO instruction contains a pointer to a 6 byte Control Block which contains the disc drive number (0 to 15), function, count and sector number. System Ten disc transfers were always a single sector of 100 characters. System 25 compatible data disc transfers provide the same operation and five 100 byte blocks are mapped into a single 512 byte sector on the disc and the logical sector number in the Control Block is divided by 5 to give the equivalent 512 byte sector number.

The System 25 disc functions are

Compatible Mode Read or Write – transfers a single 100 byte sector using System Ten Control Block format (maximum sector number = 99,999)

Extended Compatible Mode Read or Write – transfers a single 100 byte sector using System 25 Control Block format (maximum sector number = 9,999,999)

String Read and Write -a string of up to 10,000 bytes starting at the beginning of a sector and extending over several sectors is transferred for one instruction, using System 25 Control Block format (maximum sector number = 999,999)

Other functions are provided to format the disc and read the status of the previous transfer.

4.3.2 Magnetic Tape Control: The use of the IO instruction fields is the same as to the slow peripherals. The Read and Write instructions cause the transfer of a single block of data to or from the tape.

The Read Control instruction is used to access status information from the tape controller and the Write Control instruction is used for control commands for the control of the tape, e.g. Rewind.

Cartridge Magnetic Tape is driven as a 'slow peripheral'.

## 5 System 25 Software

System 25 software is largely derived from System Ten to allow the large number of application programs developed for that machine to run on System without change.

System 25 can be run with various levels of software support; at the lowest level a program can be loaded directly into a partition and can run and control its peripherals without reference to any supervisory program. The main ICL supporting software is provided in the following three packages, which together give the facilities normally provided by an operating system.

## 5.1 DMF III (Data Management Facilities)

This is the basic supervisor package and is derived from the System Ten equivalent, DMF II. It consists of the following components:

CSM (Conversational System Manager) which provides facilities for the main-

tenance of the file store and loading programs

LIOCS (Logical Input/Output Control Software) which is a set of housekeeping routines for the logical control of the disc and magnetic tape Utilities for sorting and editing files

## 5.2 IAS (Interactive Applications Support)

This provides an environment for transaction processing applications, in which the control of slow peripherals is separated from the application program. It consists of the following components:

Video/Printer Drivers which control up to 10 Videos or printers on a single interface

Data Buffer and Message Handling Routines which are used to pass data between the application programs and the Video/Printer drivers.

#### 5.3 CAM (Communications Access Manager)

This provides a simple macro interface for application programs for the control of communication lines. There is a different CAM package for each communication line protocol. It consists of the following components:

Communication Line Driver which performs the low-level control of the line Data Buffer and Message Queue handling routines

Macro Interface Routines which convert the macro calls from the application program into messages and data blocks

As was stated in the introduction, the software will be described in more detail in a second paper.

# Designing for the X.25 telecommunications standard

## K. J. Turner

ICL Information Processing Architecture Division, Kidsgrove, Staffs

#### Abstract

Packet switching is becoming increasingly important in telecommunications systems in many countries and the 'X.25 Recommendation' of the International Telegraph and Telephone Consultative Committee (CCITT) is now widely accepted as defining the standard for the interface to a public packet-switched network. The paper describes the ICL Communications System Controller, a hardware device with associated software, which has been designed to interface ICL main frame computers to X.25 packet-switched networks. The description is preceded by a short account of X.25 and of ICL's own communication protocol ICLC-03. The essential function of the CSC is to convert between ICLC-03 and other protocols: the conversion between ICLC-03 and X.25 is discussed.

#### 1 Introduction

#### 1.1 X.25

1.1.1 X.25 history: X.25 is probably the most important telecommunications standard to have appeared in recent years. It represents the substantial agreement between communications experts on the interface to Public Data Networks of the packet-switching variety.

Packet-switching began in earnest around 1968 with the opening of networks such as ARPANET (US) and SITA, the international airlines' system. Many countries followed suit in implementing their own packet-switching networks, for example EPSS (UK), RETD (Spain) and TELENET (USA). With great foresight CCITT (International Telegraph and Telephone Consultative Committee) saw the future importance of this developing communications technology and began a programme of work to produce an international specification for interfacing to such networks. Thus was Recommendation X.25<sup>1</sup> born in 1976, to be enhanced within a year by the publication of an alternative link protocol with improved error recovery.

Following the publication of X.25 a considerable amount of activity ensued as older networks were brought into line with the recommendation and new networks

were implemented in direct conformance to it. Typical of these new networks were TRANSPAC (France) and SAPONET (South Africa).

It was inevitable that such widespread and diverse implementations of X.25 would lead to various interpretations of the recommendation and would suggest desirable enhancements to it. CCITT therefore began the revision of X.25 with a view to reconciling the differences in interpretation that had arisen. The result was a new and much larger version of  $X.25^2$  in 1980. At present the conformance of packetswitching networks worldwide to the revised recommendation is patchy, but there is hope of a high degree of commonality by 1982.<sup>3</sup> Recent networks such as PSS (UK) are already largely in agreement with the latest version.

An interesting property of X.25 networks is that it is fairly easy to couple them together, and indeed CCITT has evolved Recommendation  $X.75^2$  for just this purpose. By provision of such 'gateways' between X.25 networks it becomes possible to make calls through the concatenation of several of them. Thus X.25 may lay the foundation for truly international digital data communication.

The following two Sections give a brief overview of X.25. For further background information there are good texts on packet-switching in general<sup>4</sup> and on  $X.25^5$  in particular.

1.1.2 X.25 services and facilities: Packet-switching is a digital communications technique which fragments data into 'packets' of an agreed maximum size and then multiplexes them onto the communications channel with data from other sources. Because the communication channel can carry interleaved packets from many sources its capacity can be utilised very effectively. This is to be contrasted with a circuit-switched connection where plant (lines and switches) will typically be dedicated to that connection. The average utilisation of a communications connection is often low, particularly for interactive traffic, thus leading to inefficient usage of the associated plant. An authority which administers both packet-switched and circuit-switched connection because the operating capacity may be more nearly reached. The actual choice of connection type must depend, however, on the specific application and on other factors such as the availability of equipment.

Since data from many sources can be multiplexed onto one channel, the packets of each stream need to be distinguished by some kind of address: in X.25 this is termed the Logical Channel Number (LCN). X.25 defines only the interface between the DTE (Data Terminal Equipment, supplied by the manufacturer) and the DCE (Data Circuit-terminating Equipment, usually supplied by the network authority). Many of the parameters of X.25 are therefore local only, that is they apply to the DTE-DCE link. Of course they generally have an end-to-end (DTE to DTE) effect, but usually in a loosely coupled way. The LCN in X.25 is therefore for DTE-DCE addressing only.

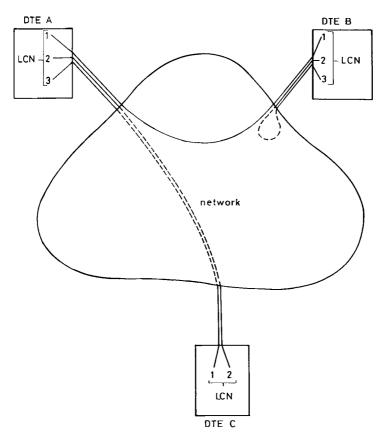

To establish a connection from one DTE to another via an X.25 network it is necessary to make what is termed a virtual call, which identifies the destination DTE by means of a unique subscriber number. As part of establishing the call each DTE-DCE pair will select a logical channel of its link or which to transfer data. The identifier, the Logical Channel Number, of this will generally be different at each end. Completion of the virtual call results in a virtual circuit which persists until the call is terminated (by either party). This kind of temporary association between DTEs is termed a Switched Virtual Circuit (SVC). By way of contrast, a fixed association may also be set up by agreement with the network administration and the other party: this requires no call to set it up or clear to terminate it and is called a Permanent Virtual Circuit (PVC). As shown in Fig. 1, a DTE may have concurrent virtual circuits to several DTEs or even to itself (for test purposes).

X.25 provides a number of options which are available on subscription to the network or on call set-up, as appropriate. They include:

incoming calls barred outgoing calls barred reverse charging call re-direction charging information membership of a private group of subscribers flow control parameters

Most of these have obvious parallels in the telephone network. Only the flow control parameters are unusual in being peculiar to the digital transmission technique used.

The Virtual Circuit service is the only one which is generally available on X.25 networks. A more recent addition to X.25 is the Datagram service which (like Telex) allows the transmission of individually addressed messages. To capitalise on the widespread provision of Virtual Circuits, CCITT has defined a Fast Select facility which in some respects resembles the Datagram Service. A Fast Select call sets up a transient Virtual Circuit, allowing a block of data to be sent with the request. The recipient may either clear the call immediately (optionally supplying a block of data in response) or turn it into a normal virtual call. Thus Fast Select may serve a transaction-oriented application or an enquiry-type of application where the response may be brief or lengthy.

1.1.3 X.25 operation: X.25 is a three-level protocol which conforms to the principle of layer independence. While each layer must know what functions are provided to it by the layer below and what functions are required of it by the layer above, it does not need to have any knowledge of the mechanisms within the adjacent layers by means of which these functions are provided. Such a protocol may be modelled by the familiar 'onion skin' architecture.<sup>6</sup> The three levels of X.25 are:

- (i) the Physical (or Transmission) Level

- (ii) the Link (or Frame) Level

- (iii) the Network (or Packet) Level

In concert they define the procedures across the DTE-DCE interface for establishing connections, transmitting data and breaking connections. The functions of the levels may be briefly summarised as follows:

(i) Physical Level

This concerns the control of the modem (or equivalent) and the transmission of data. Two separate recommendations apply here:  $X.21^2$  (for digital transmission) and X.21 bis<sup>2</sup> (for analogue transmission). X.21 bis (which describes the use of the familiar V-Series modems) is the most commonly found type of interface at present. X.25 connections are full-duplex and so are normally by leased line.

(ii) Link Level

This concerns the control of the DTE-DCE link. Two alternative protocols are used, both of which are variants of HDLC (High-Level Data Link Control): LAP (Link Access Protocol) which is related to the International Standards Organisation (ISO)<sup>7</sup> and the European Computer Manufacturers Association (ECMA)<sup>8</sup> Unbalanced Class, and LAPB (Link Access Protocol Balanced) which is compatible with ISO<sup>9</sup> and ECMA<sup>10</sup> Balanced Class. Both LAP and LAPB offer two-way simultaneous transparent data transfer (with protection against loss, corruption and duplication of data) and flow control facilities. They differ, however, in the way connection, disconnection and error recovery are handled. LAPB is generally agreed to be superior to LAP and is preferred by CCITT.

(iii) Network Level

This concerns the control of the conversations multiplexed over the DTE-DCE link. The protocol closely resembles that used at Link Level, but offers the important advantages of multiplexing and interconnection of DTEs with differing characteristics (e.g. packet size or throughput). Another important function is the provision of an expedited data route, e.g. for interrupt or break-in.

1.1.4 X.25 Between DTEs: Although X.25 is strictly a DTE-DCE interface standard, it is quite easy to adapt it for point-to-point DTE-DTE links. There are some minor asymmetries in X.25 which can be removed by building sufficient flexibility into a DTE: later Sections mention a few of these. The benefit of X.25 DTE-DTE operation is that the same implementation and protocol can be used for private or public connections.

1.1.5 Related protocols: An X.25 DTE requires a relatively high degree of sophistication that would be expensive to provide in a simple terminal. CCITT identified the need for easy attachment of basic terminals such as teletypewriters to X.25 networks and evolved the interlinked X.3, X.28 and X.29 Recommendations. Like X.25 these have been revised since their initial issue<sup>4</sup>.

X.3 defines the behaviour of a Packet Assembler/Disassembler (PAD) which concentrates the traffic from asynchronous terminals onto X.25. X.28 specifies the interface between the PAD and the terminal. X.29 describes the conversation between the PAD and the controlling DTE. X.29 may thus be viewed as a higher – level protocol which is carried over X.25. X.29 does not, however, fit into the more modern communications architectures mentioned in Section 1.2.3 and may therefore be supplanted in the long term by other Virtual Terminal Protocols.

## 1.2 ICL communications

1.2.1 The ICLC-03 communication protocol: ICL's current communication protocol Full XBM, also known as ICLC-03, is multi-level. The principal components of ICLC-03 are:

- (i) Transmission Level

- (ii) Link Level

- (iii) Group Level

- (iv) Access Level

These hierarchically organised levels constitute the means whereby data is transported on behalf of applications or users. There is an obvious similarity to the corresponding functions in X.25.

(i) Transmission level

This concerns the control of the modem (or equivalent) and the transmission of data. Connections may be either half-duplex or full-duplex. (ii) Link Level

This concerns the control of the link between a primary and one or more secondaries. The protocol is two-way alternate and is derived from the ISO Basic Mode procedures.<sup>11</sup>

- (iii) Group Level This concerns the control of the conversations multiplexed over a primarysecondary link.

- (iv) Access Level

This concerns the control of the sequencing and presentation of application or user messages. Unlike the lower three levels, Access Level occurs in several varieties to match the needs of differing devices and functions. Of these, the Device Independent Access Level (DIAL) and the Logical Connection Control Access Level (LCC) particularly concern the subject of this paper.

Like X.25, DIAL offers two-way simultaneous, transparent data transfer and flow control, together with control functions for expedited data and for error recovery. Indeed DIAL and X.25 offer such similar facilities that the mapping between them is almost one-to-one.

ICLC-03 distinguishes clearly between data transfer and connection control functions. LCC provides facilities for mainframe control of connection, disconnection, and error handling. As with DIAL, these map onto X.25 in a natural way.

The close correspondence between ICLC-03 and X.25 makes protocol conversion from one to the other particularly practicable. Some examples of the relationship between the two are given below. The attraction to ICL of ICLC-03 in X.25 protocol conversion is the ease with which large communications systems can be built out of local ICL networks interconnected by public X.25 networks.

| ICLC-03                     | <b>X</b> .25            |

|-----------------------------|-------------------------|

| connect                     | call                    |

| disconnect                  | clear                   |

| reset                       | reset                   |

| access level<br>data packet | data packet<br>sequence |

| program<br>function         | interrupt               |

For the connection of PAD-concentrated teletypes a similarly convenient mapping of X.29 on to the ICLC-03 Scroll Mode Access Level can be defined.

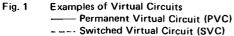

1.2.2 ICL Communications System Controller CSC: ICL's Communications System Controller hardware (CSC) is designed to front-end the larger ICL 2900 mainframes via a high-speed trunk interface. Communications lines are interfaced by hardware units known as couplers. CSC's primary functions are to act as a concentrator for ICLC-03 communications traffic and to convert other communications traffic to ICLC-03 form. It is in this latter function that the majority of the interest and complexity lies. Currently CSC offers conversion of three classes of protocol:

- (i) Asynchronous (teletypewriter)

- (ii) Synchronous (video, clustered video)

- (iii) Bit-oriented (X.25, X.29)

This paper addresses itself solely to the design of an X.25 protocol converter.

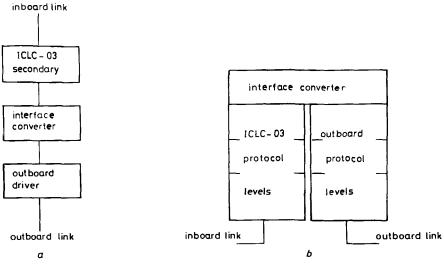

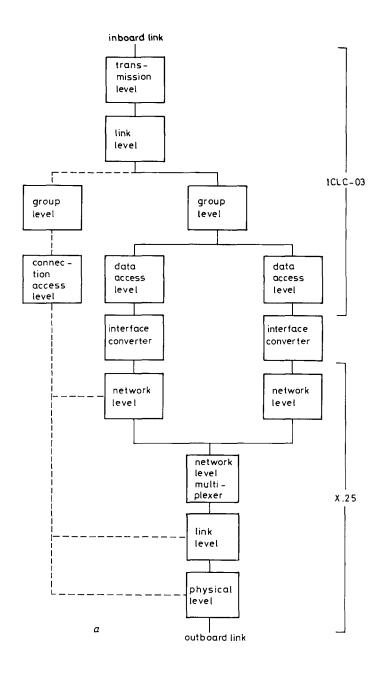

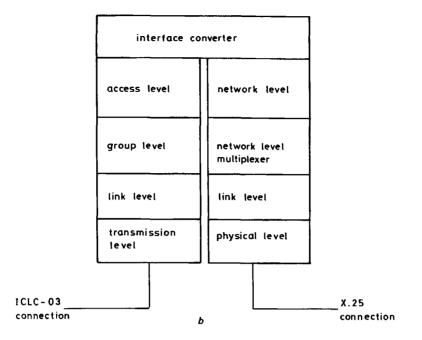

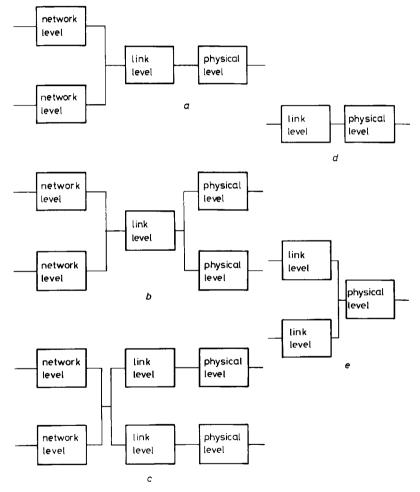

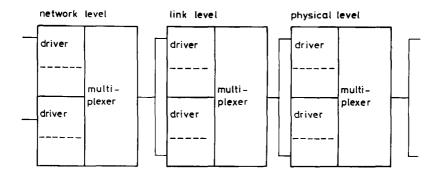

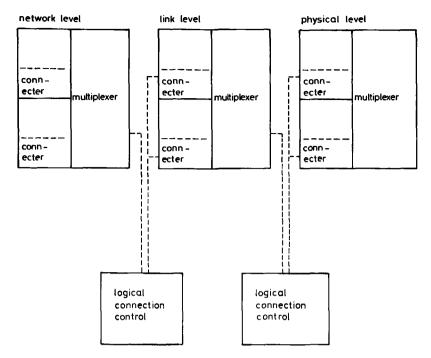

The CSC system software may be broadly divided into Kernel and Communications. A Peripheral sub-system is also used during development. The Kernel offers the usual resource management facilities such as scheduling, buffer allocation, timer control, error handling and hardware interfacing. The Communications subsystem comprises a number of Protocol Converters and the ICLC-03 multiplexer, which may be regarded as a kind of null protocol converter. A significant amount of code is shared between the protocol converters because of the inevitable commonality of functions to be performed. The general structure of CSC and its relationship to the mainframe are illustrated in Fig. 2.

After the next Section giving a short note on the ICL general information processing architecture IPA, the rest of the paper is concerned with CSC. The three main Sections deal with the following aspects:

- Section 2- Functionality. The services provided by CSC.

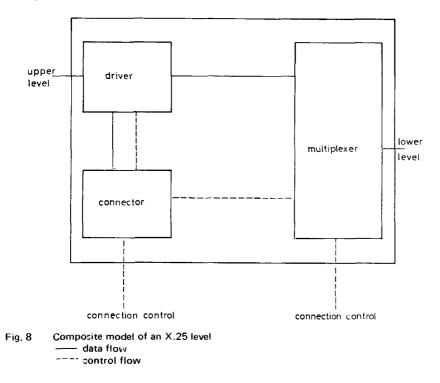

- Section 3- Architecture. The basic design of CSC and an indication of the mechanisms by means of which these services are provided. In particular, three important software components Driver, Connector and Multiplexer are described.

- Section 4. Resource Management. Scheduling, flow control, handling of errors and collection of statistical information are described.

The final Section deals briefly with the testing of this equipment.

1.2.3 ICL Information Processing Architecture IPA: Considerable interest has been shown in recent years in the development of Open Systems Interconnection  $(OSI)^{.6},^{12}$  The concept which underlies OSI is that any host or terminal in a community should be able to interwork with any other. As a step towards this goal ISO have evolved a Reference Model<sup>13</sup> which defines an appropriate system architecture. The functions of this model are separate into seven layers, each of

#### Fig. 2 CSC structure and relationship to mainframe

#### ICL TECHNICAL JOURNAL NOVEMBER 1981

347

which builds progressively on the layers below it. The principal layers are:

| Information Processing          | 7 Application Layer                                                           | (user programs/facilities)                                              |  |  |

|---------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------|--|--|

| Functions                       | 6 Presentation Layer<br>5 Session Layer                                       | (device characteristics)<br>(synchronisation)                           |  |  |

| Telecommunications<br>Functions | 4 Transport Layer<br>3 Network Layer<br>2 Data Link Layer<br>1 Physical Layer | (end-to-end-connection)<br>(routing)<br>(data transfer)<br>(electrical) |  |  |

ICL has adopted the OSI model as the basis of its Information Processing Architecture (IPA).<sup>14</sup> The particular relevance of X.25 to IPA is that it can serve as the major part of the lower three layers of the model.

## 2 Functionality

## 2.1 Split of functions

As explained in the paper by Kemp and Reynolds,<sup>14</sup> there are many possible ways of partitioning the layers of the IPA model between different functional units. For protocol conversion of X.25 the most natural choice was to separate the lower three layers and implement them in CSC. The networking capability is therefore vested in CSC and the end-to-end control is handled by the mainframe.

The other split of function between the mainframe and CSC is that of control as opposed to data transfer. The general philosophy of ICLC-03 is that the mainframe is responsible for overall control. It is therefore the mainframe which initiates conections, breaks them and decides how to recover from serious errors, although it is CSC that carries out the detail of these operations.

## 2.2 Services

As well as standard X.25, CSC also implements the ICL DTE-DTE variant for pointto-point operation.

At the Physical Level X.25 has a choice of connection service: X.21 or X.21 bis. CSC supports only the latter.

At the Link Level X.25 has the option of operating with either of the access protocols LAP, LAPB referred to in Section 1.1.3(ii). Both of these are implemented in CSC because the older networks have not yet converted from LAP to LAPB.

It was explained in Section 1.1.2 that X.25 offers two main types of service: Virtual Circuits and Datagrams. It was also noted that Virtual Circuits, which are very similar to physical circuits, fall into two classes: Switched Virtual Circuits (SVCs) which are analogous to Public Switched Telephone Network connections, and Permanent Virtual Circuits (PVCs) which are analogous to leased-line connections. The concept of a Datagram is rather foreign to many communications protocols, which usually follow the pattern of connect/exchange transactions/ disconnect. In particular, the mapping of datagrams on to ICLC-03 would be fairly difficult. It is also unlikely that datagrams will be widely available on X.25 networks in the near future.

CSC therefore supports the Virtual Circuit service only. Besides the basic SVC/PVC Split mentioned above, Switched Virtual Circuits are further categorised as Inward (ISVC), Bothway (BSVC) or Outward (OSVC). These labels refer to which end originates the call, not to which end originates the data since a virtual circuit is intrinsically symmetrical once it is set up. Note that it is really the logical channels of the DTE - DCE interface, rather than the virtual circuits, which have a call direction.

## 2.3 Facilities

Facilities in the X.25 sense refer to the options available with a particular service. In the case of CSC they define the properties of the virtual circuits. When a Switched Virtual Circuit (SVC) is set up the required facilities are specified in the call request or are given default values. X.25 allows facilities, particularly those related to flow control, to be negotiated. The recipient of the call may either reject the call if the requested facilities are unsuitable or accept the call with modified facilities. This dynamic set-up of facilities is not available on a Permanent Virtual Circuit; instead, the facilities must be agreed at subscription time with the network authority and sometimes also with the other party.

The choice and negotiation of call facilities is not really an appropriate matter for a front-end processor like CSC. For example, the decision to accept a reverse charge call may require reference to a file of accredited users. CSC therefore handles all facilities transparently and leaves call analysis or synthesis to the mainframe. Although the same level of sophistication is not needed at the Link or Physical Levels their connection is handled in the same way for consistency.

A wide range of facilities is available on virtual circuits. The ones permitted by CSC are as follows, although it should be noted that the support of a number of them is dependent on the host operating system:

fast select reverse charging call re-direction call charge notification membership of a private group of subscribers variable choice of flow control parameters negotiable choice of flow control parameters sub-addressing packet re-transmission

The facility names are fairly self-explanatory, but a few require further description. Sub-addressing allows the network subscriber address to be extended by further

information to determine the process or function required of the called DTE. CSC does not use sub-addressing since the call request has fields which allow this requirement to be specified more comprehensively. Packet re-transmission refers to the ability of the DTE to retransmit an unacknowledged packet on request. This is not needed for interfacing to an X.25 network but may be required for DTE-DTE operation, where symmetry is necessary.

It is difficult to design a single DTE implementation which will work against all or even most X.25 networks because the facilities offered, and sometimes their encodings, vary widely.<sup>15</sup> The general approach with CSC was to support the common features and to tolerate variations in the protocol where these were known. Detailed study of individual network specifications was often necessary to determine incompatibilities.

## 2.4 Parameters

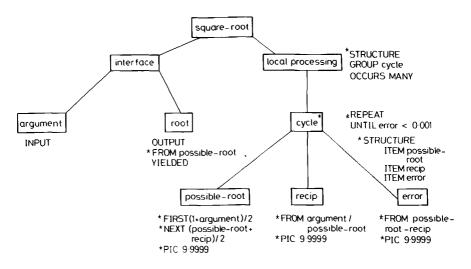

The operation of each level of X.25 is characterised by a large number of parameters. At the Physical Level they specify the modem and line characteristics. At the Link Level they specify the frame size, time-outs, retry limits, etc. At the Network Level they specify the packet size, throughput requirement, circuit type, etc. Although some of these parameters (such as the Link Level addresses) are fixed by convention in X.25, CSC permits their values to be varied to maximise the range of applications in which CSC may be used. Thus DTE-DTE X.25 operation at Link Level is simply achieved by giving one end the X.25 DTE address and the other end the X.25 DCE address.