# ICL Technical Journal

Volume 2 Issue 2

November 1980

# Contents

|                                                                                                            | Volume 2 Issue 2 |

|------------------------------------------------------------------------------------------------------------|------------------|

| The ICL information processing architecture IPA<br>J.Kemp and R.Reynolds                                   | 119              |

| VME/B a model for the realisation of a total system concept<br>B.C.Warboys                                 | 132              |

| Birds, Bs and CRTs<br>I.D. MacArthur                                                                       | 147              |

| Solution of elliptic partial differential equations on the ICL<br>Distributed Array Processor<br>S.J. Webb | 175              |

| Data routing and transpositions in processor arrays C.R.Jesshope                                           | 191              |

| A Bayesian approach to test modelling<br>M.Small and C.W.Bartlett                                          | 207              |

| Notes for authors                                                                                          | 219              |

ICL TECHNICAL JOURNAL NOVEMBER 1980

.

# ICL Technical Journal

The ICL Technical Journal is published twice a year by Peter Peregrinus Limited on behalf of International Computers Limited

Editor J. Howlett ICL House, Putney, London SW15 1SW, England

| Editorial Board                       |                |

|---------------------------------------|----------------|

| J. Howlett (Editor)                   | D.W. Kilby     |

| D.P. Jenkins                          | K.H. Macdonald |

| (Royal Signals & Radar Establishment) | B.M. Murphy    |

| M.V. Wilkes FRS                       | J.M. Pinkerton |

| (University of Cambridge)             | E.C.P. Portman |

| C.H.Devonald                          |                |

All correspondence and papers to be considered for publication should be addressed to the Editor

Annual subscription rate: £10 (cheques should be made out to "International Computers Limited", and sent to International Computers Limited, Corporate Communication, ICL Technical Journal Office, ICL House, Putney, London SW15 1SW)

The views expressed in the papers are those of the authors and do not necessarily represent ICL policy

#### Publisher

Peter Peregrinus Limited PO Box 8, Southgate House, Stevenage, Herts SG1 1HQ, England

This publication is copyright under the Berne Convention and the International Copyright Convention. All rights reserved. Apart from any copying under the UK Copyright Act 1956, part 1, section 7, whereby a single copy of an article may be supplied, under certain conditions, for the purposes of research or private study, by a library of a class prescribed by the UK Board of Trade Regulations (Statutory Instruments 1957, No. 868), no part of this publication may be reproduced, stored in a retrieval system or transmitted in any form or by any means without the prior permission of the copyright owners. Permission is however, not required to copy abstracts of papers or articles on condition that a full reference to the source is shown. Multiple copying of the contents of the publication without permission is always illegal.

© 1980 International Computers Ltd

Printed by A. McLay & Co. Ltd., London and Cardiff

ISSN 0142-1557

# The ICL information processing architecture IPA

### J.Kemp and R.Reynolds

ICL Marketing Division, Slough, Berks

#### Abstract

IPA embodies ICL's strategy and plans for information processing over at least the next 10 to 20 years. It is not itself a product but a comprehensive and consistent set of systems concepts, design rules and function descriptions, together with specifications for interfaces and protocols, in accordance with which all existing software and hardware products will evolve and all new products will be developed. In broadest terms its objective is the provision of standard methods for linking together computers, computer systems and terminals via either public or private telecommunication lines or networks, extending to international linkings. The formal structure of IPA is based on the ISO seven-layered model for Open Systems Interconnection. The paper explains the need for such an architecture, describes the essence of the ISO model and shows its close relation to the existing ICL communications architecture Full XBM, from which IPA has evolved. The paper shows also how the principles of IPA can be implemented in various circumstances and describes some of the first products and user services which will be made available.

#### 1 Why is an architecture needed?

The early development of the digital electronic computer was dominated by the concept of the centralised installation. This was largely a consequence of the high cost of the processor and main random-access store with the physical bulk, large power demands and need for a controlled air-conditioned environment contributing. As the possibilities increased for the transmission of digitally encoded information over the telephone lines available from the national telecommunications authorities — the PO in the UK, the PTT's in most other countries and certain regulated companies in the USA — there was a great increase in the use of the computer from terminals remote from the centre, and of increasingly wide variety. But the standard remained, essentially, the central machine though now with possibly very large numbers — such as hundreds — of terminals directly connected.

This type of structure, with simple terminals all connected to a single powerful mainframe machine, does not present any deep problems of system management and co-ordination of data, and the disciplines necessary for successful operation became well understood. There are many systems of this kind all over the world, some on a very large scale, which have been operating very successfully indeed for many years now. But over the past few years the cost of both processing power and

storage capacity have fallen dramatically as a consequence of developments in micro-electronics. The physical size and power consumption of the equipment have been reduced equally dramatically and now only the largest systems need to be housed in air-conditioned or otherwise special accommodation. At the same time, all the world's telecommunications authorities are accelerating the growth of digital communication services: for example, a public packet-switched network TRANSPAC is now operating in France and a corresponding service PSS will be opened by the PO in Britain in the near future. All this has made the dispersal of processing power and data storage from the centre a much more practical and economic possibility and similarly for the devolution of authority and the diversification of electronic applications. The user community, which now includes virtually the whole of the business world, has already seen great value in such developments and there is a real demand that, to put it most simply, it should be possible to connect any piece of equipment to any other and to transfer any kind or quantity of information. with everything kept properly under control and without the user needing to concern himself with anything but the job in hand.

This presents problems of an entirely different order of complexity from those of the simple centralised system with its directly connected terminals. Purely tactical or *ad hoc* solutions are no longer sufficient and indeed we are no longer dealing with simple data processing but rather with the interconnection of a wide variety of tasks aided by computers and associated devices: in fact, with all aspects of information processing and handling in general. There is clearly a need for a firm strategy for linking equipment together if one is to avoid the situation in which every new demand presents a new problem. But the strategy must be based on fundamental and widely accepted principles if the products to which it leads are to meet the needs of such a wide range of users. It must also allow for needs which have not yet been specified. The term 'architecture' has come to be used for the embodiment of such a strategy in the computer world and considerations of this kind have led ICL to the development of IPA.

IPA is not a product in the sense of a particular piece of hardware or software but a coherent set of rules and conventions which provide for the unified and comprehensive interconnection of the main ICL products such as data-processing systems, business systems and terminals, and give also the capability for connecting these to other products either from ICL or from other manufacturers.

# 2 IPA and the ISO 7-Layered Model for Open Systems Interconnection

The overwhelming majority of linkings between computers and associated devices such as terminals and satellite processors are made over lines provided by the national telecommunication authorities such as the PTT's. At one end of such a link User A despatches some information, which we can call a 'message', together with a destination, which we can call the 'address' of User B at the other end, and it is the responsibility of the PTT to deliver this safely, that is, without errors and to the correct address. How this is achieved, in particular how any errors in transmission are detected and corrected, is no concern of A or B; and what is in the message is no concern of the PTT. Thus there is a clear separation between the information processing function, which is the concern of the users, and the communication function, which is the concern of the communication authority. But the manufacturer of the computing and other equipment must be aware of the requirements of this authority and must ensure that the signals constituting the messages which are put into the communication system conform in every way to the standards and conventions to which that system is built. Therefore whilst there is this separation between the processing and communication functions, the architecture which we have been discussing cannot avoid a close involvement with the architectures of international telecommunications systems.

There has been intensive study by international bodies for several years past of the question of what has become known as Open Systems Interconnection, or OSI. This means that if OSI were achieved in any community - which ideally should be the whole world - then there would be no technical barriers to the user of any computer, terminal or similar device communicating with any other within the community. The telephone and Telex are familiar examples of virtually world-wide OSI. The paper by Houldsworth<sup>1</sup> in the first issue of this Journal discusses this concept and the technical problems which underly its realisation. Recently the International Standards Organisation (ISO) has published<sup>2</sup> a formalisation of the fundamental structure of information processing and communication, which has become known as the ISO 7-Layered Reference Model for OSI, This, like IPA, is a set of concepts. It separates the full processing-plus-communication spectrum into an ordered set of seven subactivities or *layers*, in such a way that only adjacent layers interact with one another. The effect of this is both to make clear and to bound the consequences of a change in the implementation of any layer. In particular, the model makes the vital separation between processing and communication. The model and its relevance to the aims and realisation of OSI are discussed by Brenner.<sup>3</sup> We shall give a brief account of the model in Section 3 of this paper.

IPA and the ISO model are concerned with the same problem and it is evident that their aims have a lot in common. Further, the model is the outcome of truly international studies by groups of acknowledged experts in this field and is an expression of fundamental concepts which have already gained international acceptance. Therefore ICL, who have a general policy of adhering to international standards wherever possible, have incorporated the ISO model into the structure of IPA. It is not entirely accidental that the structure of the current ICL communications protocol Full XBM (also known as ICLC-03) is already quite close to that of the ISO model.

# 3 The ISO model and full XBM

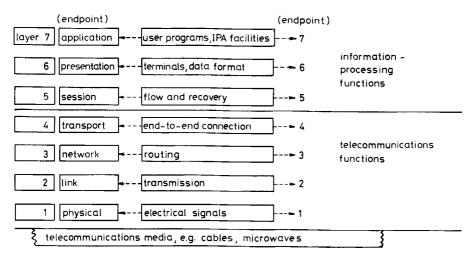

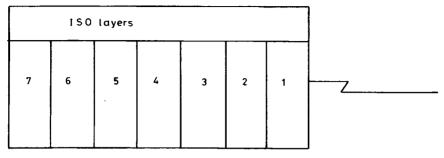

Fig. 1 gives the structure of the model

The details are discussed at length in the definitive ISO publication<sup>2</sup> and more briefly by Brenner.<sup>3</sup>

The top layers 7,6,5 are concerned with the information processing functions and with ensuring that the messages which are to be transmitted between the communicating parties contain all the information necessary to specify the task to be performed and to control the interchange in whatever way is desired. The top

#### Fig. 1 ISO 7-layered model for OSI

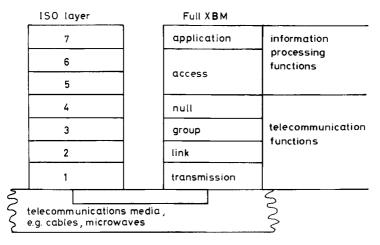

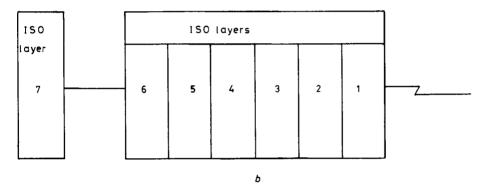

Fig. 2 Comparison between Full XBM and the ISO model

layer 7, the 'applications' layer, concerns the actual work which the users wish to do; they do not need to concern themselves with or even to be aware of the others below. The lower layers 4,3,2,1 are concerned with ensuring that the actual signals input to the communications system – for example, the public telecommunications network – meet the requirements of that system. The basic concept is that information originating in any one layer is handed down through the layers below until it reaches the physical communications medium; after transmission it is handed up through the layers at the receiving end until it reaches the equivalent layer. A principle of fundamental importance is that whatever is 'done' to an information stream as it moves down from one level to the next below at the sending end is 'undone' as it moves correspondingly upwards through the layers at the receiving end. This means that communication is between layers at the same level – 'peer'

layers - and that to any layer the layers below together appear as nothing more than a delay line. For this reason David Ackerman of ICL, in his early work in this field, used the terms 'onion skin architecture' and 'principle of complementary reflection'.

Over the past few years ICL has developed a series of structures for communications of which the latest and most comprehensive before IPA was Full XBM, originally called ICLC-03. XBM means Extended Basic Mode. This has much in common with the ISO model as Fig. 2 shows.

Like the ISO mode, Full XBM embodies the principles of:

separation of information processing from telecommunication interfaces only between adjacent layers end-to-end communication only between 'peer' layers.

It was thus a natural evolutionary step to adopt the structure of the ISO model as the basis of the new architecture IPA.

#### 4 Initial implementations of IPA

#### 4.1 Communications processors

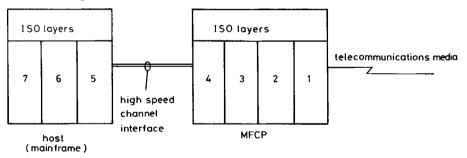

The first major ICL hardware product designed according to the principles of IPA is the Multi-Function Communication Processor, MFCP. This expresses in physical terms the important separation between the processing and communications functions. Fig. 3 shows the structure.

Fig. 3 The ISO Model and the ICL Multi-Function Communications Processor, MFCP

The MFCP provides the functions of layers 4,3,2,1 of the ISO model. Its purpose is to take care of all the operations which have to be performed in order to connect a mainframe (host) computer to a telecommunications system, such as for example a public packet-switched network. The top three layers are in the host machine. Layer 7 is of course the 'real' work which is to be done and is all the user need know about; layers 6 and 5 deal with data format, control of terminals and flow control and are implemented in the system software.

A great benefit resulting from this structure is that the host computer (meaning in effect the user) is insulated from changes in the communication system. Thus if the

#### ICL TECHNICAL JOURNAL NOVEMBER 1980

.

latter is a packet-switched network using the X-25 protocol, as is the case for the French TRANSPAC, the British PSS and other important networks, this can be provided in the MFCP by appropriate software or micro-code in layers 3,2,1. But other protocols, such as X-21 for circuit-switched networks, are emerging and these could be implemented if the need developed.

Fig. 4 a All ISO model layers in one unit b Application in 'back-end' processor

Communication between the host computer and the MFCP is via a high-speed channel and it is important that the host need not be concerned with the physical form of this – for example, whether it carries a single bit stream or is a 32-bit high-way. Therefore a new protocol has been defined for the purpose embodying the rules governing how information is to be transferred between layer 5 (in the host) and layer 4 (in the MFCP).

This implementation, with the whole of the transport function of the ISO model in the MFCP and the processing functions in the host, is clearly one of several possibilities. Two extremes are equally possible (shown diagrammatically in Fig. 4a and 4b):

- (a) a fully-integrated system with all the processing and transport capabilities (i.e. all seven layers) in one unit

- (b) a single unit providing the capabilities of layers 1 to 6, acting as a frontend to a machine dedicated to processing; then only layer 7 would be implemented in the latter.

Any other allocation can be made but the order of the layers must not be varied - a basic principle of the ISO model is that the functions of the various layers have been defined and there must be interaction only between adjacent layers. The important point is that if the principles of the model are held to, then there is plenty of scope for flexibility in design of equipment with no risk of loss of coherence, compatibility and standardisation.

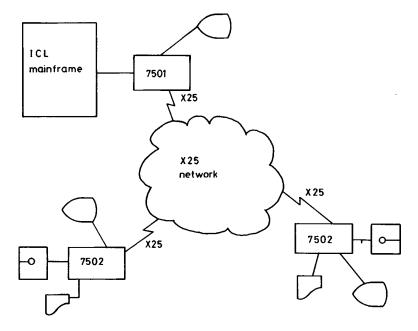

#### 4.2 Packet switching terminals

Packet switching is being adopted by many of the world's telecommunication authorities and the relevant X-25 protocol has gained equally wide acceptance. (There is a thorough discussion of the concepts and merits of packet switching, and of the relevant protocols including X-25, in the book by Davies *et al.*<sup>4</sup>) ICL has therefore produced new models of the 7501 and 7502 terminals for connection to such networks. These control all levels of X-25 and thus relieve the mainframe of any need for knowledge of the existence of the network. The implementation does not however include the possibility of polling across the network because this would bring in an expensive overhead.

The implementation is known as PSTS, meaning Packet Switching Terminal Systems. The terminals are already in use in France with the TRANSPAC network and will be available for connection to the British PSS when this opens. Implementations for other X-25 networks will be made available as the need arises.

Fig. 5 shows the X-25 connections with the 7501 and 7502.

Fig. 5 Packet Switching Terminal Systems, PSTS

# 5 Some user services

To show what this means at the practical user level, we now describe some of the main services to be made available under IPA.

The following is an example of an entirely realistic situation. User A, with a small machine and a terminal, has some data which he wishes to process by means of a program P running on a large machine M at a distant site to which he has access. This program will need to use some other data held in a file F at third site. He wishes to have the results printed out on his local printer and also to transmit them to user B at a fourth site, for up-dating one of his (B's) files. All these files, programs and so on are known by names to the participants and these are the only identifiers which A wishes to use in initiating the various activities.

The services to be described enable this kind of activity to be carried out as a routine matter. They are all implemented as software running under the main ICL operating systems VME/B, VME/K and TME. DME users also are catered for under the IPA umbrella, as they may assume the role of an 'associate' in an IPA community, so that a DME machine can act as a host providing a service such as MAC to the community. It is the adherence to the principles of IPA which makes it possible to provide the services in such a general form; that is, in standard forms which, so far as the user is concerned, are independent of the equipment and the communications system being used.

| The services are: | Remote Session Access (RSA)            |

|-------------------|----------------------------------------|

|                   | Distributed Message Router (DMR)       |

|                   | Distributed Application Facility (DAF) |

|                   | File Transfer Facility (FTF)           |

|                   | Application Data Interchange (ADI)     |

|                   | Range Remote Job Entry (RRJE)          |

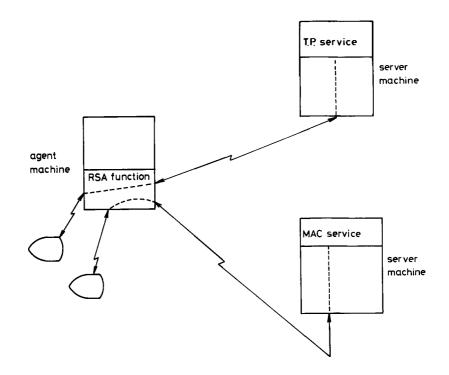

# 5.1 Remote Session Access (RSA) (Fig. 6)

This facility allows the user of a terminal connected to an IPA mainframe to access a service resident in another processor to which he is not directly connected. This is essentially a 'pass-through' facility which allows complete transparency through intervening machines to the required service. The link between the terminal user and the machine offering the service is achieved by the input of an appropriate simple message from the terminal keyboard.

An example of RSA in use might be when the terminal operator wishes to use a TP service which is not available on the machine to which he is directly connected. Once connected to the 'remote' TP service the operator is unaware that RSA is being used. Breaking the RSA link is as simple as establishing it; the terminal user then drops back to the machine environment to which he is directly connected.

In this type of organisation the machine 'passed through' is called the Agent and the machine offering the service is called the Server. The RSA connection is on a session basis, not message-by-message.

Fig. 6 Remote Session Access (RSA)

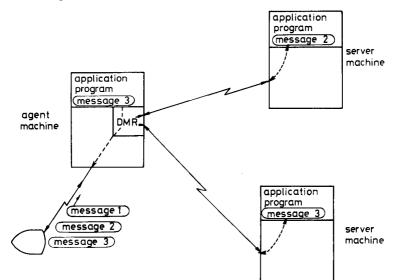

# 5.2 Distributed Message Router (DMR) (Fig. 7)

Some user input messages may relate to files or applications which are not available locally and which therefore need to be transmitted to a remote system for processing. Using DMR, any message input by the terminal operator will be examined for a destination indicator and routed to that destination, which may be the local or a remote mainframe.

This facility is of particular use where adjacent messages, for example in a stock control system, need to be processed against files or applications resident locally or in distant processors. DMR would be used to despatch the messages to the appropriate destinations. Once again the operator is unaware of this routing activity, except perhaps for a variation in response time resulting from the extra transmission delays.

Here, unlike RSA, routing activity is handled on a message-by-message basis.

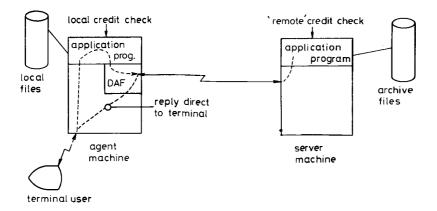

# 5.3 Distributed Application Facility (DAF) (Fig. 8)

This enables the processing of different tasks, or different parts of the same task, to be distributed amongst different parts of the system or network. A terminal oper-

ator may send messages to a particular application for which data is not available locally, or which requires treatment by an application residing elsewhere in the processing network. Without operator intervention or awareness the local application will arrange transmission of either the original message or an entirely different one, depending on the requirements, to the appropriate distant application through the use of DAF. When the distant application has processed the message it may reply to the originating application in the local machine or it can optionally reply directly to the terminal operator.

Fig. 7 Distributed Message Router (DMR)

Fig. 8 Distributed Application Facility (DAF)

An example is the request of a credit check for a customer whose account has been idle for some time and whose records have been archived in order to minimise

local storage requirements. The local credit check program recognises that the account is not held locally and accordingly makes the enquiry upon the files held at the central site. When the reply is sent back from the centre the message can go either first to the local application or directly to the terminal user.

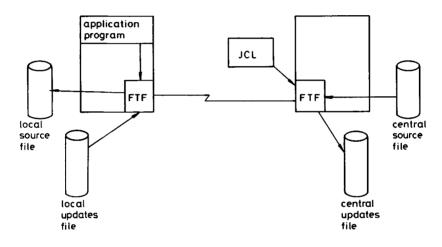

# 5.4 File Transfer Facility (FTF) (Fig. 9)

In conjunction with DAF, FTF will respond to commands in Job Control Language (JCL), for example from a terminal or from within an application program, to transfer a file between two systems.

An example might be the transfer of a summary of a day's local transactions at a branch office or shop to a central location for updating the central files. Another use of FTF could be the transmission of centrally developed source program files to remote systems for testing for local use.

Fig. 9 File Transfer Facility (FTF)

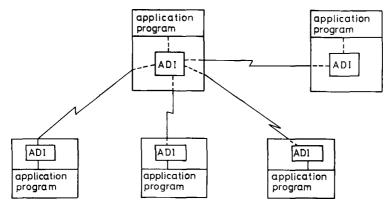

# 5.5 Application Data Interchange (ADI) (Fig. 10)

This is the facility whereby an application program in one computer can communicate with another program in another computer without involving TP control or software. It is particularly useful when a high level dialogue is required between two related programs which are not operating on a TP message/transaction basis.

An example might be an overnight run of an application program which gathers the accumulated data and statistics of the previous day's work from a number of remote systems. The central and remote programs would have an intimate protocol relevant only to themselves for gathering the data.

Alternatively, and perhaps more important, as ADI offers a transparent 'pipe' through which data passes, it can be used for connection to alien (non-ICL)

machines, when the interpretation of the incoming data can be handled by the application within the ICL mainframe. In this way it is possible to have a meaning-ful conversation at the application level with other manufacturers' machines.

Fig. 10 Application Data Interchange (ADI)

Fig. 11 Range Remote John Entry (RRJE)

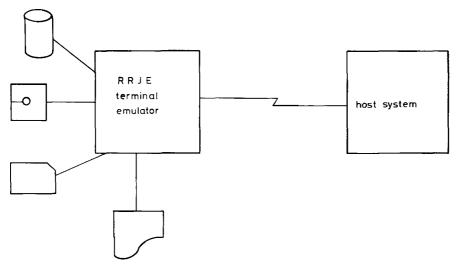

# 5.6 Range Remote Job Entry (RRJE) (Fig. 11)

The RRJE facility offers the ability to input work for processing, including source code, data and JCL, from a machine emulating an RJE terminal to a host system. Output from the host can be received and spooled by the emulating machine, for eventual printing.

An example could be the transfer of jobs from one IPA host to another. Using RRJE, the entire JOB envelope - that is, the JCL, the job itself and any other

relevant information – could be moved from one host to another, executed and the results then despatched to the appropriate site.

## 6 Concluding remarks

This paper is intended as a broad overview of IPA. We have aimed to bring out the fundamental nature of the principles on which the architecture is based, its power and generality and its scope for unlimited development. As will be clear, a great deal of technical detail is involved in its implementation; it is intended that later papers in this *Journal* will deal with some of this.

#### Acknowledgments

The authors wish to thank Mr. D.J.Williams of ICL Product Development Group, Bracknell, for his technical help and advice and Dr. J. Howlett the Editor of the *ICL Technical Journal* for his advice of form of the paper.

# References

- 1 HOULDSWORTH, J.: Standards for open network operation. ICL Tech. J., 1978, 1, 50-65

- 2 ANON.: Reference Model of Open System Interconnection (Version 4 as of June 1979). ISO/TC97/SC16/N227

- 3 BRENNER, J.: Using Open System Interconnection standards ICL Tech. J., 1980, 2 (1), 106-116

- 4 DAVIES, D.W., BARBER, D.L.A., PRICE, W.L. and SOLOMONIDES, C.M.: Computer Networks and their protocols, New York, Wiley, 1979.

# VME/B a model for the realisation of a total system concept

# **B.C.Warboys**

ICL Product Development Group, Northern Development Division, Kidsgrove, Staffs

#### Abstract

Almost a decade has elapsed since the foundations of the VME/B system design were laid. The paper is an attempt to isolate the fundamental initial design motivations. During the decade most exposure has inevitably been given to the extensive set of capabilities provided by the system. As a result the original motivations tend to be obscured by the, admittedly most important, facility discussions. It therefore seemed appropriate to restate the fundamentals uncluttered by details of such facility support. This may well cause disappointment to those who expect to find a facility overview within; however, I felt that a highly personal statement of the original design motivations would be worthwhile after such a long interval.

'The writers against religion, whilst they oppose every system, are wisely careful never to set up any of their own' (Edmund Burke).

No such precaution was taken by the author and in fact a decade has flown by since the lapse and this paper. The paper is both an attack on the then (1971) state of operating systems and an attempt to provide a positive response to that attack.

Inevitably when attempting to outline the initial design concepts for such a project after such a long interval there is some difficulty in separating current motivations from those of ten years beforehand. The paper is therefore somewhat of a mixture of history, present thoughts and future predictions. Apologies are offered for such self-indulgence; it is hoped that the reader will understand and forgive.

#### 1 Scope

The reader who perseveres will read about system concepts and motivations. Little or no mention is made of the extensive processing and support capabilities of the VME/B system. These are well documented in a series of ICL technical publications to which the interested reader is referred.

Thus there is little or no description of the scheduling mechanisms, the control language, the filestore or the virtual store. It is hoped that some future papers in this series will provide technical background to some of these areas.

The VME/B system is currently packaged and marketed as a large general-purpose system supporting the concurrent operation of batch, multi-access, remote job entry and transaction processing services. It is offered to support large ICL 2900 series systems.

## 2 Introduction

In any description of an entity it is useful to detail not only what it is but also what it is not. The classical view of a computer operating system 'to share the hardware which it controls among a number of users, making unpredictable demands upon its resources ..... efficiently, reliably and unobtrusively' is too narrow to enable a reasonable presentation of VME/B's objectives and philosophy. There are so many preconceptions about the components of an operating system and even more about what its functions should be.

Instead the paper reflects the basic thinking behind the original design intentions that the time had come (in 1971) to challenge the boundaries and dichotomies which had grown up around that mythical entity 'the operating system'; to challenge the concept of a single unit capable of satisfying the diverse needs of all users.

Well, so the King is dead: now what do we do? Clearly the first task is to examine the origins of any legend in order to understand society's dependence on it; to examine the divisions and boundaries that give shape to the legend and distinguish between those that have prospered through the lack of any formulation of theorems, those that reflect the constraints of recent knowledge and practice and those that exist through our present conception of the very nature of the system we are providing.

The paper thus attempts to gradually identify what was perceived as the users needs. It demonstrates that VME/B is not just a 'product' but a unified and comprehensive set of system concepts, design rules and functions. These provide the basis for the development and integration of ICL products of many types, both existing and new. The paper seeks to establish that the 'packaged' VME/B system as currently preferred is a particular usage of the design and thence to differentiate between module capabilities and their packaging, mapping and binding into marketed systems.

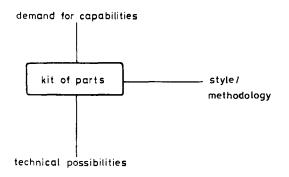

Any set of software capabilities must choose how to colonise the wilderness between the rich pastures of available technical possibilities and the forest of users' demands for capabilities.

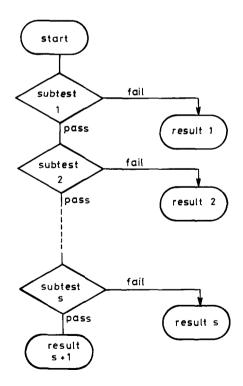

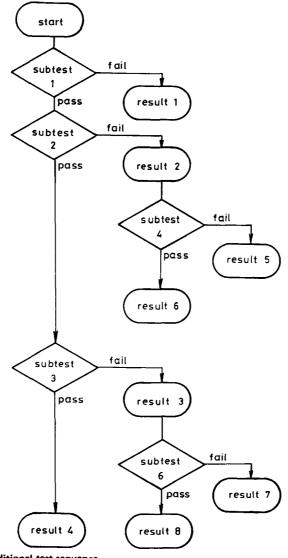

Such a colonisation requires the identification of the characteristics of the components, the style of their combination, and a supporting methodology allowing the flexible assemblage of components to provide the necessary application services (Fig. 1).

So what were the possibilities, what were the demands?

# **3** Technical possibilities

The sixties had generated a number of techniques:

structured programming, top-down design, procedures, capability machines, data-bases and communication protocols.

The architecture of the 2900 range had drawn from this base and had reflected the latest thinking into the structure within which module designers could begin to function. The 2900 architecture has been outlined elsewhere<sup>1</sup> and the reader is referred to such publications if further background reading is required.

From the viewpoint of the software module designer the architectural features which framed the basis for a sympathetic software implementation were as follows.

# 3.1 Architectural support for the procedure

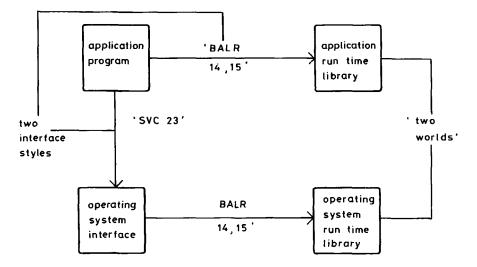

Historically the dichotomy between software packages, in particular those which had come to be known as the operating system and the applications system, had grown to such an extent that the concept of privilege had enshrined a single level boundary between the 'good' guys with wide capabilities and the 'bad' guys with narrow ones. The justification, probably after the event, was that one of the principal roles of the operating system was to hide the details of hardware from the application writers. In practice one highly stylised and complex interface had merely been replaced by another.

#### Fig. 1

The advent of high level languages and then of application data interfaces in fact presented the applications developer with a stylised high level interface which now required support from mapping code rather than an abstracted hardware interface. However few people had seemed to notice and a sharp distinction grew up between the mapping support provided by the 'run-time library' and that provided by the 'operating system'. The 360 architecture in fact provided two code-calling mechanisms something like 'BALR 14, 15' for library calls and something like 'SVC 23' for operating system calls.

Further, once within the operating system, it (the operating system) invoked procedures within itself using the library calling convention of BALR 14, 15. Thus three classes of procedures could be identified

- (i) User available library procedures (subroutines)

- (ii) Operating system interface procedures

- (iii) Operating system available library procedures.

#### Fig. 2

Not only did this enshrine for the system the level and structuring of support offered by the various libraries but also cut off general access to operating system procedures which were of potential value to the user. Since that time the growth of microcode machines has introduced a fourth level of library: that of the hardware-provided microcode-procedure library.

It was clear that if we were going to exploit to the full the opportunities presented by more flexible hardware machines, the new lessons of data management and the wide use of high level application languages such distinctions would only inhibit the freedom for flexible system restructuring to meet the challenges of the rapid evolution of computing theory, technique and hardware economies.

Thus 2900 offered a number of facilities which were specifically designed in order to ensure that such distinctions were not pre-ordained for the system designer:

- (a) The call (the procedure invocation) was a universal mechanism independent of the privilege and priority of the calling and called procedures.

- (b) The binding of a called procedure to its caller was accomplished by the 'insertion' of a pointer (a call descriptor) between the call and the target procedure. This 'insertion' could be delayed, if necessary, until call time

and it was this generalisation of binding mechanisms which offered real opportunities to rethink the mechanisms needed to flexibly assemble a variety of application services.

(c) The 'work-space' for a procedure was mechanised, by a hardware stack, such that all procedures could operate in the same way. This was clearly a prerequisite for the delayed binding of procedures into application environments. There was little point in delaying the classification of procedures into levels of privilege if the code body of such procedures was dependent on the level chosen.

In practice, for efficiency reasons most binding is performed at either system generation, system initialisation or module load time as part of the packaging of the product for field release.

Clearly the possibilities available through such a general technique could not be ignored in the resulting software system design.

# 3.2 Architectural support for virtual machines

Historically the other major distinction which had become cemented into systems architecture reflected the need for multiple users to access the computing service simultaneously. To support such access most machines implemented some form of base-displacement protection mechanism limiting access by a user program to a 'local' store plus a set of operating system interface procedures, i.e. the SVCs mentioned above were included in the base-displacement domain. This mapping did much to enshrine the concept of a 'program' as the basic user processing unit and hence encourage the development of monolithic application programs to fit into these highly stylised protection domains. Further since the user had no access to any form of concurrency apart from the 'program level' a plethora of tasking techniques evolved such as to enable the applications writer to have some access to parallel processing capabilities. The combination of the lack of distinction between the protection of tasks and shared variables within a program led to a number of rather complex parallel language definitions culminating in PL/1-like approaches. Such approaches placed considerable strain on the skills of the applications developer. Indeed since then a number of treatises, books even, have been written attempting to provide aids in mastering such complexity.

2900 offered the possibility of a more thoughtful and general approach to sharing and concurrency through the notion of procedure capabilities within virtual machine domains. However, it must be admitted that the further developments particularly in information processing theory have demonstrated that in the future wider generalisations are going to be necessary. These will basically derive from a better understanding of the nature of naming and relationships in information processing. However, it is already clear that the lifting of many of the artificial barriers has presented better opportunities for developing a coherent approach.

The virtual machine in 2900 is thus viewed as the assembly point for a set of capabilities to provide an applications service. The procedure base offers a flexible

mechanism for mapping real world objects into capabilities and the scene is set enabling us to look at the provision of a set of modules enabling the assemblage of highly specific application-processing services.

However, at this point, it is worth noting the constraints, implicit in our style of business, which were imposed by the large number of established commercial practices, especially since the manufacturers had in the first place been responsible for the establishment of these practices. These included the rather peculiar style of mapping required for FORTRAN and COBOL applications and in ICL's case the style of control language made familiar to users through the George 3 operating system. Thus the virtual machine needed to become a flexible localised container in which opportunities for rationalisations could be exploited whilst allowing familiar techniques to continue to be exploited. Indeed the current style of command language interface, deriving from the George 3 vocabulary, is likely to continue for at least another decade.

# 4 Capabilities

So what processing services are necessary and what style and methodology is required to provide the framework for such services? To answer this question we must look at the pressures which were growing within the industry which in turn were dictating these requirements. There were two basic areas of pressure, one deriving from the economics of application software development and one from the technological developments in the science and practice of the industry.

# 4.1 Application development

From the viewpoint of the computer user striving for a cost-effective applications service there appeared to be three problems which were of particular concern and where an increased application of software engineering principles could be of immense benefit to him.

- (i) Program duplication duplication in his own programming because of ignorance of the work of others, differing languages, change of computing system or partial change of requirements, and duplication of system support software, which in the final analysis he has to pay for.

- (ii) The poor design and implementation of the images presented to the user and their irrational variation from one application to another.

- (iii) The management of large application program suites getting them written, used and maintained.

# 4.2 Technology development

From the state of the industry a number of pressures were arising and these can broadly be divided into the three areas of Hardware technology, Information technology and System and Information theory.

# 4.2.1 Hardware technology:

- (a) Processing power. The cost of hardware was reducing rapidly which generated the twin challenges of the effective utilisation of more power by the competent user and the utilisation of a powerful system by an increasing population of non-professional users.

- (b) Accessible storage. Most social and business revolutions have derived from the ready availability of an enlarged information base. The huge explosion in the amounts of accessible storage over the last decade and its even greater explosion in the next posed problems of distributed databases, friendly interfaces and rapid access and protection of very large information banks. Clearly an approach to filestore, database structure and naming was required that both coped with existing skills and practices but at the same time left the door open to deal with new vastly different demands.

- (c) Novel machines. It was becoming clear that the general purpose machines prevalent in 1971 would rapidly be complemented by a whole 'mish-mash' of special purpose engines. The ICL DAP and CAFS machines are already available and there are a number of 'Reduction' machines which have demonstrated the potential of very high and functional programming languages as directly executable languages. Clearly the system partitioning and hardware mapping would have to take account of this aspect.

- (d) Networks. The network business was taking off spurred on by a number of influences:

the growth of distributed processing in the market place;

the demands to interlink data-processing systems and components in a flexible way;

the mutterings about automatic offices and electronic mail.

Clearly no longer could communications facilities be treated as add-on goodies to a batch processing service; an integrated approach to both centralised and distributed processing was required. See for example the paper by Kemp and Reynolds<sup>2</sup> on the recently-released ICL Information Processing Architecture, IPA.

4.2.2 Information technology: File organisations had arrived, indexed sequential, keys, records, were accepted jargon. The CODASYL work and the work of  $CODD^3$  were producing implementations of management information systems with immense scope and potential. There was clearly a need both to absorb the lessons on naming conventions, data structuring and relational theory and to produce solutions which allowed freedom of evolution of the applications database independently of the applications suite. In particular many applications would for the first time be changing from tape-based unconnected file-processing approaches to disc-based interconnected integrated management-information systems.

4.2.3 System and information theory: It was the era of 'modularity' – the need to get rid of monoliths and move to off-the-shelf interchangeable applications modules together with a style and a methodology for packaging such modules.

# 4.3 Summary of required capabilities

- (i) Cost-effective applications development environment, in particular the availability of modular programming support techniques

- (ii) 'Synergetic' man machine interfaces

- (iii) Exploitation of very large information bases and current information theory

- (iv) Exploitation of 'novel' machines

- (v) Exploitation of distributed systems

# 5 Response

## 5.1 Recap on the story so far

The paper has thus far attempted to outline the three main areas of influence.

- (i) The existence of historical boundaries and the opportunities offered by the 2900 architecture as a basis for a more flexible approach to technological possibilities.

- (ii) The challenges presented by a whole new set of technological possibilities.

- (iii) The demands for capabilities from an often embittered user population.

The rest of the paper is an attempt to demonstrate the extent to which the system style has grasped these opportunities and challenges and gone some way to understanding how much of operating system sentiment was fact and how much fiction.

# 5.2 Functionally-oriented environments

Earlier the paper had identified that the set of capabilities which were needed effectively demanded a style, a set of mechanisms for easing the lot of the developers of applications systems. It had identified that historically monolithic applications development had derived from two main sources.

- (a) The widespread classification into two worlds operating system and application program.

- (b) The lack of support for modular program development systems.

It then identified the basic elements of the 2900 building style, that is, procedures and virtual machines. Particular emphasis was given to the concept of delayed binding of procedures to support the mapping of a set of real-world entities into a set of functionally oriented environments existing within the boundaries of an architecturally supported Virtual Machine. Further in performing this mapping we did not wish to reintroduce unnecessary boundaries but rather allow as much freedom as possible in the selection of procedures to support a given set of applicationprovided packages. The final requirement was clearly to then provide a generalised

#### ICL TECHNICAL JOURNAL NOVEMBER 1980

.

naming and control structure allowing the flexible assemblage of procedures to present the required application images.

In order that such environments could freely exist it was necessary to ensure that:

- (a) we were not building interpreters on top of interpreters and thereby creating systems with a certain hierachic elegance but very poor performance;

- (b) the maximum use was made of defaults and naming contexts in order to localise identifiers;

- (c) once packaged environments had been established they would be re-used (inherited) in order that the minimum amount of time was spent in creating the tailor-made environments. Clearly the object of the exercise was the execution of work in such environments rather than their initial establishment.

- (d) the mechanisms for the building of a set of 'user-friendly' interfaces were freely available. We took the view that no single definition of user-friendly was likely to serve the needs of all users. Further the state of the industry was such that the definition of 'friendly' was likely to evolve rapidly in the next two decades or so.

The approach taken to ensuring that such objectives were indeed satisfied was:

- to provide a single naming system within which all real-world objects could be described, the relations between them could be specified and a set of local (i.e. environment specific) 'currencies' could be used to access such objects once they had been mapped ('selected') from the real world into the processing environment; see section 5.3.5 for further explanation;

- (ii) to allow such currencies to identify (and hence directly invoke) primitives which were needed to support the environment and hence avoid the need for intermediate interpreters;

- (iii) to provide a block-structured scoping system allowing both the re-use of tailored nested environments and to ensure that such environments were tidily deleted when no longer required. The system adopted was very similar to that used for variables in any Algol-like language. However, all real-world entities when mapped through the naming (and thence procedural support) system were subject to the same scoping rules;

- (iv) to provide a 'profile' system allowing for the establishment of a variety of human input command languages which controlled the assembling and thence execution of the set of procedures required to support a given application.

Note that in all of the above there has been no necessity to distinguish between the providers of procedures. We shall however, identify functions which need 'public' access (and hence privilege) in order to support this model. It is such functions which help to identify the classical operating system functions which are 'real' and those which evolved through habit or manufacturer's policies.

Notice also that, as yet, no real mention has been made of the mapping of information and programs onto storage. Indeed this paper will not attempt to describe the various sophisticated techniques which are needed to ensure an effective utilisation of file storage and main store. Clearly much of the system implementation was and is concerned with this mapping but this is seen as of secondary strategic importance to the basic concepts outlined above. Indeed it was imperative that with the rapid evolution of storage technology the mapping of the storage hierarchy should be flexible and distinct from the support given to the general system structure.

### 5.3 Basic system principles

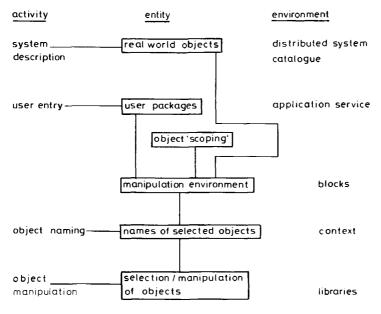

Thus the system was viewed in concept as supporting four basic activities.

- (a) System description involving the description of all of the named objects required to be accessed by the various users and managers of a distributed computer system. Note no distinction has had to be made between operator, system manager, programmer or application user. This system description may turn out to be distributed throughout a network and indeed encompass a variety of different naming systems and standards.

- (b) User entry involving the creation and management (and thence deletion) of an environment tailored to meet the demands of this particular user within a set of installation defined user types.

- (c) Object naming being the mechanism required for the provision of a local view of the generic system description. In particular in a distributed network it was considered of primary importance that the user was given a consistent and personalised way of naming an object independent of the controlling system managing the object.

- (d) Object manipulation once an object had been named, the user needed a local 'currency' guaranteeing his required private access which when subsequently used to manipulate that object would police its conformance to the behaviour which he had established for it (rather like the concept of types, classes and monitors).

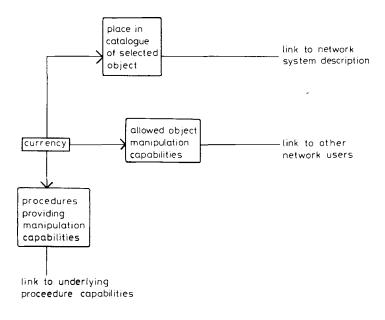

Fig. 3 outlines the entities and environments which support these basic activities.

5.3.1 Loading: Before more detailed analysis of these basic system activities there is one point worth reiterating. The basic 2900 approach has been viewed as providing mechanisms for the translation of any activity into a set of procedure capabilities. Clearly the procedures provided from a number of sources are themselves named objects. Thus when visualising named objects one should remember that the procedures supporting them are included in that set. In other words the system is basically providing mechanisms for name translation and the naming system copes both with the naming of primary objects (e.g. users, files, devices) and their supporting derived objects (e.g. procedures, events, data areas). The process of providing named procedures to support object selection and manipulation is known as 'loading'. Thus basically whenever a user names and then manipulates an object the system 'dynamically' provides the named procedures for supporting these opera-

tions, hence the importance of the delayed binding and run-time privilege classification mechanisms outlined earlier.

As noted earlier the system generation (packaging) process can of course preload to optimise the process for identified packaged requirements. In fact VME/B, currently marketed as an 'Operating System' product, is mostly packaged this way at present.

# Fig. 3

5.3.2 System description: To support a complete description of a set of named objects the concept of a names catalogue was introduced. As a design statement the catalogue was not dependent on any processing centre of a distributed system and indeed might appear in several such centres. It is organised in terms of nodes and relationships. Entries for named objects are located at *nodes* and the nodes are connected by *relationships*. For example a file node is connected to a volume node by a placement relationship.

Privacy relationships define access rights and in particular control the translation (mapping) possible between objects and the implied support procedures. Thus rather than provide a rigid partitioning between operating system capabilities (functions) and user-provided procedures the system provides, through the loader and catalogue mechanisms, a general capability for establishing as part of a system description the mapping between objects and the privilege, priority etc of the underlying and often implied support procedures. Clearly once we have established a global, protected loading and cataloguing system we can generate secure systems.

5.3.3 User entry: User entry to the system is viewed merely as the 'selection' of a user node. Clearly as a result of such a selection the implied support procedure

(normally referred to as LOGIN) can select required (allowed) processing environments and required (allowed) manipulation facilities. The capabilities (provided through named procedures) reflecting the installation's view of this particular user's needs and competence.

However, more is required. The original objective was to hide the complexity of translation between the user's view and the generic description of the network. Further in an 'open' system one might expect to see several different underlying network views and indeed (with the advent of CAFS, DAP and other novel machines) different types of processing capabilities. Thus the system provides two other basic mechanisms:

- (a) implicit 'loading' and thence 'unloading' of capabilities. This is accomplished as mentioned earlier by giving scope to all loaded capabilities and selected objects. The system adopted was the simplest. That is a blockstructured system such as is used to control variables in ALGOL 60. Most 'loading' is implicit since the system objective was to provide the user with access to named objects and the underlying support procedures vary according to the hardware supporting any application. Clearly the support procedures required for mapping to an array processor are different from those required to support a conventional machine.

- (b) re-use and sharing capabilities. Clearly the establishment (binding) of procedures to support each and every named object takes a great deal of processing time but once established many environments rarely alter (e.g. a cash dispenser terminal in a banking network). Hence the system supports the concept of multilevel sharing and re-use of environments. This allows the installation to produce (system generate) a set of prepackaged environments with selected capabilities; the previously mentioned LOGIN procedure then merely has to link to the appropriate member upon user entry to the network.

5.3.4 Object naming: The paper has so far merely established a general mechanism for naming objects within a network and providing a tailored environment for their subsequent processing. Clearly the user having been presented with a tailored processing environment now needs to access objects using purely local terms. He does not wish to understand other people's naming system nor indeed to know all the names and naming structures in the universe. Thus the system provides a context mechanism. This can be viewed as the glue necessary for relating a purely local name to a fully qualified name within the network catalogue(s).

Thus a series of translation tables are provided allowing the user to gain coherent access to the naming systems within the network and thus to gain independence from any given processing node's naming structure. In a world of ever increasing open system interconnection and thence rapidly expanding information bases it is imperative that the necessary mechanisms be provided for the user to have a single coherent naming system.

5.3.5 Object manipulation: We have now provided the mechanisms for users to select objects into a tailored personalised processing environment. What remains is

to provide processing capabilities. The naming of an object is not the end of the matter; clearly one needs mechanisms for describing the 'correct' behaviour of any entity processing that object. Thus in order to identify the specific selection of a named object for a specific purpose a system of 'currencies' was introduced. A currency is a local pointer to a specific object selection. It thus acts as a 'bookmark' remembering where this user has accessed the catalogue. It further acts as a description of the permitted accesses (including other people's right to concurrent access) afforded by a particular selection or series of selections. And lastly it gives the route to the 'possibly implicitly' loaded procedure capabilities that give the facilities for manipulation of the selected object.

Thus as an example a user may select a real file and thence a file manager and thence a record. The combination of file, processing agent (i.e. access method), file position and processing buffer resulting in a record currency. In the case of a serial file therefore repeated usage of a record currency might always yield 'the next record' into the processing buffer.

Clearly the support of such currencies is undertaken by a whole series of procedures specifically designed to support a set of required processing capabilities. The set is infinite and the role changing as the hardware interface moves and as the definition of the object types and operations required to support networked information processing is developed.

5.3.6 Applications development: The model established so far has only dealt with naming, name translation into procedure capabilities and environment provision. In passing it has dealt with the demands generated as a result of wishing to exploit

the capabilities of distributed systems and novel machines. It has as yet not sought to specifically satisfy the demands for synergetic man-machine interfaces and cost-effective applications development environments. The model has however identified the mechanisms for the provision of such processing environments and the underlying support necessary for the implicit 'loading' and 'unloading' of the supporting procedure based capabilities.

What additional capabilities are required to support these other demands? Basically the system design took the view that there was little to choose between the requirements necessary for basic system structuring and those required for application structuring. That is to develop applications as a set of modular capabilities, to allow for the flexible assemblage of such modules into services, to provide the mechanisms to create and thence re-use packaged environments and to provide maximum transparency of required capabilities to the end user. The list of requirements is the same as has been identified earlier. Thus the capabilities:

- (a) to extend the catalogue system description;

- (b) to extend environment packaging user entry;

- (c) to extend the context mechanism object naming:

- (d) to extend the currency (procedure capabilities) mechanisms object manipulation,

provide the basics for modular applications development. The capabilities are augmented by a System Control Language<sup>4</sup> which reflects

- (a) the block-structured scoping of objects;

- (b) the procedure-based capabilities system;

- (c) the need to provide a single language for all applications binding since we have not distinguished types of user as a basis for system design but rather as a packaging requirement;

- (d) the need to combine application modules, system procedures into processing services and hence provides good communication (e.g. variables) facilities;

Thus one can see that the control language is not an 'add-on goody' but rather a continuous extension of the basic system concepts.

### 6 Conclusion

The paper has attempted to identify the causes of monolithic and expensive operating system development and thence monolithic and expensive applications development. It has then identified what the VME/B design identified as the four main system concepts necessary for the support of both distributed and modular system developments. That is, system description, user entry, object naming and object manipulation. It has not discussed many things including concurrency, filestore or hardware management. That is not to say that these are not important, in fact, of course they are the essence of what one might term the operating system procedures contributions. The reader will, one hopes, see that the provision of such manipulation capabilities is secondary to the provision of a coherent naming and

processing capabilities system and indeed that the implementation of such manipulative functions will rapidly evolve as the economics of system construction change over the next decade.

# Acknowledgments

Thanks are due to many people: Di Turner for painstakingly preparing the document, Jack Howlett for bullying me into writing it, Peter Wharton and Barry Hopewell for providing inspirational notes, all the members of OSTECH, past and present who provided me with such splendid design support during the past decade, the members of 2900 OSS, past and present, who turned designer's dreams into product realities and finally to those in other areas of ICL who have dealt with the consequences of these product realities.

## References

- 1 BUCKLE, J.K.: 'The origins of the 2900 series', ICL Tech. J. 1978, 1, 5.

- 2 KEMP, J. and REYNOLDS, R.: 'The ICL Information Processing Architecture IPA' ICL Tech. J. 1980, 2(2).

- 3 CODD, E.F.: 'Normalised data base structure', IBM report RJ935, 1971.

- 4 BRUNT, R.F. and TUFFS, D.E.: 'A user-oriented approach to control languages', Software practise and experience, 6, 93, 108.

# Birds, Bs and CRTs

# I.D. MacArthur

#### ICL Communications System Segment, Northern Development Division Kidsgrove, Staffs

#### Abstract

Nowadays it is popular to criticise Visual Display Units (VDUs) as a possible hazard to their operators. ICL is well aware of the concern in this area and this paper presents the views of one VDU designer. Cathode Ray Tubes (CRTs) have been around for more than 70 years and have been used for data display since the earliest days of computers. It is the author's considered belief that we shall be living with them for many years yet.

The purpose of this paper is to spell out some of the basic facts of VDU design which apply to all VDUs made by all manufacturers. In this way it is hoped to present in a compact form some of the facts which affect the appearance of the VDU screen. It must be stressed at the outset that there are very few absolute truths in the design of VDUs; most of the decisions are subjective and there are few standards to guide the engineer. The main sections of the paper deal with operators and their needs, VDU design, physical CRT parameters and safety and health.

The Bs are all around us: Business – Big Business – Brothers – Big Brothers – Breadwinners – Boredom – Backache. The Birds are of course our delightful operators.

#### 1 The operator

The whole purpose of a VDU is to communicate something speedily to an operator. VDUs do this by displaying alpha-numeric characters and sometimes graphics on the face of a CRT or other device.

If the operator is totally absorbed in the task of debugging a program, designing a bridge or taking over a company then past experience suggests he or she is unlikely to complain about the VDU. However, as VDUs are applied to more and more mundane tasks with less job interest, a bored office person is likely to find fault with her environment and colleagues. I think it is the growing penetration of VDUs into office work that makes them currently a target for criticism.

As a VDU designer I feel obliged to attempt to deflect the operator's wrath from the VDU and redirect it where it properly belongs – against the furniture, canteen facilities, air conditioning and management shortcomings in general. To this end it is a good idea to study the operator's vital statistics and make sure that the VDU is designed to harmonise rather than conflict with her needs.

This subject has been very well researched and a recent report<sup>1</sup> is recommended to the reader who wants more detail. A good summary is also provided in another report<sup>2</sup> which gives general recommendations while omitting much of the detailed background.

It must be stressed that even the best VDU in the world can be rendered unusable if badly installed, particularly in its siting relatively to windows and lights. The design of desks, chairs and office equipment generally is well covered in the above reports.

Whilst most of the operators' requirements are well covered, a few points relating to the design of VDUs are worth considering.

# 1.1 Environmental needs

Apart from the visual factors already mentioned and the usual office environment considerations of temperature, humidity and ventilation, there are one or two points concerning VDUs and their operators.

(a) Noise: Although VDUs are nominally silent it is surprising how much noise a proficient typist can make on a 'silent' keyboard. Whereas this may be quite insignificant in a computer room or in a 'data prep' area, it can cause annoyance in a very quiet office. It should be realised however that the quietness of a keyboard is related to its feel, and a very quiet keyboard may feel soft and lack a positive tactile response — one of the many compromises in VDU design must be invoked here. The same applies to fans, which can range from the Kiplingesque to the miniature RB211.

(b) Cooling: Fans have been mentioned and are generally an unmitigated nuisance. A blast of hot air in the face from a neighbouring VDU will usually result in retaliatory action. The experienced operator can usually overcome this particular problem by sticking some paper over the air outlet with selotape: the reader is left to guess what that does to the internal temperature of the VDU.

All electronic equipment dissipates heat to some extent and the 100W or so from a typical VDU can normally be handled by convection. For comparison, a human body also dissipates about 100W.

It is clearly good design to run equipment as cool as possible and to this end adequate ventilation must be provided; but care should be taken to see that warm air is directed away from the operator.

# 2 VDU design

# 2.1 Character shapes and sizes

It is generally accepted that the optimum size of character for viewing subtends an angle of about 20 min of arc corresponding to a size of 3 mm when viewed from a typical distance of 600 mm (2 ft).

Johann Gutenberg is reputed to have invented printing with moveable type about 1448 and printers have been perfecting the technique ever since. It would therefore seem reasonable to assume that after more than 500 years development, printed characters have achieved acceptable proportions. A number of modern type fonts have been analysed (see Appendix A) yielding the quoted proportions, which I believe represent the optimum for viewing by today's operators. Similarly various printed texts have been analysed to yield optimum line spacing (see Appendix B).

From these analyses it would appear that the CRT screen should accommodate a display width of about 240 mm and a height of 160 mm for 25 rows of 80 characters.

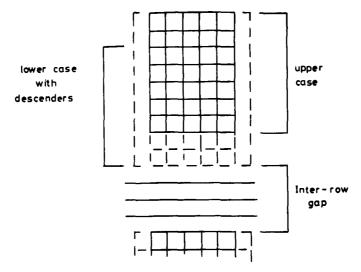

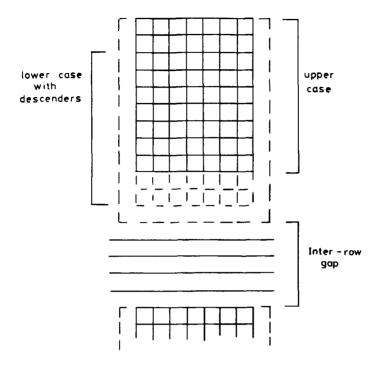

These figures are in good agreement with what is achievable on a 15 in diagonal CRT. A 12 in CRT is obviously useable, but will need a closer viewing distance. Fig. 1 summarises the optimum dimensions.

Fig. 1 Optimum character parameters

$$\frac{H}{w} = 1.63 \frac{H}{h} = 1.49 \frac{d}{h} = 0.43 \frac{S}{H} = 1.9 \frac{t}{H} = 0.13$$

### 2.2 Scanning of character generation

Let us now turn our attention to how such screenfuls of data are to be generated. Unless storage tubes are to be used it is necessary to refresh the display. This means scanning the same data repeatedly so that it appears as a steady flicker-free picture – more on this anon.

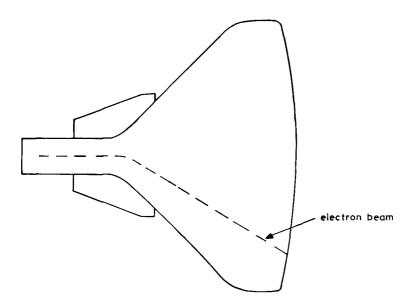

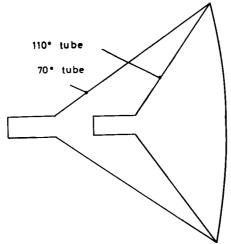

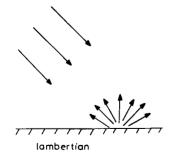

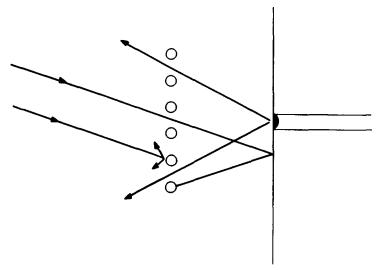

Fig. 2 shows a simple representation of a magnetically deflected CRT such as used in virtually all modern VDUs. Since a CRT generates only a single spot of light, characters are generated by deflecting this spot using magnetic fields. There are four well established techniques for doing this.

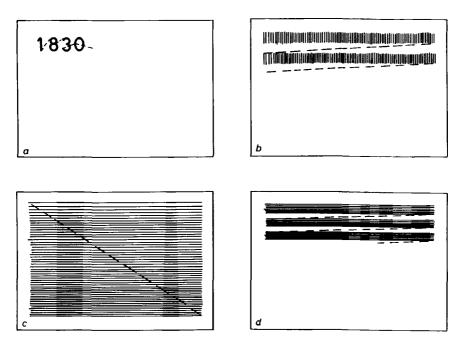

The oldest, most versatile and unquestionably most expensive technique shown in Fig. 3a is the cursive drawing where the electron beam is deflected around the outline of each character. This technique is widely used in large graphical and radar displays. It is capable of very good results but is unlikely to be seen in a display costing less than £20,000.

Fig. 2 Magnetically deflected CRT

Jiggle scan (Fig. 3b), where the beam is deflected very quickly to scan the character position combined with slower vertical and horizontal scans, is capable of providing a very good display at moderate cost. In the early days of VDUs this scanning technique was much used largely because it required a store access every  $10 \,\mu s$  or so, which was easily obtained using delay-line techniques. Nowadays, the availability of faster semiconductor stores and the cost of the additional scanning circuitry have largely caused the jiggle scan technique to be superseded by raster scan displays.

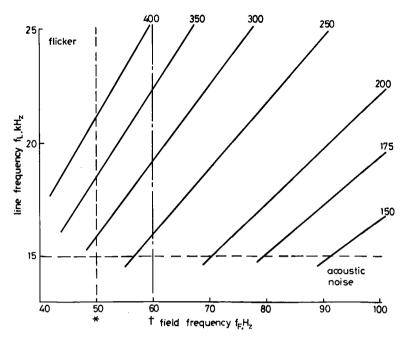

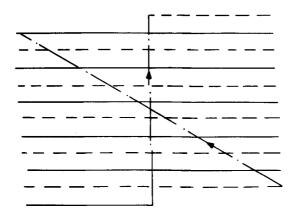

All television (TV) sets use the raster scan (Fig. 3c) where the electron beam is deflected by two continuously running scanning circuits normally called the *line* and *field* scan circuits. The line circuit usually deflects the beam horizontally while the field deflects it vertically. I shall have a lot more to say about line and field frequencies, but for the moment it suffices to say that European TV uses a line frequency of 15625 Hz and a field frequency of 50 Hz.

A development of the raster scan is the step scan raster (Fig. 3d) where the vertical scan is not uniform but speeds up between rows. Since the amount of speed up can be adjusted, it is now possible to adjust the character height independently of overall height. Table 1 summarises the pros and cons of raster and step scans.

Fig. 3 (a) Cursive scan (b) Jiggle scan (c) Raster scan (d) Step scan

## 2.3 Character generation

Fundamentally a CRT screen is a matrix of possible display dots – something like  $\frac{1}{4}$  million of them and each one must be scanned *at least* 50 times per second, allowing less than 100 ns for each dot.

We therefore have a number of interrelated parameters to work with.

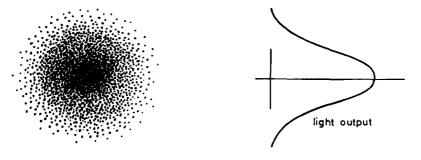

- (a) CRT spot size and amount of defocussing

- (b) Scan line spacing

- (c) Number of dots in the character cell

- (d) Number characters on the screen

- (e) Line frequency

- (f) Field frequency

- (g) Acceptable character quality

- (h) Acceptable cost.

(a) Spot size: If the spot size is too large then it will be difficult to read the characters - especially some lower case ones. If the spot size is too small the character will appear dotty and unpleasant to the eye. If the spot size varies much from one part of the screen to another, again the eye will notice this and be distracted.

# Table 1 Raster scan pros and cons

|                       |       | Pro                                                                                                                |                           |   | Con                                                                                                                                                                               |

|-----------------------|-------|--------------------------------------------------------------------------------------------------------------------|---------------------------|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Low cost              | _     | 50 years or so development of TV has<br>eroded the costs of the components<br>to rock bottom.                      | Timing                    | _ | as the line scan frequency is increased this timing<br>gets more difficult owing to the energy recovery<br>circuits' limited speed.                                               |

| Low power             | -     | since the scans are repetitive and of<br>constant amplitude it is normal to use<br>energy-recovery drive circuits. | Coarseness                | - | the TV lines are fixed distance apart tending to produce dotty characters on the screen.                                                                                          |

| Compatible            | -     | provided line and field frequencies are<br>equivalent a data display can also display<br>TV pictures.              | Fixed character<br>height | - | since a finite number of lines must be<br>allocated to each row of characters and also to th<br>inter-row gap, a compromise between spacing and<br>character height must be made. |

| Trans <b>missio</b> n | -     | well established waveforms for transmission by single coaxial cable.                                               |                           |   |                                                                                                                                                                                   |

| Interlace             | -     | can be used but beware of flicker.                                                                                 |                           |   |                                                                                                                                                                                   |

| Step scan pro         | s and | cons                                                                                                               |                           |   |                                                                                                                                                                                   |

|                       |       | Pro                                                                                                                |                           |   | Con                                                                                                                                                                               |

| Adjustment            | -     | adjustment of character height allowing                                                                            | Cannot                    | _ | display TV pictures or contiguous graphics.                                                                                                                                       |

|                       |       | increased matrix size, e.g. 9 x 7 or greater.                                                                      | Incompatible              | - | cannot be displayed on standard TV monitors.                                                                                                                                      |

| Fransmission          | -     | can be transmitted by coaxial cable just<br>like conventional raster.                                              | Cost                      | - | more expensive than raster scan adding perhaps 5% to cost of scan circuits.                                                                                                       |

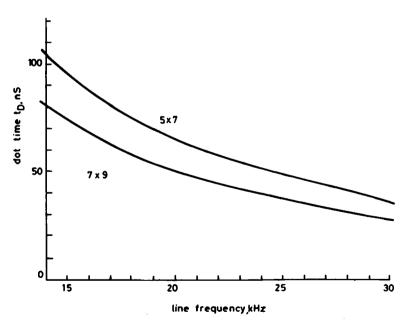

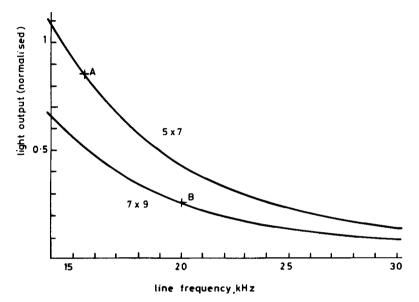

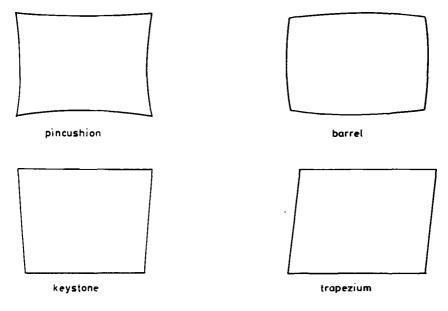

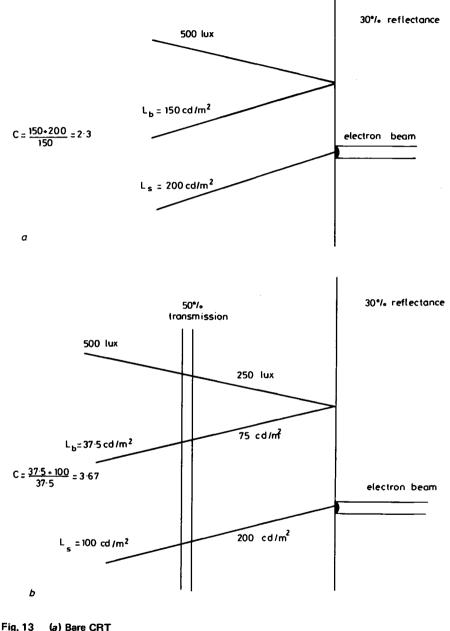

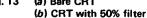

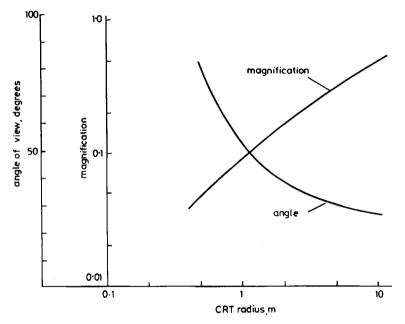

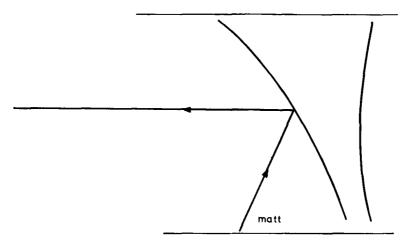

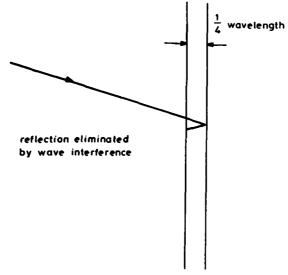

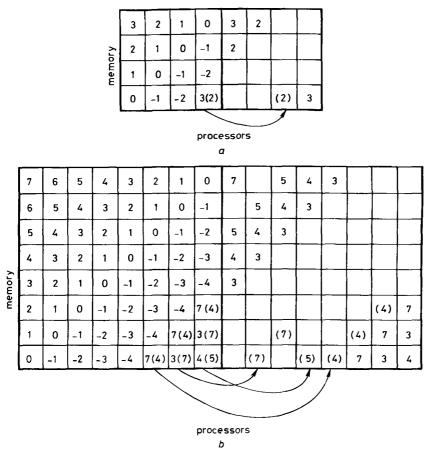

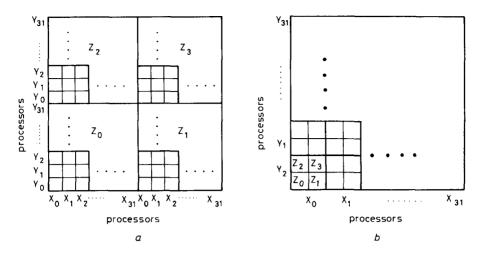

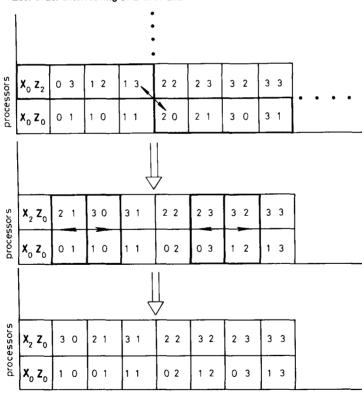

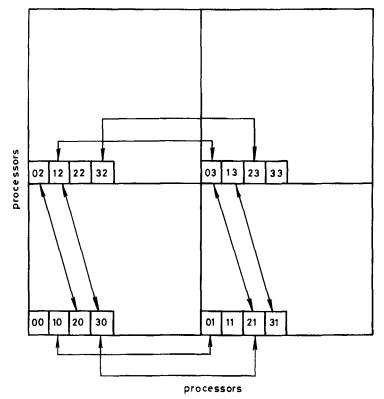

| Better display        | -     | display quality is noticeably better than for raster scan.                                                         |                           |   |                                                                                                                                                                                   |