# Limiting the Propagation of Errors in One-Bit Differential CODECs

By J. C. CANDY

(Manuscript received March 27, 1974)

An improved delta modulator is described that communicates to the receiver changes in the magnitude of the signal instead of changes in the amplitude. It is shown that propagation of errors in this system is limited, even when digital accumulators without leakage are used for integration.

#### I. INTRODUCTION

A major factor in the design of differential codes is achieving rapid recovery from transmission errors. Traditionally, low leakage in analog integrators has allowed error signals to decay with a defined time constant. We describe here another method for curtailing the propagation of errors, one that is well suited for use with digital integration. Digital integration<sup>2-4</sup> is attractive for differential codes constructed of integrated circuits. It allows the conversion to analog format to be left to a late stage of signal processing, thereby avoiding the need for high-grade amplifiers and carefully matched pulses, and enables signal amplitudes to be companded by appropriate design of the digital-to-analog (D/A) conversion network.

Introducing slow linear leakage into digital integrators is inconvenient. Indeed, leakage is often undesirable because perfect integration has an advantage of its own, once the effect of circuit and transmission faults has been contained.

Reference 2 demonstrates how a periodic clamp or an overload of the integrator corrects errors, but neither of these methods is suitable for use with speech signals. The proposed method is a simple one; instead of signaling changes of *amplitude*, the coder merely signals changes of *magnitude*. This small modification causes errors to fall quickly to zero. It has application to a variety of codecs, being especially well suited for delta modulators and related 1-bit codecs used for

transmitting speech. Application to multibit differential codecs is somewhat restricted.

# II. DIFFERENTIAL CODECS INCORPORATING DIGITAL INTEGRATION

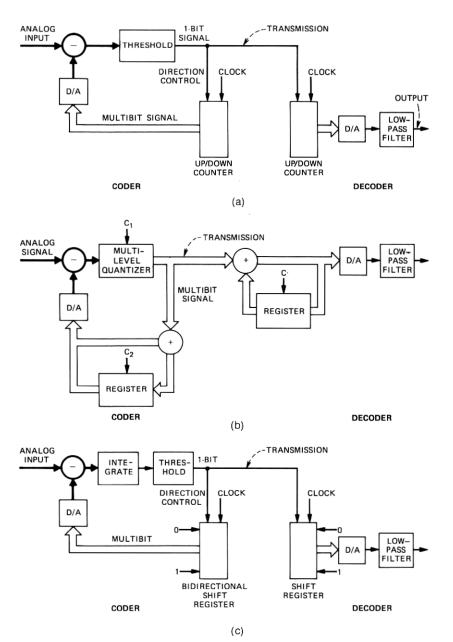

There are several ways of providing digital integration for differential codecs; Fig. 1 shows three methods. The first is a delta modulator that uses an up-down counter.<sup>3-4</sup> The second is a multilevel differential codec that uses a conventional accumulator,<sup>2</sup> comprising an adder and a register. The third is an interpolative codec<sup>5</sup> that uses a bidirectional shift register. If this register is fed 1's at the lower input and 0's at the upper, the entire contents shift up or down during each cycle, in response to the output of the threshold decision circuit. Details of this third circuit will be discussed in a later paper.

It is clear that a transmission error or inaccurate start-up procedure in any of these circuits can result in permanent mistracking of the transmitting and receiving integrators. Such mistracking may not be very serious for uniformly quantized signals, but when the D/A conversion levels are companded, mistracking would be catastrophic. Logarithmically companded magnitudes are useful for transmitting speech, and they are easily obtained by means of the circuit in Fig. 1c.

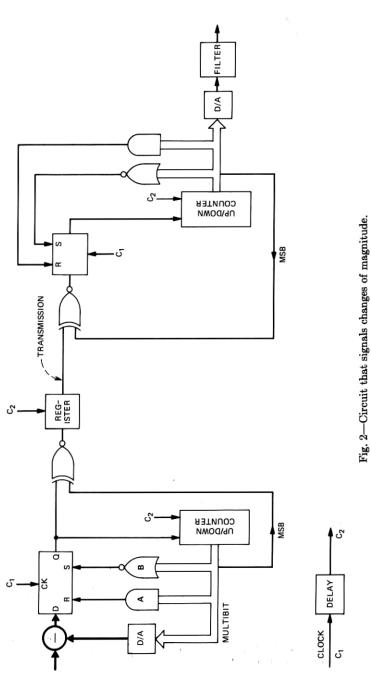

Figure 2 shows a codec modified to communicate changes of magnitude: Whenever the most significant bit in the counter is 0, the code is inverted for transmission. The code is reinverted at the receiver under control of the most significant bit of the receiving counter. Notice that for symmetric signals, such as speech, the most significant bit indicates the polarity of the signal, and the remaining bits describe its magnitude, negative magnitudes being in 2's complement format.

The circuits in Fig. 1 do not explicitly show the means for protecting the digital integrators from overflowing, but such protection is needed to prevent serious distortion of very large signals. Figure 2 incorporates two gates, A and B, that detect when the counter is full or empty. Their outputs inhibit threshold decision that would cause over- or underflow.

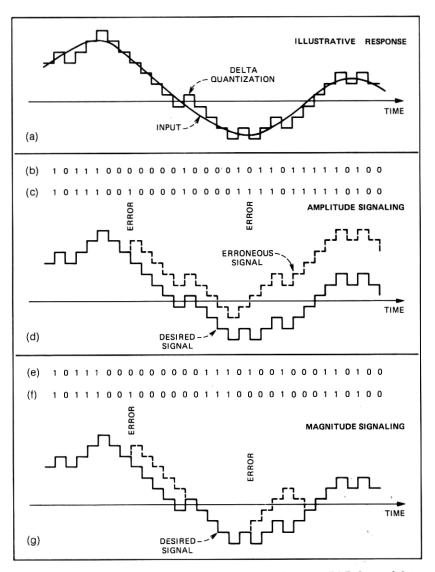

Figure 3 contrasts the responses of the circuits in Figs. 1a and 2 when transmission errors occur in the eighth and the nineteenth cycle. Permanent mistracking can occur when amplitude changes are signaled, but the errors quickly disappear when magnitude changes are signaled. The speed of recovery depends on the frequency of zero crossings of the input signal: A single positive error is wiped out when the signal would have crossed through zero going positively, or when the erroneous signal crosses zero going negatively. Zero crossings in the other direction correct negative errors.

Fig. 1—Differential codecs employing digital integration. (a) Steps are counted in a delta modulator. (b) Steps are accumulated in a differential codec. (c) A shift register stores 1's in an interpolative codec.

1670 THE BELL SYSTEM TECHNICAL JOURNAL, OCTOBER 1974

Fig. 3—CODEC responses. (a) Representative input and output. (b) Delta modulator code. (c) Delta modulator code with two errors. (d) Delta modulator responses. (e) Code that signals magnitude change. (f) Code with two errors. (g) Output waveforms.

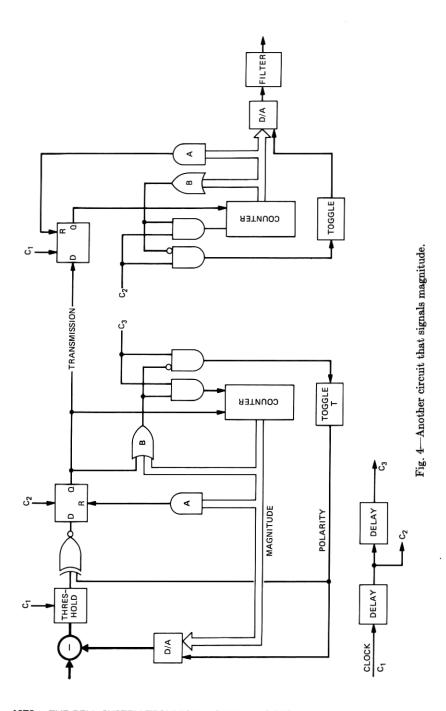

An alternative circuit arrangement for signaling magnitude is shown in Fig. 4. Here the exclusive NOR gate that inverts the code is placed in the feedback loop of the coder, and the counter holds code that describes only the magnitude of the signal. Polarity is defined by the

1672 THE BELL SYSTEM TECHNICAL JOURNAL, OCTOBER 1974

state of a toggle circuit, T. The and gate A prevents overflow of the counter. The or gate B detects when the counter is empty, and when a further decrease in magnitude is demanded, it diverts the clock from the counter to changing the state of the toggle. When the toggle indicates a negative polarity, its output inverts both the code and the output of the D/A network, thereby preserving negative feedback. This circuit arrangement is often easier to implement for companded codes than is the arrangement in Fig. 2. The methods illustrated in Figs. 2 and 4 can be used to modify any codec in Fig. 1. For the application to multilevel coding, the exclusive nor gate should be used to invert only the polarity bit, the magnitude in the transmitted bit remaining unchanged.

## III. PRESERVING SIGNAL POLARITY

A liability of signaling magnitudes is the inability to continuously inform the receiver of signal polarity. We now demonstrate that transmission errors cannot cause an inversion of the signal.

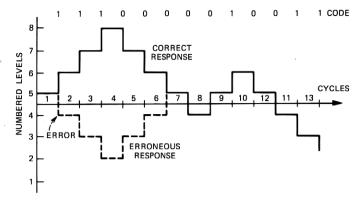

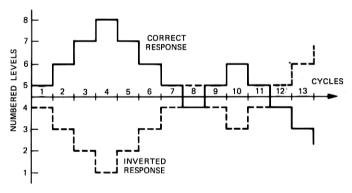

The output signal at any time has one of a set of discrete values. In Fig. 5a, these values have been numbered in order, as have the cycle times. The graph starts at cycle 1 on 5, an odd-numbered level; thereafter, the signal always has an odd-numbered value on an odd-numbered cycle, even after a transmission error has occurred. An inversion of polarity, illustrated in Fig. 5b, requires that the signal assume even-numbered values at odd-numbered cycles. This can occur only after incorrect start-up or loss of synchronization; once polarity is established, it will be preserved as long as the system remains synchronized, transmission errors having only a transitory effect.

Notice that the method used for avoiding overflow of the counters in Figs. 2 and 4 preserves the timing of the system in a way that prevents an inversion of polarity when error causes an overload. It also helps to eliminate errors in a way that is analogous to the method described in Ref. 2.

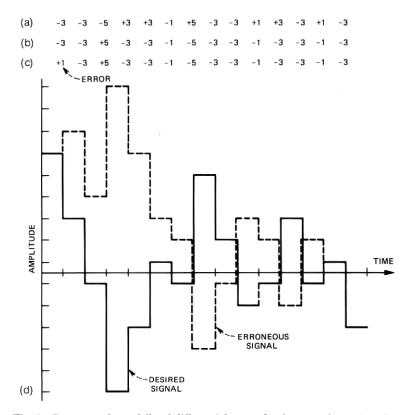

The above discussion applies whether or not the output levels are companded, but it does assume that the signal steps up or down by one level at a time. Multilevel differential codes permit the signal to step through several levels at a time; they can lose their hold on polarity after an error unless step sizes are chosen with care. Specifically, the sum of any odd number of steps should never be equal to the sum of an even number of steps. Regardless of the manner in which the steps are chosen, multilevel steps tend to increase the time taken to wipe out errors, as is illustrated in Fig. 6. These observations indi-

Fig. 5a—codec responses showing the correspondence between odd-numbered cycles and odd-numbered levels.

Fig. 5b—An inversion of polarity caused by incorrect start-up.

cate that signaling changes of magnitude is best suited for 1-bit coding, stepping one level at a time, but the levels themselves may be companded.

# IV. CONCLUSION

Codes that signal changes in magnitude direct the output to step either toward or away from zero amplitude. We have seen that such coding wipes out the effect of a transmission error when next the signal passes zero in an appropriate direction.

Use of zero as the reference is appropriate for coding speech signals, because they frequently pass through zero amplitude. In general, the

Fig. 6—Response of a multilevel differential codec having step sizes  $\pm 1$ ,  $\pm 3$ ,  $\pm 5$ . (a) Ordinary differential code. (b) The code that signals changes of magnitude. (c) The code with an error. (d) The correct and erroneous responses.

reference can be any value that does not correspond exactly to a possible output level. For coding video, the reference is best set at an amplitude corresponding to medium brightness so that errors can be wiped out quickly.

Conventional differential CODECS signal changes in amplitude; they may be regarded as having a reference set outside the signal range and do not use the error correcting properties associated with an internal reference.

### V. ACKNOWLEDGMENT

The author thanks G. D. Boyd, D. J. Connor, C. S. Phelan, and B. Prasada for helpful advice.

#### REFERENCES

J. F. Schouten, F. deJager, and J. A. Greefkes, "Delta Modulation, A New Modulation System for Telecommunication," Philips Tech. Rev., 13, No. 9

Modulation System for Telecommunication," Philips Tech. Rev., 13, No. 9 (March 1952), pp. 237-268.

2. J. O. Limb and F. W. Mounts, "Digital Differential Quantizer for Television," B.S.T.J., 48, No. 7 (September 1969), pp. 2583-2599.

3. C. B. Forrest and S. S. Green, "Analog-to-Digital Converter," U. S. Patent No. 2,836,356 applied for February 1952, issued May 1958.

4. David A. Harms, "PCM Coder," U. S. Patent No. 2,638,219 applied for May 1969, issued January 1972.

5. J. C. Candy, "A Use of Limit Cycle Oscillations to Obtain Robust Analog-to-Digital Converters," I.E.E.E. Trans. Comm., 22, No. 3 (March 1974), pp. 298-305.