### Sun 3400 CPU Board Configuration Manual

## Sun 3400 CPU Board Configuration Manual

The Sun logo, Sun Microsystems, Sun Workstation, and TOPS are registered trademarks of Sun Microsystems, Inc.

Sun, Sun-2, Sun-3, Sun-4, Sun386*i*, NFS, SunInstall, SunLink, SunOS, SunPro, SunView, NeWS, NSE, and SPARC are trademarks of Sun Microsystems, Inc.

UNIX is a registered trademark of AT&T. OpenLook is a trademark of AT&T.

All other products or services mentioned in this document are identified by the trademarks or service marks of their respective companies or organizations, and Sun Microsystems, Inc. disclaims any responsibility for specifying which marks are owned by which companies or organizations.

#### CAUTION

This equipment generates, uses, and can radiate radio frequency energy and if not installed and used in accordance with the instructions manual, may cause interference to radio communications. It has been tested and found to comply with the limits for a Class A computing device pursuant to Subpart J of Part 15 of FCC Rules, which are designed to provide reasonable protection against such interference when operated in a commercial environment. Operation of this equipment in a residential area is likely to cause interference in which case the user at his own expense will be required to take whatever measures may be required to correct the interference.

This digital apparatus does not exceed the Class A limits for radio noise emissions from digital apparatus set out in the Radio Interference Regulations of the Canadian Department of Communications.

Le présent appareil numérique n'émet pas de bruits radioélectriques dépassant les limites applicables aux appareils numériques de la classe A prescrites dans le Règlement sur le brouillage radioélectrique édicté par le ministère des Communications du Canada.

#### WARNING

There is a Lithium Battery, Matsushita Electric Type No. BR2325, located on the Sun CPU Board. This battery is NOT a customer replaceable part. The battery is marked as follows: "Warning— Replace battery with MATSUSHITA ELECTRIC, PANASONIC, or RAYOVAC Part No. BR2325 only."

The battery may explode if mistreated. Do not dispose of the battery in fire. Do not disassemble it or recharge it.

Copyright © 1989 Sun Microsystems, Inc. - Printed in U.S.A.

All rights reserved. No part of this work covered by copyright hereon may be reproduced in any form or by any means – graphic, electronic, or mechanical – including photocopying, recording, taping, or storage in an information retrieval system, without the prior written permission of the copyright owner.

Restricted rights legend: use, duplication, or disclosure by the U.S. government is subject to restrictions set forth in subparagraph (c)(1)(i) of the Rights in Technical Data and Computer Software clause at DFARS 52.227-7013 and in similar clauses in the FAR and NASA FAR Supplement.

The Sun Graphical User Interface was developed by Sun Microsystems Inc. for its users and licensees. Sun acknowledges the pioneering efforts of Xerox in researching and developing the concept of visual or graphical user interfaces for the computer industry. Sun holds a non-exclusive license from Xerox to the Xerox Graphical User Interface, which license also covers Sun's licensees.

####

#### Contents

| Chapte | <b>r 1</b> General Description and Configuration   | 3 |

|--------|----------------------------------------------------|---|

|        | Introduction                                       | 3 |

|        | General Sun 3400 CPU Board Description             | 3 |

|        | Video Daughter Boards                              | 4 |

|        | Configuration of the Jumpers on the 3400 CPU Board | 4 |

|        | ECC Memory Configuration                           | 4 |

#### Tables

Table 1-1 Factory Configuration of Jumpers on the 3400 CPU Board

5

# Figures

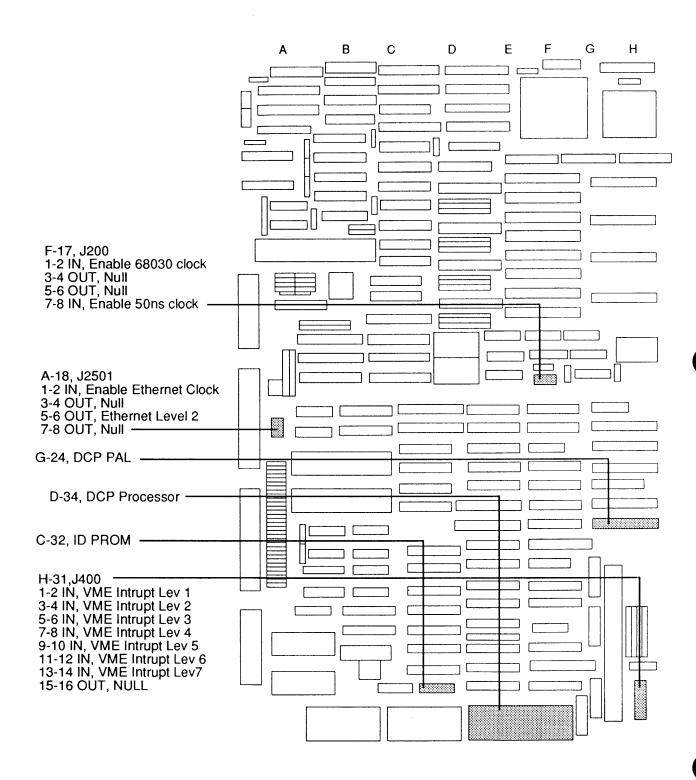

| Figure 1-1 | Section A-H of the Board | 6 |

|------------|--------------------------|---|

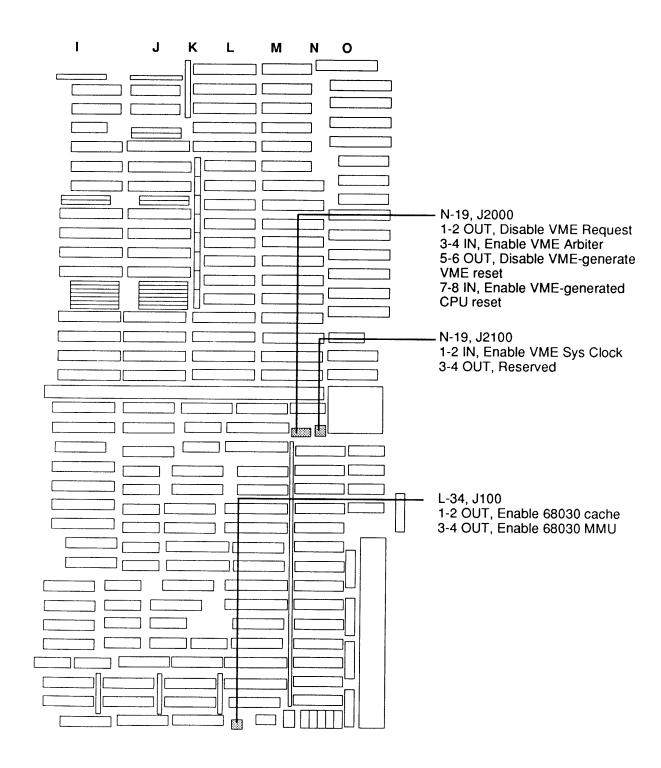

| Figure 1-2 | Section I-O of the Board | 7 |

# General Description and Configuration

1

| General Description and Configuration              |  |  |  |

|----------------------------------------------------|--|--|--|

| Introduction                                       |  |  |  |

| General Sun 3400 CPU Board Description             |  |  |  |

| Video Daughter Boards                              |  |  |  |

| Configuration of the Jumpers on the 3400 CPU Board |  |  |  |

| ECC Memory Configuration                           |  |  |  |

1

# General Description and Configuration

| Introduction               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | This document identifies jumper–block locations and describes required jumper configurations on the Sun 3400 CPU Board.                                                                                                                                                                                                     |  |  |  |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                            | Instructions for the removal and installation of your boards are contained in their respective board installation manuals. Instructions for board access and back-<br>plane jumper access are contained in your system installation manual. Instruc-<br>tions for the configuration of your backplane jumpers are contained in your <i>Sun-</i><br><i>3/460 and 3/480 Cardcage Slot Assignments and Backplane Configuration Pro-</i><br><i>cedures</i> manual (P/N 813–2056), CCSA and BCA (P/N 2004) or in your <i>Sun-</i><br><i>3/470 Cardcage Slot Assignments and Backplane Configuration Procedures</i><br>manual (P/N 813-2073). |                                                                                                                                                                                                                                                                                                                             |  |  |  |

|                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ructions for the configuration of your memory boards or your frame buffer<br>rds are covered in their respective memory board or frame buffer board<br>huals.                                                                                                                                                               |  |  |  |

| General Sun 3400 CPU Board | Standard features of the Sun 3400 CPU board include:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                             |  |  |  |

| Description                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | A 68030 central processor with separate internal 256 byte instruction and data caches and an address translation cache (ATC) for CPU address translation. The data cache is designed as a write-through cache. Both the data and instruction caches are structured as 32 blocks of 16 bytes each. The 68030 runs at 33 MHz. |  |  |  |

|                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | A central cache configured as a 64 kbyte writeback cache.                                                                                                                                                                                                                                                                   |  |  |  |

|                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | An I/O cache that supports 16 byte blocks.                                                                                                                                                                                                                                                                                  |  |  |  |

|                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | A 68882 Floating Point Coprocessor (FPC) running on the same 33MHz clock as the CPU and enabled by the system enable register bit.                                                                                                                                                                                          |  |  |  |

|                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | A VMEbus arbitration and diagnostic mode for DVMA interface testing on the board.                                                                                                                                                                                                                                           |  |  |  |

|                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 64-bit multiplexed address/data bus memory with support for both 8MB and 32MB ECC memory boards and the Sun-3 Floating Point Accelerator (FPA) board.                                                                                                                                                                       |  |  |  |

|                            | ۵                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | P4 bus support that allows a variety of video daughter boards to be used.                                                                                                                                                                                                                                                   |  |  |  |

|                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | P2 MEZZ bus support that allows the FPA+ to be used.                                                                                                                                                                                                                                                                        |  |  |  |

|                                                    | Interface circuitry that supports the VMEbus, Ethernet, two serial ports, the keyboard, and the mouse.                                                                                                                                                                                                                                                                                                                                                                       |

|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                    | An optional feature is the Data Ciphering Protocol (DCP) Processor chip set. This chip set provides additional security for your sensitive files by encrypting network data.                                                                                                                                                                                                                                                                                                 |

| Video Daughter Boards                              | The Sun 3400 CPU board will be paired with either a monochrome video daughter board or one of three color video daughter boards. In some systems, a separate terminal will be connected to one of the serial ports on the rear edge of the 3400 CPU board. In other systems, a monitor will operate from a separate color or graphics board.                                                                                                                                 |

| Configuration of the Jumpers on the 3400 CPU Board | Table 1 on the following page shows the factory configuration of the jumper-blocks on the Sun 3400 CPU board.                                                                                                                                                                                                                                                                                                                                                                |

|                                                    | Each board has grid markings that form an X–Y coordinate system. Letters of the alphabet define the X coordinate and numbers define the Y coordinate of the grid. Table 1 lists the location coordinates of pin 1 of each jumper–block. For example, referring to Table 1, pin 1 of jumper–block J100 is located at the intersection of coordinates "L" and "34".                                                                                                            |

|                                                    | In Table 1, the <i>Configuration</i> column indicates which pins can be jumpered together and whether or not the board is shipped with the referenced jumper connection installed on the indicated pins. For example, "1–2" in the Configuration column means that a jumper is installed across pins 1 and 2. "IN" means that the CPU board is shipped with the jumper connection installed. "OUT" means that the board is shipped with the jumper connection not installed. |

|                                                    | Again referring to Table 1, the <i>Description</i> column lists the effect of each jumper–block when it is installed in the indicated position. With one exception, when a jumper is "IN", a function is enabled or selected. The exception is jumper–block J100 which disables functions when installed.                                                                                                                                                                    |

|                                                    | To find pin 1 on a given jumper-block, turn the board over to the solder side and look closely at the pins. Pin 1 is soldered into a square shaped pad while the other pins are soldered into circular shaped pads.                                                                                                                                                                                                                                                          |

|                                                    | Figures 1 and 2 show where jumper–blocks are located on the Sun 3400 CPU board.                                                                                                                                                                                                                                                                                                                                                                                              |

| ECC Memory Configuration                           | When the Sun 3400 CPU board is shipped with the 8MB or the 32MB ECC memory board installed, no reconfiguration of the Sun 3400 CPU board or the ECC memory board is required. However, if you install another memory board, you will need to configure that memory board at the time of installation.                                                                                                                                                                        |

To configure the 8MB memory board refer to the Sun 501–1102 Memory Board Configuration Procedure, P/N 813–2018.

For information on configuring the 23MB memory board, please refer to the *Ins-tallation Notes for the 32 Mbyte Memory Board*, P/N 800–2123.

|                                                              | Jumper Configuration                                         |                                                                                              |                                                                                                                                                                                     |  |

|--------------------------------------------------------------|--------------------------------------------------------------|----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Jumper                                                       | Location                                                     | Configuration                                                                                | Description                                                                                                                                                                         |  |

| J100                                                         | L–34                                                         | 1–2, OUT                                                                                     | Enable cache on 68030 (IN = Disable)                                                                                                                                                |  |

| J100                                                         | L–34                                                         | 3–4, OUT                                                                                     | Enable MMU on 68030 (IN = Disable)                                                                                                                                                  |  |

| J200                                                         | F–17                                                         | 1–2, IN                                                                                      | Enable 68030 clock                                                                                                                                                                  |  |

| J200                                                         | F–17                                                         | 3–4, OUT                                                                                     | Null                                                                                                                                                                                |  |

| J200                                                         | F–17                                                         | 5–6, OUT                                                                                     | Null                                                                                                                                                                                |  |

| J200                                                         | F–17                                                         | 7–8, IN                                                                                      | Enable 50ns clock                                                                                                                                                                   |  |

| J400<br>J400<br>J400<br>J400<br>J400<br>J400<br>J400<br>J400 | H–31<br>H–31<br>H–31<br>H–31<br>H–31<br>H–31<br>H–31<br>H–31 | 1–2, IN<br>3–4, IN<br>5–6, IN<br>7–8, IN<br>9–10, IN<br>11–12, IN<br>13–14, IN<br>15–16, OUT | VME Interrupt Level 1<br>VME Interrupt Level 2<br>VME Interrupt Level 3<br>VME Interrupt Level 4<br>VME Interrupt Level 5<br>VME Interrupt Level 6<br>VME Interrupt Level 7<br>Null |  |

| J2000                                                        | M–19                                                         | 1–2, OUT                                                                                     | Disable VME Requestor                                                                                                                                                               |  |

| J2000                                                        | M–19                                                         | 3–4, IN                                                                                      | Enable VME Arbiter                                                                                                                                                                  |  |

| J2000                                                        | M–19                                                         | 5–6, OUT                                                                                     | Disable VME–generated VME reset                                                                                                                                                     |  |

| J2000                                                        | M–19                                                         | 7–8, IN                                                                                      | CPU–generated VME reset                                                                                                                                                             |  |

| J2100                                                        | N–19                                                         | 1–2, IN                                                                                      | Enable VME Sys Clock                                                                                                                                                                |  |

| J2100                                                        | N–19                                                         | 3–4, OUT                                                                                     | Reserved                                                                                                                                                                            |  |

| J2501<br>J2501<br>J2501<br>J2501                             | A–18<br>A–18<br>A–18<br>A–18<br>A–18                         | 1–2, IN<br>3–4, OUT<br>5–6, OUT<br>7–8, OUT                                                  | Enable Ethernet Clock<br>Null<br>Ethernet Level 2 (IN = Level 1)<br>Null                                                                                                            |  |

Table 1-1

Factory Configuration of Jumpers on the 3400 CPU Board

# **Revision History**

| Revision | Dash<br>Number | Date             | Comments                             |

|----------|----------------|------------------|--------------------------------------|

| 01       | 01             | 11 April 1988    | Alpha Review Draft                   |

| 02       | 02             | 3 October 1988   | Second Review Draft.                 |

| 50       | 03             | 14 November 1988 | Beta Review and Engineering Release. |

| 50       | 04             | 23 January 1989  | Review Draft.                        |

| 50       | 05             | 29 January 1989  | Beta Draft                           |

| Α        | 10             | 17 April 1989    | Released for customer shipment       |

| Α        | 11             | 15 May 1989      | FCS                                  |

|          |                |                  |                                      |

|          |                |                  |                                      |

|          |                |                  |                                      |

.

.

| SUN 3400 CPU Board Configuration |

|----------------------------------|

| Manual Reader Comment Sheet      |

#### Dear Reader,

We who work at Sun Microsystems wish to provide the best possible documentation for our products. To this end, we solicit your comments on the *Sun 3400 CPU Configuration Manual*, Part Number 813-2055-11. We would appreciate your critique of this manual, particularly if you discover errors of fact or feel that pertinent information has been omitted.

**Typographical Errors**

Please list typographical errors by page number and exactly duplicate the actual characters when recording and reporting such errors.

**Technical Errors**

Please list errors of fact or technical accuracy by page number and quote erroneous passages verbatim.

Content

Did this manual meet your needs? If not, please indicate what should be changed, added, or deleted in order to meet your needs. Please comment if you believe other information should be included in this manual. Also please advise us if you are aware of information in other manuals that would be more convenient if it were included in this manual.

Layout and Style

Did you find the organization of this guide useful? If not, how would you organize this manual to improve its utility? Did you find the style of this manual to be pleasing? If not, what should be changed to improve the style?

Mail this completed form to:

Manager, Hardware Technical Publications Sun Microsystems, Inc. 2550 Garcia Avenue Mountain View, CA 94043

Corporate Headquarters Sun Microsystems, Inc. 2550 Garcia Avenue Mountain View, CA 94043 415 960-1300 TLX 37-29639

For U.S. Sales Office locations, call: 800 821-4643 In CA: 800 821-4642 European Headquarters Sun Microsystems Europe, Inc. Bagshot Manor, Green Lane Bagshot, Surrey GU19 5NL England 0276 51440 TLX 859017

Australia: (02) 413 2666 Canada: 416 477-6745 France: (1) 40 94 80 00 Germany: (089) 95094-0 Hong Kong: 852 5-8651688 Italy: (39) 6056337 Japan: (03) 221-7021 Korea: 2-7802255 Nordic Countries: + 46 (0)8 7647810 PRC: 1-8315568 Singapore: 224 3388 Spain: (1) 2532003 Switzerland: (1) 8289555 The Netherlands: 3133501234 Taiwan: 2-7213257 UK: 0276 62111

**Europe, Middle East, and Africa, call European Headquarters:** 0276 51440

Elsewhere in the world, call Corporate Headquarters: 415 960-1300 Intercontinental Sales