# **Technical Reference Manual**

PIED PIPER

1

# Technical Reference Manual

Part No.: P/N 20000102 Price: \$125.00 in U.S.A.

#### LIABILITY DISCLAIMER

The PIED PIPER is warranted by Semi-Tech Microelectronics Corporation to be free of defects in materials and workmanship for the period specified in the waranty card enclosed with each unit. Any repairs or modifications performed by persons not authorized by Semi-Tech Microelectronics Corporation will make this waranty null and void. No repairs or modifications should be attempted by persons who are not technically qualified as serious personal injury may result. This manual is to be used as a reference only for technically qualified personel.

The information contained in this manual is believed to be accurate at the time of printing. Semi-Tech Microelectronics Corporation assumes no responsibility for errors or omissions. Semi-Tech Microelectronics Corporation reserves the right to make changes in the design to affect improvements. Such changes may not be referenced in this manual.

First Printing - June 1983

No part of this manual may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of Semi-Tech Microelectronics Corporation.

PIED PIPER is a trademark of Semi-Tech Microelectronics Corporation. CP/M is a trademark of Digital Research Incorporated.

> Copyright c 1983 Semi-Tech Microelectronics Corporation 100 Lombard St., #303 Toronto, Ontario Canada

# TABLE OF CONTENTS

|            | Chapter 1 - Specifications                    | 1        |

|------------|-----------------------------------------------|----------|

| 1.1        | Hardware                                      | 1        |

|            | Software                                      | 2        |

| 1.3        | General                                       | 2        |

|            | Chapter 2 - System Overview                   | 3        |

| 2.1        | 0                                             | 3        |

| 2.2        |                                               | 5        |

|            | I/O Port Assignments                          | 7        |

| 2.4        | Interrupt Assignments                         | 9        |

|            | Chapter 3 - Hardware                          | 10       |

| 3.1        |                                               | 10       |

|            | ROM Selection                                 | 15       |

|            | Clocks/Timing                                 | 16       |

|            | Keyboard Decoder                              | 19       |

|            | Video Controller                              | 21       |

| 3.6        | Floppy Disk Controller<br>Hard Disk Interface | 23<br>24 |

|            | Parallel Output (Printer) Port                | 24       |

|            | Speaker                                       | 20       |

|            | Expansion Board Interface                     | 27       |

|            | Expansion Board Interface                     | 29       |

|            | Floppy Disk Drive                             | 30       |

|            | Power Supply                                  | 31       |

|            | Chapter 4 - Software                          | 32       |

| 4.1        | The Control/Status Registers                  | 32       |

| 4.2        |                                               | 39       |

| 4.3        |                                               | 40       |

| 4.4        | Video Display Controller                      | 50       |

| 4.5        | Floppy Disk Controller                        | 61       |

| 4.6        | Hard Disk Interface                           | 71<br>71 |

| 4.7<br>4.8 | Parallel Output (Printer) Port                | 71       |

| 4.0        | Speaker                                       | 12       |

|            | Chapter 5 - Options                           | 73       |

| 5.1        | Dual RS232C Serial Card                       | 73       |

| 5.2        | Modem/Serial Card                             | 73       |

| 5.3        | Expansion Floppy Disk Drive                   | 73       |

# Appendices

- A. Connector Placement

- B. Circuit Schematics

- C. Character Generator ROM Listing

- D. Bootstrap ROM Listing

- E. Boot Sector Listing

- F. BIOS Listing

# 1.1 Hardware

| Processor:         | Z80A microprocessor<br>4 Mhz clock                                                                                                                                                                                                                                                                                                                                                                        |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Memory:            | 64 Kbytes user read/write memory (RAM)<br>4 Kbytes of read only memory (ROM)<br>2 Kbytes of video display buffer<br>2 Kbytes of display read only memory                                                                                                                                                                                                                                                  |

| Keyboard:          | Full size, typewriter-style<br>Upper/lower case<br>Control & function keys<br>2-key lockout with contact debounce<br>auto-repeat on all keys                                                                                                                                                                                                                                                              |

| Parallel Port:     | Centronics-type parallel output port                                                                                                                                                                                                                                                                                                                                                                      |

| Display:           | 24 lines of 80 characters each with<br>video monitor (not supplied)<br>24 lines of 40 characters each with<br>standard television (not supplied)<br>Connector for RF modulator (not sup-<br>plied) required for TV display<br>Horizontal scrolling keys for TV display<br>allows proper viewing of 80 column lines<br>Displays full ASCII character set, upper<br>and lower case, plus character graphics |

| Floppy Disk Drive: | 5 1/4 inch slimline drive<br>1 Mbyte unformatted storage capacity per<br>diskette<br>800 Kbytes formatted storage capacity<br>per diskette                                                                                                                                                                                                                                                                |

| Power Supply:      | Switching power supply<br>Sufficient capacity for optional floppy<br>disk drive                                                                                                                                                                                                                                                                                                                           |

| Expandability:     | Interface for second floppy disk drive<br>built in<br>Interface for optional hard disk drive<br>built in<br>STD bus I/O interface built in<br>Internal provision for mounting one<br>expansion card                                                                                                                                                                                                       |

1

# 1.2 Software

| Operating System: | CP/M 2.2 from Digital Research Inc.<br>PIED PIPER Utilities including format-<br>ing, file transfer and backup with one<br>disk drive |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| Applications:     | Perfect Writer - word processing<br>Perfect Speller - 50,000 word spelling<br>dictionary                                              |

|                   | Perfect Calc - Electronic spread-sheet<br>Perfect Filer - Data filing/merging                                                         |

## 1.3 General

| Dimensions:    | Height<br>4.0 in.<br>10 cm | Width<br>20.2 in.<br>51 cm | Depth<br>10.8 in.<br>27 cm       |    |

|----------------|----------------------------|----------------------------|----------------------------------|----|

| Weight:        | 12.5 lb. (5                | .6 Kg.)                    |                                  |    |

| Electrical:    |                            | Hz optional                | consumption                      |    |

| Environmental: |                            |                            | F (10 C to 35 (<br>rel. humidity | 2) |

#### CHAPTER 2 SYSTEM OVERVIEW

The PIED PIPER hardware consists of four main modules: the main printed circuit board, the keyboard assembly, the floppy disk drive, and the switching power supply. All modules are mounted inside a shielded plastic case. The software accessible to the user includes the bootstrap program, the video display character generator, and the CP/M BIOS program. This manual will provide technical information on these modules.

#### 2.1 Hardware Configuration

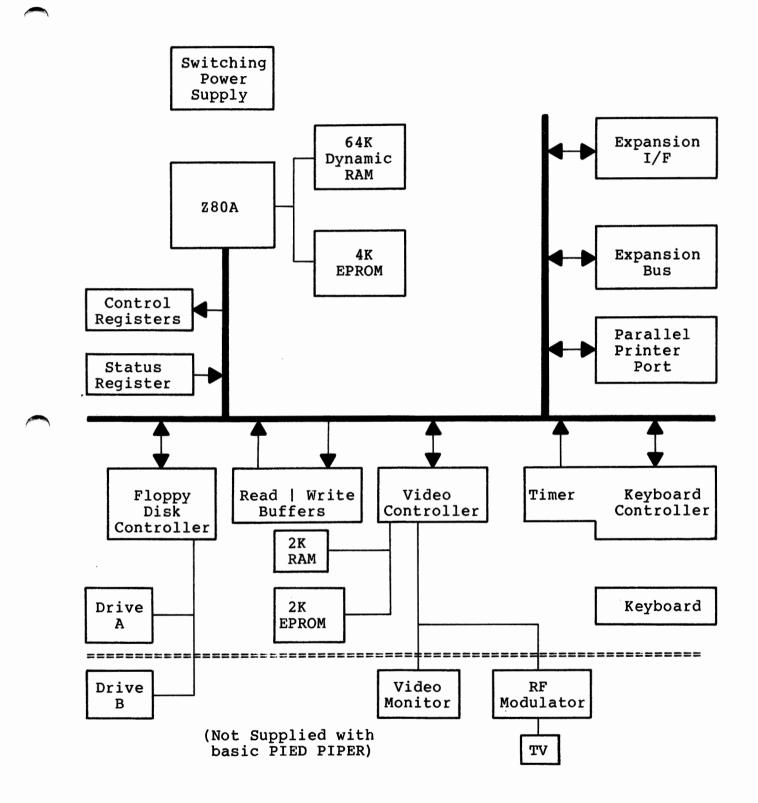

A block diagram of the PIED PIPER hardware organization is given in Fig. 2.1. The main microprocessor is a Z80A running at 4 MHz. The memory space is normally occupied by 64 Kbytes of fast dynamic RAM. After a system reset or on startup, 4 Kbytes of read only memory are switched in to replace the bottom half of the RAM. This is used to start up the system and load the disk operating system. The ROM can also be switched in/out under software control. All the peripheral controllers use programmed data transfers to communicate with the central microprocessor. Eight interrupts are configured for the sytem. Two are used by the floppy disk drive controller to indicate that its data buffer is full (DRQ) or that it has finished executing the last command (INTRQ). The video display controller uses one interrupt to indicate to the CPU when it has completed the The keyboard controller can use an requested command. interrupt to indicate when it contains key-pressed data, but this interrupt is not enabled by the system software. Another interrupt comes from a timer which is contained in the keyboard controller. This interrupt is used as an interval timer by the system software. The remaining three interrupts are available for use by the expansion cards or expansion bus.

In addition to the standard peripheral controllers, the system contains some internal I/O ports which serve the function of control/status registers. By writing data to the control registers, changes can be made to the initial hardware setup (for example, the video display format). By reading data from the status register, information can be obtained on the present state of the hardware peripherals (for example, if any interrupts are pending). These registers are initialized at startup. Changes in their contents should be made with care as it could prevent normal system operation.

3

Fig. 2.1 Basic PIED PIPER hardware configuration.

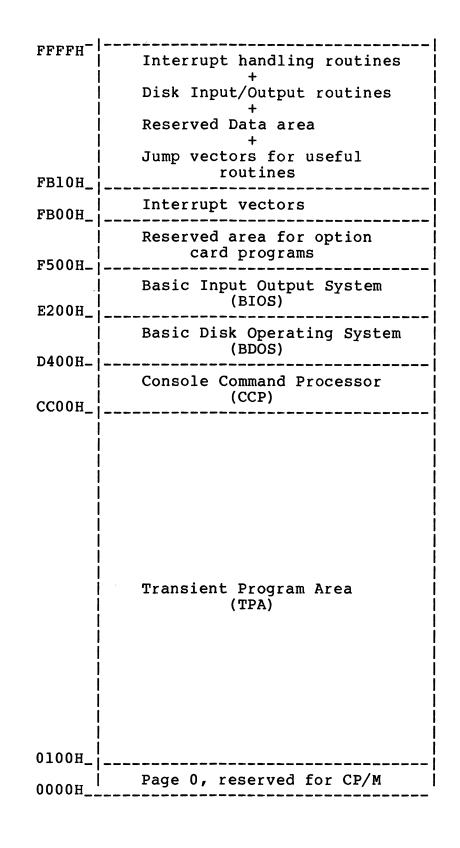

#### 2.2 Memory Map

The PIED PIPER has a total of 72 Kbytes of memory. These include the following:

- 64K RAM system memory

- 4K bootstrap ROM

- 2K RAM display memory

- 2K character generator ROM

Only the bootstrap ROM and the system memory use the Z80A processor memory address space. The display memory is accessed through I/O addresses, and the character generator ROM is accessed solely by the video display controller.

Although the bootstrap ROM is only 4 Kbytes in size, the PIED PIPER is capable of accommodating ROM of up to 16 Kbytes in size. Both the system memory and the bootstrap ROM share the memory addresses from 0000 hex to 7FFF hex, but only one will be activated at any given time. When the ROM is enabled, access to memory addresses 0000 to 7FFF hex will be directed to the ROM. When the ROM is disabled, access will be directed to the system RAM memory.

The bootstrap ROM contains hardware initialization procedures, self test diagnostics, and the bootstrap routine for bringing in the first sector of the first track from the floppy diskette. The content of this ROM is copied to RAM starting from location F000 hex, after some preliminary self tests. The ROM is then disabled, and the remaining self tests plus the bootstrap procedure are executed from the RAM area.

5

System memory map after initialization.

#### 2.3 I/O Port Assignments

PORT

The CPU address lines are decoded, along with the input/output control lines, to split the I/O port address space into banks of I/O ports. There are eight banks decoded, with each bank containing up to eight sequentially addressed I/O ports. Each bank has its own enabling signal (CSO to CS7).

The I/O port addresses used by the system software and hardware and their functions are described as follows :-

Bank 0: Ports 00H-07H (Enabling Signal CSO)

READ

All Ports Relate to the Video Controller

| 00н         | Interrupt Register   | Initialization Register |

|-------------|----------------------|-------------------------|

| <b>01</b> H | Status Register      | Command Register        |

| 02H         | Screen Start Address | Screen Start Address    |

|             | Register (low byte)  | Register (low byte)     |

| 03H         | Screen Start Address | Screen Start Address    |

|             | Register (high byte) | Register (high byte)    |

| 04H         | Cursor Address       | Cursor Address          |

|             | Register (low byte)  | Register (low byte)     |

| 05H         | Cursor Address       | Cursor Address          |

|             | Register (high byte) | Register (high byte)    |

| 06H         |                      | Pointer Address         |

|             |                      | Register (low byte)     |

| 07H         |                      | Pointer Address         |

|             |                      | Register (high byte)    |

|             |                      |                         |

WRITE

Bank 1: Ports 08H-0FH (Enabling Signal CS1)

| PORT | READ                                   | WRITE                                   |

|------|----------------------------------------|-----------------------------------------|

| 08H  | Keyboard Controller<br>Data Register   | Keyboard Controller<br>Data Register    |

| 09H  | Keyboard Controller<br>Status Register | Keyboard Controller<br>Command Register |

| 0DH  | Display Buffer<br>(Read)               | Parallel Output<br>(Printer) Port       |

Bank 2: Ports 10H-17H (Enabling Signal CS2)

All Ports Relate to the Floppy Disk Controller

| PORT | READ            | WRITE            |

|------|-----------------|------------------|

| 10H  | Status Register | Command Register |

| 11H  | Track Register  | Track Register   |

| 12H  | Sector Register | Sector Register  |

| 13H  | Data Register   | Data Register    |

Bank 3: Ports 18H-1FH (Enabling Signal CS3)

| PORT       | READ                | WRITE                                |

|------------|---------------------|--------------------------------------|

| 18H<br>1CH | STATUS REGISTER<br> | CONTROL REGISTER I<br>Display Buffer |

| lDH        |                     | (Write)<br>CONTROL REGISTER II       |

Bank 4: Ports 20H-27H (Enabling Signal CS4) Reserved for Expansion Card #1 [J8]

Bank 5: Ports 28H-2FH (Enabling Signal CS5)

Reserved for Expansion Card #2 [J7]

Bank 6: Ports 30H-37H (Enabling Signal CS6) Reserved for Hard Disk Interface

Bank 7: Ports 38H-3FH (Enabling Signal CS7)

Reserved for Expansion Bus [J1] and Expansion Cards #1 and #2 [J8,J7]

## 2.4 Interrupt Assignments

The PIED PIPER is programmed to respond to maskable interrupt mode 2 of the Z80A processor. The interrupt vectors are located from memory address FB00 hex to FB0F hex.

Eight interrupts are supported by the PIED PIPER. These are listed below in descending priority.

- 1. Disk data request (DRQ)

- 2. Disk controller interrupt request (INTRQ)

- Video display controller

Keyboard controller

- 5. Timer

- 6. Expansion connector J8

- 7. Expansion connector J7

- 8. STD Bus connector J1

#### CHAPTER 3 HARDWARE

## 3.1 Printed Circuit Board Connections

The following sub-sections give pin assignments for all connection points to the printed circuit board. This is intended as a quick reference only. Detailed descriptions of the signal labels and their specifications are included in other sections of this Chapter.

#### <u>Keyboard Connector [J13]:</u>

The pin assignments for the keyboard connector are as follows:-

| <u>Pin No.</u> | <u>Signal Name</u> | <u>Pin No.</u> | <u>Signal Name</u> |

|----------------|--------------------|----------------|--------------------|

| 1              | CNTL               | 2              | CAPLK/             |

| 3              | SHIFT/             | 4              | RL0                |

| 5              | RLl                | 6              | RL2                |

| 7              | RL3                | 8              | RL4                |

| 9              | RL5                | 10             | RL6                |

| 11             | CL0                | 12             | RL7                |

| 13             | CL1                | 14             | CL2                |

| 15             | CL3                | 16             | CL4                |

| 17             | CL5                | 18             | CL6                |

| 19             | CL7                | 20             | Signal Ground      |

| 21             | CO0/               | 22             | CO1/               |

| 23             | +5V                | 24             | SPK                |

#### Reset Switch:

A push button switch is included on the board to produce the reset signal for the system and any expansion boards. The pin assignment for the reset switch [J5] is as follows:-

| <u>Pin</u> | <u>No.</u> | Description                                                             |

|------------|------------|-------------------------------------------------------------------------|

| 1          |            | Signal Ground                                                           |

| 2          |            | Reset Signal. This line goes low when<br>the reset button is depressed. |

## Composite Video Jack [J2]:

This is an RCA phono jack which provides the RS170 standard video signal to the optional video monitor. The pin assignments are as follows : -

| <u>Pin No.</u> | Description                                                                                                 |

|----------------|-------------------------------------------------------------------------------------------------------------|

| 1              | Composite Video signal of approximately<br>1.3 volts peak to peak amplitude into a<br>75 Ohm load impedance |

| 2              | Chassis Ground                                                                                              |

## RF Modulator Jack [J4]:

This is a 5 pin Din type jack compatible with an ASTEC UM1381 Video Modulator or any FCC approved Video Modulator with the same pinout and signal configuration. The pin assignments are as follows:-

| <u>Pin No.</u> | Description                                   |

|----------------|-----------------------------------------------|

| 1              | 12V DC Supply                                 |

| 2              | Video Shield Ground (0 V)                     |

| 3              | Audio Out (1.0 V <sub>p-p</sub> , AC-coupled) |

| 4              | Video Out (0.8 V <sub>p-p</sub> , AC-coupled) |

| 5              | Not used                                      |

#### Floppy Disk Drive Connector [J12]:

The pin assignments for the connectors for the internal and optional expansion floppy disk drive are as follows:-

| <u>Pin No.</u> | <u>Signal Name</u> | <u>Pin</u> No. | <u>Signal Name</u> |

|----------------|--------------------|----------------|--------------------|

| 2              | Not used.          | 4              | Not used.          |

| 6              | Not used.          | 8              | INDEX/             |

| 10             | DR1/               | 12             | DR2/               |

| 14             | Not used.          | 16             | MOTOREN/           |

| 18             | DIR/               | 20             | STEP/              |

| 22             | WD                 | 24             | WG/                |

| 26             | TRK00/             | 28             | WPRT/              |

| 30             | RD                 | 32             | SS/                |

| 34             | Not used.          | 36             | Not used.          |

| 38             | Not used.          | 40             | Not used.          |

All odd numbered pins are grounded except pins 35, 37 and 39 which are not used.

## Hard Disk Interface Connector [J10]:

The pin assignments for the hard disk interface connector are as follows:-

| <u>Pin No.</u> | <u>Signal Name</u> | <u>Pin No.</u> | <u>Signal Name</u> |

|----------------|--------------------|----------------|--------------------|

| 1              | HDAL0              | 3              | HDAL1              |

| 5              | HDAL2              | 7              | HDAL3              |

| 9              | HDAL4              | 11             | HDAL5              |

| 13             | HDAL6              | 15             | HDAL7              |

| 17             | ABO                | 19             | ABl                |

| 21             | AB2                | 23             | CS6/               |

| 25             | IOWR'/             | 27             | IORD'/             |

| 29             | WAIT'/             | 31             | HDRES'/            |

| 33             | Not used.          | 35             | HINTRQ'            |

| 37             | HDRQ '             | 39             | Not used.          |

All even numbered pins are grounded.

## Parallel Output (Printer) Port [J3]:

This is a 15-pin female DB-type jack. The pin assignments are as follows:-

| <u>Pin No.</u> | <u>Signal Name</u> | <u>Pin No.</u> | <u>Signal Name</u> |

|----------------|--------------------|----------------|--------------------|

| 1              | DATAL              | 2              | DATA2              |

| 3              | DATA3              | 4              | DATA4              |

| 5              | DATA5              | 6              | DATA6              |

| 7              | DSTR/              | 8              | PRBUSY             |

| 9              | DATA7              | 10             | DATA8              |

| 11             | GROUND             | 12             | GROUND             |

| 13             | GROUND             | 14             | GROUND             |

| 15             | GROUND             |                |                    |

# Speaker [J6]:

The speaker connections are defined as follows:

| <u>Pin No.</u> | Name | Description                                                          |

|----------------|------|----------------------------------------------------------------------|

| 1              | +5V  | To be connected to one side of the speaker                           |

| 2              | SPK  | Audio output. To be connected<br>to the other side of the<br>speaker |

## Expansion Card Connectors [J7,J8]:

Two connectors are provided on the board for interfacing to the optional expansion cards. The pin assignments for connector [J7] are as follows :-

| <u>Pin No.</u> | <u>Signal Name</u> | <u>Pin No.</u> | <u>Signal Name</u> |

|----------------|--------------------|----------------|--------------------|

| 1              | AB0                | 2              | AB1                |

| 3              | AB2                | 4              | Ground             |

| 5              | Ground             | 6              | +5V                |

| 7              | CS5/               | 8              | RESET/             |

| 9              | CLK                | 10             | INT1/              |

| 11             | AUDIO              | 12             | DB7                |

| 13             | DB6                | 14             | DB5                |

| 15             | DB4                | 16             | DB3                |

| 17             | DB2                | 18             | DB1                |

| 19             | DB0                | 20             | +5V                |

| 21             | Ground             | 22             | Ground             |

| 23             | IOWR'/             | 24             | IORD'/             |

| 25             | WAIT/              | 26             | CS7/               |

| 27             | +12V               | 28             | -12V               |

The pin assignments for connector [J8] are as follows:-

| <u>Pin No.</u> | <u>Signal Name</u> | <u>Pin No.</u> | <u>Signal Name</u> |

|----------------|--------------------|----------------|--------------------|

| 1              | AB0                | 2              | ABl                |

| 3              | AB2                | 4              | Ground             |

| 5              | Ground             | 6              | +5V                |

| 7              | CS4/               | 8              | RESET/             |

| 9              | CLK                | 10             | INT2/              |

| 11             | AUDIO              | 12             | DB7                |

| 13             | DB6                | 14             | DB5                |

| 15             | DB4                | 16             | DB3                |

| 17             | DB2                | 18             | DB1                |

| 19             | DB0                | 20             | +5V                |

| 21             | Ground             | 22             | Ground             |

| <u>Pin No.</u> | <u>Signal Name</u> | <u>Pin No.</u> | <u>Signal Name</u> |

|----------------|--------------------|----------------|--------------------|

| 23             | IOWR'/             | 24             | IORD'/             |

| 25             | WAIT/              | 26             | CS7/               |

| 27             | +12V               | 28             | -12V               |

## Expansion Bus Edge Connector [J1]:

An edge connector is provided which produces a subset of the STD bus signals and can be used for system expansion. The pin assignments are as follows:-

| <u>Pin No.</u>        | <u>Signal Name</u> | <u>Pin No.</u> | <u>Signal Name</u> |

|-----------------------|--------------------|----------------|--------------------|

| 1                     | +5V DC             | 2              | +5V DC             |

| 3                     | Ground             | 4              | Ground             |

| 5                     | Not used           | 6              | Not used           |

| 1<br>3<br>5<br>7<br>9 | DB3                | 8              | DB7                |

|                       | DB2                | 10             | DB6                |

| 11                    | DB1                | 12             | DB5                |

| 13                    | DB0                | 14             | DB4                |

| 15                    | AB7                | 16             | Not used           |

| 17                    | AB6                | 18             | Not used           |

| 19                    | AB5                | 20             | Not used           |

| 21                    | AB4                | 22             | Not used           |

| 23                    | AB3                | 24             | Not used           |

| 25                    | AB2                | 26             | Not used           |

| 27                    | AB1                | 28             | Not used           |

| 29                    | ABO                | 30             | Not used           |

| 31                    | WR'/               | 32             | RD'/               |

| 33                    | IORQ'/             | 34             | MREQ/              |

| 35                    | AUDIO              | 36             | CS7/               |

| 37                    | Not used           | 38             | Not used           |

| 39                    | Not used           | 40             | Not used           |

| 41                    | BUSAK/             | 42             | BUSRQ/             |

| 43                    | INTAK/             | 44             | INTO/              |

| 45                    | WAIT/              | 46             | NMI/               |

| 47                    | RESET/             | 48             | Not used           |

| 49                    | CLK                | 50             | Not used           |

| 51                    | Not used           | 52             | Not used           |

| 53                    | Ground             | 54             | Ground             |

| 55                    | +12V DC            | 56             | -12V DC            |

## DC Power Connector [J9]:

This is a 4 pin male connector which joins with the DC power cable coming from the internal switching power supply. It provides all the DC power for the main circuit board and any expansion cards attached to board.

The pin assignments are as follows :-

| <u>Pin No.</u> | <u>Wire</u> <u>Color</u> | Description              |

|----------------|--------------------------|--------------------------|

| 1              | Green                    | Common Electrical Ground |

| 2              | Red                      | +5V                      |

| 3              | Yellow                   | +12V                     |

| 4              | Blue                     | -12V                     |

#### 3.2 ROM Selection

The PIED PIPER requires 32 Kbits of read-only memory containing the Boot Utility Program. This ROM must be present in the system from address 0000H to 0FFFH on startup or after a system reset. In order to provide a full 64 Kbyte RAM addressing capability for the system, the memory address space from 0000H to 7FFFH is shared by the ROM and RAM. However, only one is activated at any given time. After a system reset, the ROM is enabled. However, the system CONTROL REGISTER II can be used to enable or disable the ROM under software control. The RAM in the address space from 8000H to FFFFH is independent of the contents of CONTROL REGISTER II. This RAM is always present in the system, whether the ROM is enabled or not.

The circuit is designed to accomodate ROM of up to 128 Kbits in size, which will then occupy memory adddress space from 0000H to 3FFFH. The system is shipped with a 2732-type EPROM containing the PIED PIPER BOOT UTILITY PROGRAM. To use a 2764-type (64 Kbit) EPROM, a jumper must be installed from JU to JU2. To use a 27128-type (128 Kbit) EPROM, a jumper must be installed from JU to JU1 instead. Only one jumper should be installed. The EPROM should have an access time of 450 nsec. or less.

15

## ROM SOCKET PINOUT

| +5V | 11  | 28 | +5V |          |

|-----|-----|----|-----|----------|

| A12 | 2   | 27 | +5V | *JU2 +5V |

| A07 | 3   | 26 |     | *JU      |

| A06 | 4   | 25 | 80A | *JU1 A13 |

| A05 | 5   | 24 | A09 |          |

| A04 | 6   | 23 | All |          |

| A03 | 7   | 22 | OE/ |          |

| A02 | 8   | 21 | A10 |          |

| A01 | 9   | 20 | CE/ |          |

| A00 | 10  | 19 | D07 |          |

| D00 | 11  | 18 | D06 |          |

| D01 | 112 | 17 | D05 |          |

| D02 | 13  | 16 | D04 |          |

| GND | 14  | 15 | D03 |          |

|     |     |    |     |          |

## 3.3 Clocks/Timing

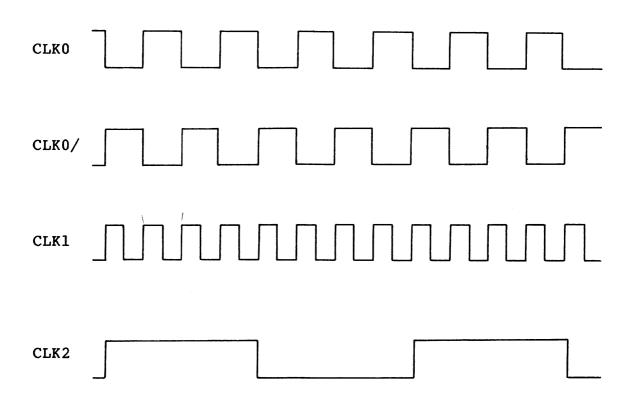

The 4 MHz microprocessor clock is derived from the clock generator circuit which uses an 8.000 MHz crystal. This system clock is scaled down with a counter [U70] to provide the 1 MHz clock for the peripheral controllers. The clock labels are defined as follows:-

| LABEL | DEFINITON                                                                       |

|-------|---------------------------------------------------------------------------------|

| CLK0  | System Clock (4.000 MHz)                                                        |

| CLK0/ | Complement of CLK0 (4.000 MHz)                                                  |

| CLK1  | (8.000 MHz)                                                                     |

| CLK2  | Keyboard Controller Clock and Floppy Disk<br>Drive Controller Clock (1.000 MHz) |

The phase relationship of these clock signals is defined in the following timing diagrams:-

The microprocessor has a 16-bit address bus and an 8bit data bus. The low order address bus lines and the data bus lines DB0-DB7 are buffered. The BUSRQ/, HALT/, NMI/, INT/, and WAIT/ are held high by 1 KOhm resistors to +5V. I/O write and read signals are decoded by logic gates using signals IORQ/, WR/, and RD/ from the CPU.

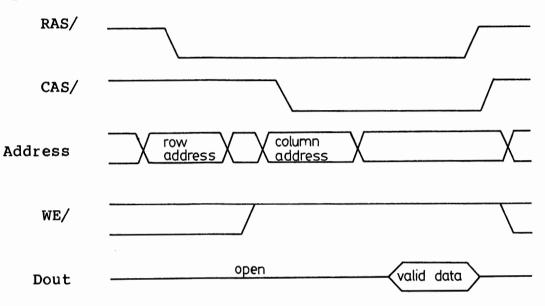

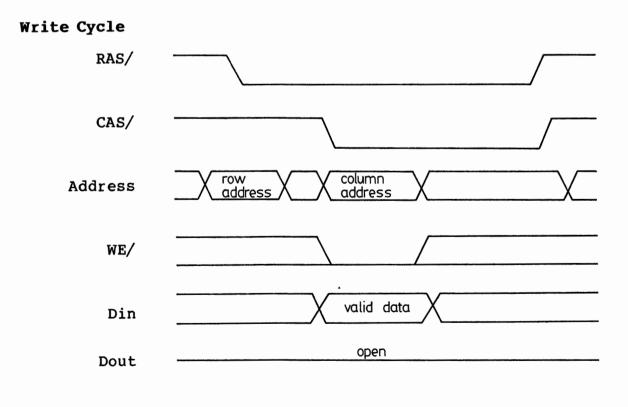

The PIED PIPER uses eight 64K x 1 bit Dynamic RAM's to provide 64 Kbytes of user read/write memory. Two multiplexors [U46, U47] use the status of the Row Address Strobe (RAS/) and Column Address Strobe (CAS/) signals to encode the low and high address bytes and supply them to the DRAM's. The data lines are directly tied to the system data bus and the data read/write mode is selected by the write enable line (WE/). A logic high on WE/ selects the read mode and a logic low selects the write mode.

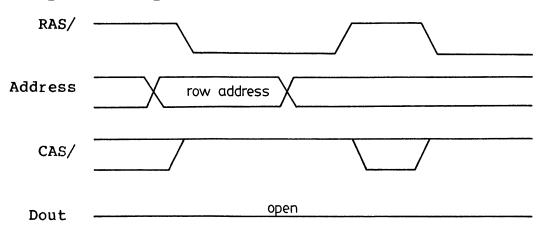

The DRAM's are automatically refreshed during instruction fetch cycles. The CAS/ line is set high when the refresh signal line (RFSH/) is low to avoid any data output during refresh. When RFSH/ and MREQ/ are low, the RAS/ line uses the lower system address byte as a refresh address and causes all bits in each row to be refreshed.

The timing waveforms for memory read, write, and refresh are as follows:-

#### Read Cycle

#### 3.4 Keyboard Controller

The keyboard controller uses the Intel 8279 Programmable Keyboard Controller. The controller is mounted on the main printed circuit board and interfaces with the keyboard via the connecting cable attached to connector J13.

The controller rapidly scans through the column lines CLO-CL7 of the keyboard matrix. As each column is enabled, the return lines RLO-RL7 are sensed to determine if any key in that column is closed. If a key closure is detected, then a debounce circuit is activated to check if it is a proper key switch depression. If the closure is shorter than 10 msec, then it is regarded as a bounce and the controller looks for another key closure. Otherwise, it is taken as a proper key depression and the key position is returned together with the status of the CONTROL and SHIFT lines and stored in the controller's character buffer.

When a key closure is detected which lasts for more than 1 second, the keyboard is disabled by resetting the KBREL line and then re-enabled again to check for a key depression. If a key closure is still detected and the key value is the same as that previously stored in the controller's character buffer, then the key is assumed to be in the auto repeat mode. The KBREL line is disabled and re-enabled every 0.05 seconds to generate a multiple key closure effect. This process is repeated until the key is released. If no key, or a different key closure, is detected at any time after the KBREL line is re-enabled, then the controller returns to its normal keyboard scan cycle.

A 24 pin male connector is used to connect the main

printed circuit board to the keyboard assembly. The signal descriptions for the connector are as follows :-

| <u>Signal Name</u>                                       | <u>Signal flow</u> | Functional description                                                                                                                                               |

|----------------------------------------------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CL0-CL7                                                  | Output             | Column scan lines which<br>are used to scan for key<br>switch closure. SL7 is<br>the most significant<br>column number.                                              |

| RLO-RL7                                                  | Input              | Return line inputs. Each<br>These line should be<br>pulled high unless a<br>switch closure in the row<br>pulls it low. RL7 is the<br>most significant row<br>number. |

| CNTL/                                                    | Input              | This line should be low<br>when either the "CTRL" or<br>"FUNCT" key is depressed.                                                                                    |

| SHIFT/                                                   | Input              | This line should be low<br>when either the "SHIFT"<br>or "FUNCT" key is<br>depressed.                                                                                |

| <u>KEY</u> <u>DEPRH</u><br>FUNCT<br>CTRL<br>SHIFT<br>NIL | SSION              | <u>CTRL/ SHIFT/</u><br>Low Low<br>Low High<br>High Low<br>High High                                                                                                  |

| CAPLK/                                                   | Input              | This line should be low<br>when the capital lock key<br>"CAPS LOCK" is depressed.                                                                                    |

| CO0/-CO1/                                                | Output             | Drive select indicators.<br>COO/ is low when drive l<br>is selected. COI/ is low<br>when drive 2 is selected.                                                        |

| SPK                                                      | Output             | Audio signal Output to<br>speaker mounted on the<br>keyboard PCB.                                                                                                    |

#### 3.5 Vidéo Controller

The Video Display Controller consists of a Signetics 2672 Programmable Video Timing Controller (PVTC), 2 Kbytes of display buffer memory, a display character generator ROM, and video and attribute control circuitry. The display buffer does not occupy any of the main processors address space but rather is controlled directly by the PVTC. The display buffer is made up of four 1024 x 4 bit static RAMs, giving a total capacity of 2 Kbytes, which is sufficient to store one full display screen. To store data in the display buffer, or read data from it, the main microprocessor makes use of one-byte read and write buffers to store the data. Commands are then issued to the PVTC to execute the desired data transfer using the appropriate buffer.

The PVTC derives its timing from an external Character Clock Generator which uses a 13.000 MHz crystal as its time base and generates all the display timing including scan line per character row, video dot timing, composite sync and other control signals necessary to display characters on the video monitor. It also provides consecutive addressing to the display buffer memory and controls the CPU-display buffer interface.

The PVTC contains 8 internal registers which control its operation and can be accessed by the CPU with input/output instructons. These registers allow the PVTC to be programmed for different display formats, and to execute commands. The status of the display can also be read from these registers. Transfer of data between the CPU and the display memory is accomplished via the read and write display buffers. Each buffer appears as a single input/output port to the CPU. To write data to the display memory, the data is first loaded by the CPU into the write buffer. The CPU then outputs the desired cursor or pointer address where the data is to be stored in the cursor or pointer register of the PVTC. The CPU then issues a write command to the PVTC using its command register. The PVTC then retrieves the data from the write buffer and generates the required control signals to store the data at the correct address in the display memory. To read data from the display memory, the CPU first loads the cursor or pointer register with the desired address. The CPU then issues a read command to the PVTC via its command register. The PVTC then generates the appropriate control signals to take the data from the given address in display memory and place it in the read buffer. The CPU can then retrieve the data from the read buffer. The status register of the PVTC must be polled in both cases to ensure that the PVTC can accept a new command and to sense when the data transfer has actually occurred. The PVTC does not actually write any new data to the display memory until the next display blanking interval in order to avoid any visual disturbances (flashing) on the video

screen.

The PVTC can be programmed for a variety of display formats and timing relationships. Two standard setups are provided with the system software to allow suitable displays for either a video monitor or a standard television set with RF modulator. The characteristics for the Monitor and Television modes are summarizd as follows :-

|                           | Monitor  | Television |

|---------------------------|----------|------------|

| Scan Lines per screen     | 216      | 216        |

| No. of Rows per Screen    | 24       | 24         |

| No. of Characters per Row | 80       | 40         |

| Character Clock Frequency | 13.0 MHz | 6.5 MHz    |

| Character Width in dots - | 8        | 7          |

The character clock frequency and character width are controlled by the signal lines 40COL and DIV7-8/ respectively.

The dot pattern for the displayable characters is contained in the 2 Kbyte display character generator ROM. The display memory stores the ROM addresses of the characters to be displayed. The character generator ROM outputs the corresponding dot patterns for the characters to the video shift register. The shift register then shifts the dot pattern out to form the video signal. All timing for the video shift register is controlled by the Character Generator Clock, which also drives the PVTC. The PVTC takes care of all timing and display memory address generation to ensure that the next dot pattern is accessed properly. The PVTC also ensures that the columns and rows of the display are generated in the proper order.

The video attribute circuitry can produce dualintensity, reverse video and black-on-white video effects on the screen depending on the signals HIL, REV and BOW, respectively. Attribute bit CC7, obtained from the display memory along with the ASCII character code, can be used to select either the high intensity or reverse video attribute on a charcter by character basis. The dot pattern shifted out of the video shift register passes through the attribute logic to produce the video output signal.

The composite sync signal generated by the PVTC is combined with the video signal to produce an output which conforms to the EIA RS170 Standard. This signal appears at both Composite Video and RF connectors.

#### 3.6 Floppy Disk Controller

The PIED PIPER's Floppy Disk Drive Controller is built Disk around the Western Digital FD1793 Floppy Formatter/Controller which is configured for 5 1/4" Mini Floppy Disk Drives in double density format. The controller performs all the functions necessary to read and write data to the drive. For the Disk Read operation, data from the disk in Modified-Frequency-Modulated (MFM) format is fed into the Data Separator circuit, made up of a FDC 9216, to The retrieve the RAW READ data and the READ CLOCK signals. serial data is then formed up into words and transferred to the CPU via the Data Bus Lines. The read operation continues until the end of the sector is reached and the Interrupt request line is set.

For the Disk Write operation, the Write Gate is enabled. Write Data in the form of a series of pulses in MFM format is output to the drive. Write Precompensation is performed digitally by the shift register 74LS195 depending on the states of the Write Data, EARLY and LATE signals. Writing to the disk is inhibited when the Write Protect input is at a logical low, in which case any Write Command is immediately terminated.

Connector J12 is a 40 pin male connector for hook up to 5 1/4" mini floppy disk drives. It consists of all the signals required for disk read/write data transfer, motor stepping and step direction, drive status and drive selection.

The signal descriptions are as follows :-

| <u>Signal Name</u> | Signal flow | Functional Description                                                                                                                                                                      |

|--------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DR1/               | Ouptut      | Enables Drive A.                                                                                                                                                                            |

| DR2/               | Output      | Enables Drive B.                                                                                                                                                                            |

| MOTOREN/           | Output      | Enables the drive motor.                                                                                                                                                                    |

| DIR/               | Output      | Controls the direction of<br>Read/Write head movement.<br>Low indicates movement away<br>from the centre of the<br>drive and high indicates<br>movement towards the centre<br>of the drive. |

| STEP/              | Output      | Steps the read/write head<br>by one track for each step<br>pulse output. The direction<br>is specified by DIR/.                                                                             |

HARDWARE

| <u>Signal Name</u> | <u>Signal flow</u> | Functional Description                                                                                                                       |

|--------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| SS/                | Output             | Side Select. It is low when<br>side 1 of the diskette is<br>selected and high when side<br>0 is selected.                                    |

| WD                 | Output             | Writes data to the diskette<br>in MFM format.                                                                                                |

| WG/                | Output             | Write Gate Enable. It must<br>be turned on when writing<br>is to be performed on the<br>diskette.                                            |

| RD                 | Input              | Reads data from the<br>diskette.                                                                                                             |

| Index/             | Input              | Index Hole Detect. This<br>line is low when the index<br>hole is encountered on the<br>diskette.                                             |

| TRK00/             | Input              | Track Zero Indicator. This<br>line is low when the drive<br>head is positioned at track<br>zero and high when it is<br>away from track zero. |

| WPRT/              | Input              | Diskette Write Protect.<br>This line is low when the<br>diskette is write<br>protected.                                                      |

## 3.7 Hard Disk Interface

This is a 40 pin male connector which is configured to hook up to Western Digital's WD1000 Series Winchester Hard Disk Controller. It consists of an eight bit bi-directional data bus, three bit address bus and seven control lines. All commands, status and data are transferred over this bus. The signal descriptions are as follows :-

24

| <u>Signal Name</u> | Signal flow    | Functional Description                                                                                                                                                                    |

|--------------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HDAL0-HDAL7        | Bi-directional | Data Bus Lines. These<br>eight bi-directional data<br>lines transmit and<br>receive data to and from<br>the hard disk controller.<br>HDAL7 is the most<br>significant bit.                |

| AB0-AB2            | Output         | Address Bus Lines. These<br>three bit address lines<br>are used to select one of<br>the eight registers in<br>the hard disk controller.<br>AB2 is the most<br>significant bit.            |

| CS6/               | Output         | I/O Select. This line is<br>activated when data is to<br>be read from or written<br>to the hard disk<br>controller.                                                                       |

| IOWR'/             | Output         | Write Command. It<br>indicates that data on<br>the data bus lines is to<br>be accepted by the hard<br>disk controller and put<br>into the registers<br>specified by the address<br>lines. |

| IORD'/             | Output         | Read Command. It<br>indicates that the<br>contents of the register<br>whose address is<br>specified by the address<br>lines are to be placed<br>onto the data lines.                      |

| WAIT'/             | Input          | This line should be low<br>when data bus lines are<br>not valid on a read<br>command or when data has<br>not been accepted on a<br>write command.                                         |

| HINTRQ'            | Input          | This line should be high<br>whenever the hard disk<br>controller has completed<br>the read or write<br>command.                                                                           |

| <u>Signal Name</u> | Signal flow | Functional Description                                                     |

|--------------------|-------------|----------------------------------------------------------------------------|

| HDRQ '             | Input       | This line should be high<br>whenever the sector<br>buffer of the bard disk |

whenever the sector buffer of the hard disk controller contains data to be read from it, or is waiting for data to be loaded into it. It should be reset whenever the Data Register is read from or written to. The toggling should continue until the buffer is empty.

Hard Disk Reset. This line is used to reset the hard disk to its initial state.

#### 3.8 Parallel Output (Printer) Port

Output

HDRES'/

This is a 15 pin D-type female connector which can be used to attach any Centronics compatible printer. It consists of eight data lines and two control lines for printer handshaking. The signal descriptions are as follows:-

| <u>Signal Name</u> | <u>Signal Flow</u> | Description                                                                                                                                                                    |

|--------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DATA1-DATA8        | Output             | Data Lines. These eight data<br>lines are used to transmit<br>data to the printer. DATA8<br>is the most significant bit.                                                       |

| DSTR/              | Output             | Data Strobe. This line is<br>set to a low level by system<br>software when the data lines<br>contain a character to be<br>printed. It is returned<br>high after a short delay. |

| PRBUSY             | Input              | This line should be high<br>when the printer is busy or<br>not ready to receive data<br>from the printer port.                                                                 |

#### 3.9 Speaker

The PIED PIPER's internal speaker is driven by a Darlington amplifier circuit which delivers about 0.5 watt into an 8 Ohm load. The speaker connector [J6] is a 2 pin connector. The Darlington amplifier gets its signal from bit 7 of the system CONTROL REGISTER II. To produce a tone from the speaker, this bit must be repetitively set and reset at a rate which determines the frequency of the tone. A program example for generating a 1 kHz tone is given in Section 4.8.

#### 3.10 Expansion Board Interface

There are two 28 pin single row male connectors [J7 & J8] on the board which are used to interface with the expansion card options. They may also be used to interface with user designed I/O devices, provided such devices do not present a safety hazard and meet the Class B FCC requirements.

The signal descriptions and Pin Assignments for Connector [J7] are as follows :-

| <u>Pin No.</u> | <u>Signal Nam</u> | e Signal Flow         | <b>Description</b> |

|----------------|-------------------|-----------------------|--------------------|

| 1              | AB0               | Ouptut                | Address line O     |

| 2              | ABl               | Output                | Address line l     |

| 3              | AB2               | Output                | Address line 2     |

| 4              | Ground            |                       | Signal Ground      |

| · <b>5</b>     | Ground            |                       | Signal Ground      |

| 6              | +5V               | Output                | +5V DC             |

| 7              | CS5/              | Output                | I/O Select         |

| 8              | <b>RESET</b> /    | Output                | System Reset       |

| 9              | CLK               | Output                | System Clock       |

| 10             | INT1/             | Input                 | Interrupt Request  |

| 11             | AUDIO             | Output                | Audio output to RF |

|                |                   |                       | modulator.         |

| 12             | DB7               | Bi-directional        | Data line 7        |

| 13             | DB6               | <b>Bi-directional</b> | Data line 6        |

| 14             | DB5               | Bi-directional        | Data line 5        |

| 15             | DB4               | <b>Bi-directional</b> | Data line 4        |

| 16             | DB3               | Bi-directional        | Data line 3        |

| 17             | DB2               | <b>Bi-directional</b> | Data line 2        |

| 18             | DBl               | Bi-directional        | Data line l        |

| 19             | DB0               | Bi-directional        | Data line O        |

| 20             | +5V               | Output                | +5V DC             |

| 21             | Ground            |                       | Signal Ground      |

| 22             | Ground            |                       | Signal Ground      |

| <u>Pin No.</u> | <u>Signal Name</u> | <u>Signal Flow</u> | <u>Description</u>    |

|----------------|--------------------|--------------------|-----------------------|

| 23<br>24       | IOWR'/<br>IORD'/   | Output<br>Output   | I/O write<br>I/O read |

| 25             | WAIT/              | Input              | Wait Request          |

| 26             | CS7/               | Output             | I/O select            |

| 27             | +12V               | Output             | +12V DC               |

| 28             | -12V               | Output             | -12V DC               |

Signal descriptions and Pin Assignments for Bus Connector [J8] are as follows:-

| <u>Pin No.</u> | <u>Signal Name</u> | e <u>Signal Flow</u> | Description              |

|----------------|--------------------|----------------------|--------------------------|

| 1              | AB0                | Ouptut               | Address line 0           |

| 2              | ABl                | Output               | Address line l           |

| 2<br>3<br>4    | AB2                | Output               | Address line 2           |

|                | Ground             |                      | Signal Ground            |

| 5              | Ground             |                      | Signal Ground            |

| 6              | +5V                | Output               | +5V DC                   |

| 7              | CS4/               | Output               | I/O Select               |

| 8              | RESET/             | Output               | System Reset             |

| 9              | CLK                | Output               | System Clock             |

| 10             | INT2/              | Input                | Interrupt Request        |

| 11             | AUDIO              | Output               | Audio output to RF       |

|                |                    |                      | modulator.               |

| 12             | DB7                | Bi-directional       | Data line 7              |

| 13             | DB6                | Bi-directional       | Data line 6              |

| 14             | DB5                | Bi-directional       | Data line 5              |

| 15             | DB4                | Bi-directional       | Data line 4              |

| 16             | DB3                | Bi-directional       | Data line 3              |

| 17             | DB2                | Bi-directional       | Data line 2              |

| 18             | DB1                | Bi-directional       | Data line l              |

| 19             | DB0                | Bi-directional       | Data line 0              |

| 20             | +5V                | Output               | +5V DC                   |

| 21             | Ground             |                      | Signal Ground            |

| 22             | Ground             | Output               | Signal Ground            |

| 23<br>24       | IOWR'/             | Output               | I/O write                |

| 24<br>25       | IORD'/<br>WAIT/    | Output               | I/O read<br>Wait Request |

| 25             |                    | Input<br>Output      | I/O select               |

| 20             | CS7/<br>+12V       | Output               | +12V DC                  |

| 28             | -12V               | Output               | -12V DC                  |

| 20             | - I Z V            | Julpul               | ILV DC                   |

• •

#### 3.11 Expansion Bus Interface

The PIED PIPER has a 56 pin card edge connector [J1] which can be used to interconnect with external peripherals or I/O expansion cards. The interface contains a subset of the STD bus signals and is intended to be used with an STD bus card cage expansion module. Normally, only I/O port expansion is possible. Expansion of this type should be done with care so as not to exceed the power supply capabilities or interfere with the operation of the main PIED PIPER circuitry.

The PIED PIPER utilizes only the first 64 I/O port addresses from 00H to 3FH for its internal registers, I/O ports and peripheral controllers. The I/O addresses are decoded with a 74LS138 decoder. Each decoded line (CSO/-CS7/) represents a group of eight I/O addresses. Each line must be combined with other control lines to obtain individual I/O address enable lines for specific functions. Users who want to expand the I/O address lines through the Expansion Bus should use addresses from 40H to FFH by decoding the lower eight bit address lines provided by the BUS Connector. I/O Addresses from 00H to 3FH should not be used.

The Expansion BUS organization consists of a power bus, a Data Bus and a Control Bus. The signals are as follows :-

| <u>Signal Name</u> | Signal Flow    | Description                                     |

|--------------------|----------------|-------------------------------------------------|

| DB0-DB7            | Bi-directional | Data Bus lines.                                 |

| AB0-AB7            | Output         | Address Bus Lines.                              |

| WR'/               | Output         | Write to memory or I/O.                         |

| RD'/               | Output         | Read from memory or I/O.                        |

| MREQ/              | Output         | Memory select.                                  |

| RESET/             | Output         | System Reset.                                   |

| INTO/              | Input          | Interrupt Request                               |

| INTAK/             | Output         | Interrupt Acknowledge.                          |

| NMI/               | Input          | Non-Maskable Interrupt.                         |

| WAIT/              | Input          | Wait Request.                                   |

| AUDIO              | Input          | Source for audio signal output to RF modulator. |

| BUSRQ/             | Input          | Bus Request.                                    |

HARDWARE

| <u>Signal Name</u> | Signal Flow | Description                                                         |

|--------------------|-------------|---------------------------------------------------------------------|

| BUSAK/             | Output      | Bus Acknowledge.                                                    |

| IORQ'/             | Output      | I/O Request.                                                        |

| CS7/               | Output      | I/O Select. Also used<br>by Peripheral Card<br>Connector J7 and J8. |

| CLK                | Output      | Clock from processor.                                               |

#### 3.12 Floppy Disk Drive

The floppy disk drive is a Mitsubishi model M4853 double-sided, double bit and double track density, halfheight unit using standard double density, 96TPI 5.25 in. diskettes. It uses a circular gimbal spring in the read/write head suspension mechanism to improve medium tracking performance. The steel band drive system for positioning achieves an inter-track access time of just 3 msec. A maintenance-free, DC, brushless, direct-drive motor is employed to eliminate the drive belt of other units. The unit provides a storage capacity of up to 1000 Kbytes unformatted, or 800 Kbytes formatted.

The performance features of the unit are summarized as follows:

| Transfer Rate<br>Avg. Latency Time<br>Access Time | 250 Kbits/sec<br>100 msec |

|---------------------------------------------------|---------------------------|

| Track to Track                                    | 3 msec                    |

|                                                   | 94 msec                   |

| Average<br>Settling Time                          | 15 msec                   |

| Head Load Time                                    | 50 msec                   |

| Motor Start Time                                  | 250 msec                  |

| Recording Density                                 | 5922 bits/in.             |

| Encoding Method                                   | MFM                       |

| Track Density                                     | 96 tracks/in.             |

| Number of Cylinders                               | 80                        |

| Number of Tracks                                  | 160                       |

| Number of Heads                                   | 2                         |

| Rotation Speed                                    | 300 RPM                   |

| MTBF                                              | 10,000 POH or more        |

| MTTR                                              | 30 min.                   |

| Error Rate                                        | •                         |

| Soft Read Error                                   | $10^{-9}$ bit             |

| Hard Read Error                                   | $10^{-12}$ bit            |

| Seek Error                                        | 10 <sup>-6</sup> seek     |

|                                                   |                           |

DC Power Requirements +5 V +12 V

0.5 A typical 0.7 A typical (seek)

#### 3.13 Power Supply

The switching power supply is a Sanyo model MC-040BL. This is a triple output supply with a 72 % conversion efficiency. The outputs are rated at +5 V at 3 A, +12 V at 2 A, and -12 V at 0.5 A. All outputs have foldback overcurrent protection. The input AC requirements are 85-132 VAC at 55 +/-10 Hz.

The total current requirements of the standard PIED PIPER are 1.5 A at +5 V, 5 mA at +12 V, and 0 mA at - 12 V. Before adding any user-designed expansion boards to the system which use the excess capacity of this supply, the user should total up the current requirements of the PIED PIPER and any expansion boards or peripherals.

The power supply is protected on the AC line side by a 3.15 A fuse. The rating of this fuse should not be changed under any circumstances.

31

## CHAPTER 4 SOFTWARE

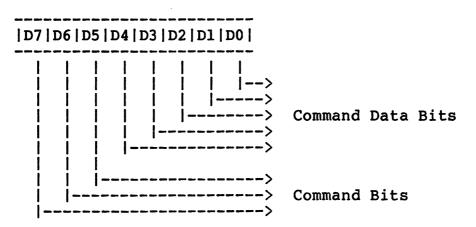

This Chapter describes how the software interacts with the PIED PIPER hardware. The computer uses three internal control/status registers to provide program interaction with the peripherals. In addition, each of the controller chips associated with the peripherals contains internal registers which must be programmed for proper operation. The function of each of these registers will be explained in the following sections, along with some programming examples.

## 4.1 System Control/Status Registers

There are two system control registers (CONTROL REGISTER I and CONTROL REGISTER II) and one system status register (STATUS REGISTER). The control registers are write-only, and the status register is read-only. It is therefore necessary to keep a record of the current contents of the control registers in memory. Every time a control register is to be modified, its contents must first be obtained from the associated memory location, the appropriate bits modified, the memory location updated, and finally the new value written to the control register. The programming examples in the following sections will reflect this approach

The functions provided by the control registers include:

- floppy disk drive selection

- disk drive read/write head/side selection

- output printer port data strobe

- interrupt enable

- keyboard scan enable/disable

- video display mode selection

- ROM enable/disable

- implementation of bell

The information provided by the status register includes:

- interrupt status

- capital lock key status

- output printer port ready status

- floppy disk drive index hole sense

- keyboard scan reference

The addresses asigned to the system control/status registers are as follows:

| CONTROL REGISTER I:  | <b>18H -</b> Write-only |

|----------------------|-------------------------|

| CONTROL REGISTER II: | <b>1DH</b> - Write-only |

| STATUS REGISTER:     | 18H - Read-only         |

The current contents of CONTROL REGISTER I are saved in memory location **FFE2H**; that of CONTROL REGISTER II are saved in memory location **FFE0H**.

## 4.1.1 CONTROL REGISTER I

The bits of CONTROL REGISTER I are defined as follows:

|D7|D6|D5|D4|D3|D2|D1|D0| | | | | | | | | > Floppy Disk Drive A Select | | | | | | | | ->> Floppy Disk Drive B Select | | | | | | | ---->> Floppy Disk Side Select | | | | | ---->> Floppy Disk Side Select | | | | ---->> Output Printer Port Data Strobe | | | ---->> Keyboard Interrupt Enable | | ---->> Timer Interrupt Enable | | ---->> Hard Disk Interrupt Enable

Drive A Select:

A "1" level in bit D0 will select floppy disk drive A as the active drive. A "0" level will deselect drive A. Bits D0 and D1 cannot both be "1" simultaneously.

Drive B Select:

A "1" level in bit D1 will select floppy disk drive B as the active drive. A "0" level will deselect drive B. Bits D0 and D1 cannot both be "1" simultaneously.

## Floppy Disk Side Select:

If bit D2 is a "O" level, then side 0 of the floppy disk drive is selected. A "l" value selects side 1.

## Output Printer Port Data Strobe (DSTR):

This bit supplies the data strobe signal (DSTR/) to the output printer port [pin number 7 of connector J3]. This bit should be set to a "1" level after data has been written to the output port, and then returned to a "0" level after a suitable delay. See Section 4.7 for details on the printer port. (Bit D3 is an inverted version of the actual signal sent to the printer)

#### Keyboard Interrupt Enable:

If bit D4 is a "1" level, then the keyboard controller interrupt is enabled. An interrupt signal is generated whenever there is data in the keyboard controller FIFO RAM. The interrupt signal is removed every time data is read from this FIFO, but will return high if there is still data in the FIFO. A "0" level disables keyboard controller interrupts, and the only way of sensing the presence of characters in the FIFO is to poll the system STATUS REGISTER or the keyboard controller status register.

#### Timer Interrupt Enable:

The keyboard controller contains a programmable timer. This timer generates an interrupt signal every 10.24 msec. If bit D5 is a "1" value, this timer interrupt is enabled. A "0" value disables the timer interrupt. Operation of the timer is described in Section 4.2.

## Hard Disk Interface Enable:

If bit D6 is a "l" value, then the hard disk interface interrupt is enabled. A "0" value disables the interrupt signal.

## Keyboard Scan Disable:

If bit D7 is a "l" value, then keyboard scanning is disabled. A "O" value enables keyboard scanning to continue. This signal is used to implement the "auto-repeat" feature for the keyboard.

## Initialization:

After system initialization, the value contained in CONTROL REGISTER I is:

D7 D6 D5 D4 D3 D2 D1 D0 0 0 1 0 0 0 1

#### Programming Example:

The following program demonstrates how the contents of a control register can be altered. In this case, it is desired to enable the timer interrupt.

| LD  | A,(OFFE2H) | ; GET CURRENT VALUE  |

|-----|------------|----------------------|

| SET | 5,A        | ; SET TIMER ENABLE   |

| LD  | (OFFE2H),A | ; SAVE CHANGED VALUE |

| OUT | 18H,A      | ; ENABLE TIMER       |

#### **4.1.2 CONTROL REGISTER II**

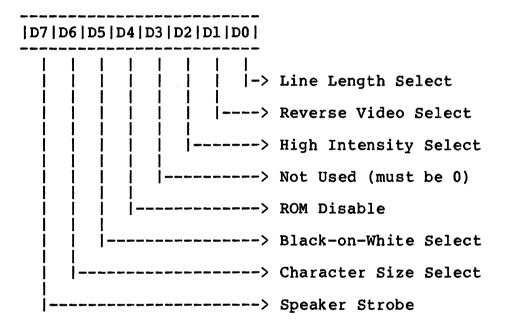

The bits of CONTROL REGISTER II are defined as follows:

Line Length Select:

If bit D0 is a "1" value, then a 40 column line length is selected for the display. This is required if the RF modulator and standard television is used. A "0" value selects an 80 column line length for use with a video monitor.

## Reverse Video Select:

If bit Dl is a "l" value, then the reverse video attribute is selected for the display. In this mode, each character can appear as black dots in a white character block, or in the normal mode of white dots in a black character block. If bit Dl is a "0" value, this display attribute is disabled. Note that only one of bits Dl or D2 can be set to "l" at the same time.

## High Intensity Select:

If bit D2 is a "1" value, then the high intensity attribute is selected for the display. In this mode, characters can appear in either normal or high intensity. A "0" value disables this display attribute. Note that only one of bits D1 or D2 can be set to "1" at the same time.

#### ROM Disable:

If bit D4 is a "1" value, then the system EPROM is disabled (does not exist in processor memory space). If bit D4 is a "0" value, then the lower 32 Kbytes of system RAM are disabled and the system EPROM is enabled and occupies system memory space starting at address 0000H. Note that the EPROM is actually not dsiabled/enabled until the next time the STATUS REGISTER is read after changing bit D4.

## Black-on-White Select:

If bit D5 is a "1" value, then the display is changed to produce black characters on a white background. This format applies to the entire display, and is not a character attribute like reverse video. If bit D5 is a "0" value, then a normal display of white characters on a black background is produced.

## Character Size Select:

If bit D6 is a "1" value, then the character block size is selected to be 7 dots wide for the display. If bit D6 is a "0" value, then the character block size will be 8 dots wide.

#### Speaker Strobe:

Bit D7 produces the signal which drives the internal speaker line. This bit should be alternately set to "1" and "0" levels to produce a continuous tone from the speaker. The pitch of the tone is determined by the frequency with which the bit is being changed. Note that since this technique drives the speaker with a square wave, as opposed to a sinewave, the emitted tone will not be pure but will contain many harmonics.

## Initialization:

After system initialization, the contents of CONTROL REGISTER II are as follows:

D7 D6 D5 D4 D3 D2 D1 D0 0 1 0 1 1 1 0 0

## Programming Example:

The system EPROM can be disabled or enabled by reading the STATUS REGISTER after modifying bit D4 of CONTROL REGISTER II. This capability is useful for OEM users who would like to customize the PIED PIPER for specialized applications by placing their own software routines in EPROM.

To disable the EPROM, bit 4 of CONTROL REGISTER II must be set. The next time the STATUS REGISTER is read, the ROM will be disabled. To enable the EPROM after it has been disabled, bit 4 of CONTROL REGISTER II must be reset, and the STATUS REGISTER must be read. The following programs illustrate how to enable/disable the system EPROM.

Instructions to disable the EPROM:

| Set | A,(OFFEOH)<br>4,A<br>(OFFEOH),A | ; GET CURRENT MODE<br>; SET TO DISABLE ROM |

|-----|---------------------------------|--------------------------------------------|

|     | 1DH,A<br>A,18                   | ; DISABLE ROM                              |

Instructions to enable the EPROM:

| LD  | ,          | - |      |      | RRENT M |     |

|-----|------------|---|------|------|---------|-----|

| RES | 4,A        | ; | SET  | TO   | ENABLE  | ROM |

| LD  | (OFFEOH),A |   |      |      |         |     |

|     | 1DH,A      |   |      |      |         |     |

|     | •          | - |      | от р | DOM     |     |

| IN  | A,18       | 7 | ENAI | апе  | KUM     |     |

SOFTWARE

#### **4.1.3 STATUS REGISTER**

#### Interrupt Pending:

If bit D0 is a "1" level, then one of the system interrupts (given by the contents of bits D1-D3) is pending. Note that this signal will occur even if the interrupt producing it is not enabled. If bit D0 is a "0" value, then no system interrupts are pending.

#### Interrupt Source:

Bits D1, D2, and D3 are used to form up a three-bit address which indicates the highest priority interrupt which is pending. The following list gives the address assignments for the interrupts, in order from highest to lowest priority:

<u>D3 D2 D1</u>

#### Source

| 0 | 0 | 0 | Disk Controller Data Request (DRQ) |

|---|---|---|------------------------------------|

| 0 | 0 | 1 |                                    |

| 0 | 1 | 0 | Video Controller Interrupt         |

| 0 | 1 | 1 | Keyboard Controller Interrupt      |

| 1 | 0 | 0 | Timer Interrupt                    |

| 1 | 0 | 1 | Expansion Connector J8 Interrupt   |

| 1 | 1 | 0 | Expansion Connector J7 Interrupt   |

| 1 | 1 | 1 | Expansion Bus Jl Interrupt         |

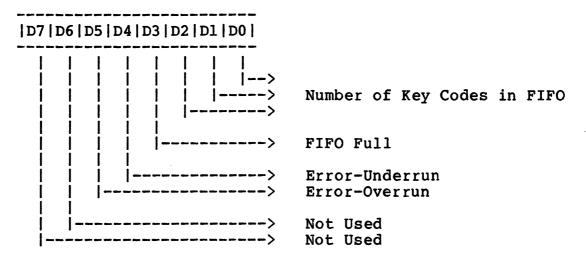

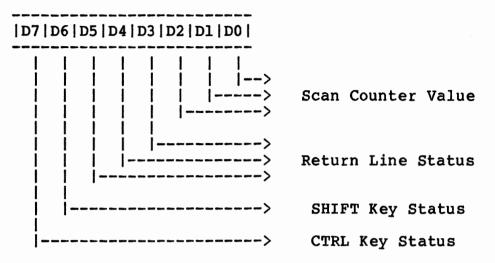

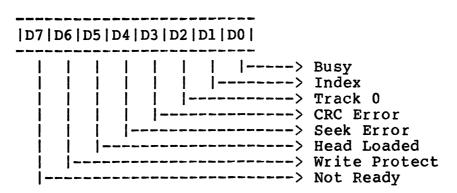

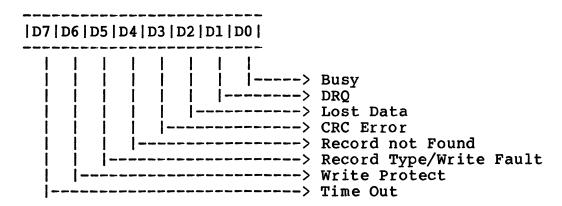

Capital Lock Key Status: