GA22-7139-02

Enterprise System/9000 Models 520, 640, 660, 740, 820, 860, and 900

Functional Characteristics and Configuration Guide

GA22-7139-02

#

Enterprise System/9000 Models 520, 640, 660, 740, 820, 860, and 900

# Functional Characteristics and Configuration Guide

---- For questions or problems regarding this publication:

In the U.S.A., Canada, and Puerto Rico, call

# 1-800-426-9021

In **all countries**, either mail the Readers' Comment Form or FAX the Readers' Comment Form to

# 1-914-432-9405 (FAX number)

**Note:** In countries other than the U.S.A., Canada, and Puerto Rico, dial the appropriate international access code before the above FAX number.

#### Note

Before using this information and the product it supports, be sure to read the general information under "Notices" on page xi.

#### Third Edition (September 1991)

This edition obsoletes and replaces GA22-7139-1. Changes or additons to the text and illustrations are indicated by a vertical line to the left of the change. Make sure you are using the correct edition for the level of the product.

Order publications through your IBM representative or the IBM branch office serving your locality. Publications are not stocked at the address given below.

A form for readers' comments appears at the back of this publication. If the form has been removed, address your comments to:

IBM Corporation, Department B97 P.O. Box 950 Poughkeepsie, NY 12602 U.S.A.

When you send information to IBM, you grant IBM a nonexclusive right to use or distribute the information in any way it believes appropriate without incurring any obligation to you.

#### © Copyright International Business Machines Corporation 1990, 1991. All rights reserved. Note to U.S. Government Users — Documentation related to restricted rights — Use, duplication or disclosure is subject to restrictions set forth in GSA ADP Schedule Contract with IBM Corp.

# Contents

1

| Notices                                   | xi<br>xi            |

|-------------------------------------------|---------------------|

| What is Included in This Publication      | xiii<br>xiii<br>xiv |

| Summary of Changes                        | xv                  |

|                                           | 1-1                 |

|                                           | 1-2<br>1-2          |

|                                           | 1-2                 |

|                                           | 1-3<br>1-3          |

|                                           | 1-3                 |

|                                           | 1-3                 |

|                                           | 1-4                 |

|                                           | 1-4                 |

|                                           | 1-5                 |

|                                           | 1-5                 |

|                                           | 1-6                 |

|                                           | 1-7                 |

|                                           | 1-7                 |

| <b>103</b>                                | 1-8                 |

| ;                                         | -10                 |

|                                           | -10                 |

|                                           | -10                 |

|                                           | -11                 |

|                                           | -11                 |

|                                           | -11                 |

|                                           | -11                 |

|                                           | -12                 |

| regramming export                         | -12                 |

|                                           | -13                 |

|                                           | -13                 |

|                                           |                     |

| Chapter 2. Characteristics of the ES/9000 | 2-1                 |

|                                           | 2-2                 |

| Machine Requirements                      | 2-2                 |

|                                           | 2-3                 |

| Corequisite Requirements                  | 2-3                 |

| Optional Machines and Features            | 2-4                 |

| Console and Display Configuration         | 2-4                 |

| Power and Cooling Functions               | 2-4                 |

| Power                                     | 2-5                 |

| Cooling                                   | 2-5                 |

| Input/Output Operations                   | 2-5                 |

| Storage Operations                        | 2-6                 |

| Data Representation                       | 2-7                 |

| System Security                           | 2-7                 |

| Data Integrity                            | 2-7                 |

en Son dan Brentoma Anderra Secondaria (Britan

| System Access Control                                          | 2-7          |

|----------------------------------------------------------------|--------------|

| IBM 9022 Processor Controller                                  |              |

| Reliability, Availability, and Serviceability                  |              |

| Reliability                                                    |              |

| Availability                                                   | 2-9          |

| Serviceability                                                 | <b>2-1</b> 0 |

|                                                                |              |

| Chapter 3. Processor Components                                | 3-1          |

| Overview                                                       | 3-2          |

| Central Processors                                             | 3-3          |

| Control Storage Element                                        | 3-3          |

| Buffer Control Element                                         | 3-4          |

| Instruction Element                                            | 3-4          |

| Execution Element                                              | 3-5          |

|                                                                | 3-5          |

| Vector Facility Feature                                        | 3-6          |

| Integrated Cryptographic Feature                               | 3-7          |

| Storage                                                        | 3-8          |

| Common Storage Buffer Element                                  | 3-9          |

| Central Storage Element                                        | 3-9          |

|                                                                | 3-11         |

|                                                                | 3-11         |

|                                                                | 3-12         |

| Channels                                                       | 3-12         |

|                                                                |              |

| Chapter 4. Consoles and Displays                               | 4-1          |

| Overview                                                       | 4-2          |

| System Console Interactive Facilities                          | 4-3          |

| System Definition                                              | 4-3          |

| LPAR Mode Definition                                           |              |

| System Activity Display                                        |              |

| I/O Configuration Data Set Content                             |              |

| I/O Problem Determination Information                          | 4-4          |

| Chapter 5. Understanding the 0000 Dresses Controller           | 5-1          |

| Chapter 5. Understanding the 9022 Processor Controller         |              |

| Overview                                                       |              |

|                                                                | 5-2          |

| System Power Panel                                             | 5-3          |

| Dual Support Processors       Operation Monitoring and Control | 5-4          |

|                                                                | 5-4          |

|                                                                | 5-4          |

| Remote Support Facility                                        | 5-4          |

| RSF Configuration                                              | 5-5          |

| Authorization                                                  | 5-5          |

|                                                                | 5-5          |

|                                                                | J-J          |

| Chapter 6. Handling Errors                                     | 6-1          |

| Overview                                                       | 6-2          |

| Automatic Error Recovery                                       | 6-2          |

| Error Checking and Correction                                  | 6-2          |

| Machine-Check Handling                                         | 6-2          |

| I/O Operations                                                 | 6-4          |

| Problem Analysis                                               | 6-5          |

|                                                                | 6-5          |

| Power Malfunction                                              | 0-0          |

| Other Malfunctions                                  | 6-5  |

|-----------------------------------------------------|------|

| Remote Support Facility                             | 6-5  |

| Chapter 7. Standard and Optional Features           | 7-1  |

| Overview                                            | 7-4  |

| Features Dependent on Architectural Mode            | 7-5  |

|                                                     | 7-8  |

| Programming Assists Dependent on Architectural Mode | 7-9  |

|                                                     | 7-10 |

| Access-List-Controlled Protection                   | 7-10 |

|                                                     | 7-10 |

| Basic Control Mode                                  | 7-11 |

| Bimodal Addressing                                  | 7-11 |

| Branch and Save                                     | 7-11 |

|                                                     | 7-11 |

|                                                     | 7-11 |

|                                                     | 7-11 |

| Channels                                            | 7-12 |

| Channel Indirect Data Addressing                    | 7-12 |

| Channel-Set Switching                               | 7-12 |

| Channel Subsystem                                   | 7-12 |

| Channel-Subsystem Call                              | 7-12 |

|                                                     | 7-12 |

|                                                     | 7-12 |

|                                                     | 7-13 |

| Conditional Swapping                                | 7-13 |

| Concurrent CP TCM Maintenance                       | 7-13 |

|                                                     | 7-13 |

|                                                     | 7-13 |

| Console Integration                                 | 7-13 |

|                                                     | 7-13 |

|                                                     | 7-14 |

|                                                     | 7-14 |

|                                                     | 7-14 |

|                                                     | 7-14 |

|                                                     | 7-15 |

|                                                     | 7-15 |

|                                                     | 7-15 |

|                                                     | 7-15 |

|                                                     | 7-16 |

|                                                     | 7-16 |

|                                                     | 7-16 |

|                                                     | 7-16 |

|                                                     | 7-16 |

|                                                     | 7-16 |

| U                                                   | 7-17 |

|                                                     | 7-17 |

|                                                     | 7-17 |

| ·                                                   | 7-17 |

| ······································              | 7-17 |

|                                                     | 7-17 |

|                                                     | 7-17 |

| ······································              | 7-18 |

|                                                     | 7-18 |

| Interpretive Execution                              | 7-18 |

|

1

1

۱

- 10

| Interval Timer                                  | 7-18 |

|-------------------------------------------------|------|

| I/O-Device Self-Description                     | 7-19 |

| I/O Error Alert                                 | 7-19 |

| I/O Interface Reset                             | 7-19 |

| I/O Power Sequence Control                      | 7-19 |

| Key-Controlled Storage Protection               | 7-19 |

| Limited Channel Logout                          | 7-20 |

| Logging Volume Reduction                        | 7-20 |

| Monitoring                                      | 7-20 |

| Move Page                                       | 7-20 |

| Multiprocessing                                 | 7-20 |

| MVS Dynamic Physical Partitioning               | 7-21 |

| Page Protection                                 | 7-21 |

| PER Extensions                                  | 7-21 |

| Preferred Machine Assist                        | 7-21 |

| Private Space                                   | 7-21 |

| Processor Availability Facility                 | 7-21 |

| Processor Resource/Systems Manager              | 7-22 |

| PSW-Key Handling                                | 7-24 |

| Recovery Extensions                             | 7-24 |

| SCP-Initiated Reset                             | 7-24 |

| Service Signal                                  | 7-24 |

| Sorting Instructions                            | 7-24 |

| Storage Background Scrubbing                    | 7-24 |

| Storage-Key Instruction Extensions              | 7-25 |

| Storage-Key Instructions                        | 7-25 |

| Storage-Key 4KB Block                           | 7-25 |

| Storage-Reconfiguration                         | 7-25 |

| Subsystem Storage Protection                    | 7-25 |

| IBM 9037 Sysplex Timer                          | 7-25 |

| System/370 Extended Facility                    | 7-26 |

| Test Block                                      | 7-26 |

| Time-of-Day Clock                               | 7-26 |

| Tracing                                         | 7-27 |

| Translation                                     | 7-27 |

| Vector Facility Feature                         | 7-28 |

| Virtual-Machine Assist                          | 7-28 |

| VM Assists for the CPU Timer                    | 7-28 |

| 3033 Extension                                  | 7-29 |

| 31-Bit Indirect Data Address Word               | 7-29 |

| 31-Bit Real Addressing                          | 7-29 |

|                                                 | 0.4  |

| Chapter 8. Characteristics of Channel Operation | 8-1  |

| Overview                                        | 8-2  |

| Subchannels                                     | 8-2  |

| Channel Control                                 | 8-3  |

|                                                 | 8-3  |

| ESA/390 Mode                                    | 8-3  |

| Chaining                                        | 8-5  |

| I/O Interruptions                               | 8-5  |

| Channel Implementation                          | 8-6  |

| Channel Time-Out Functions                      | 8-6  |

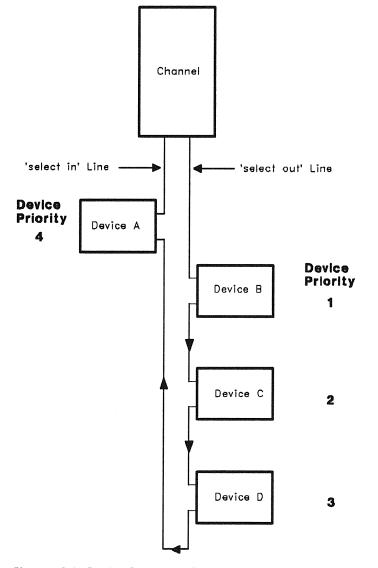

| Device Priority on an I/O Interface             | 8-7  |

| Dynamic Reconnection                            | 8-8  |

I

| Chapter 9. Channel Subsystem Performance                          | 9-1          |

|-------------------------------------------------------------------|--------------|

| Overview                                                          | 9-2          |

| Performance Characteristics                                       | 9-2          |

| Description                                                       | 9-2          |

| I/O Device Characteristics                                        | 9-5          |

| ESCON Channels                                                    | 9-7          |

| Configuring ESCON Channels                                        | 9-7          |

| Elapsed Time                                                      | 9-7          |

| Critical Time                                                     | 9-7          |

| Deferred Access                                                   | 9-8          |

| Parallel Channels Only                                            | 9-9          |

| Device Class                                                      | 9-9          |

| Block Multiplexer Mode of Operation                               | 9-9          |

| ESCON Channels Using Link-Level and Device-Level Protocols        | 9-9          |

|                                                                   | 9-10         |

| -,,,,,,,,,,,-,-,-,                                                | 9-10         |

| Byte Multiplexer Mode and Burst Mode                              | 9-10         |

|                                                                   |              |

|                                                                   | 10-1         |

|                                                                   | 10-2         |

|                                                                   | 10-2         |

| ······································                            | 10-2         |

| · · · · · · · · · · · · · · · · · · ·                             | 10-3         |

|                                                                   | 10-3         |

|                                                                   | 10-3         |

|                                                                   | 10-4         |

| 5                                                                 | 10-5<br>10-5 |

| ······································                            | 10-5         |

|                                                                   | 10-5         |

|                                                                   | 10-6         |

|                                                                   | 10-6         |

|                                                                   | 10-0         |

|                                                                   | 10-7         |

| Appendix A. Architectural Deviations                              | Δ_1          |

| Concurrent Indication of PER Events with Operand-Access Exception |              |

| Protection Violation Instead of Delayed Access Exception          |              |

|                                                                   |              |

| Appendix B. Summary of the Configurations                         | B-1          |

| · · · · · · · · · · · · · · · · · · ·                             |              |

| Glossary of Terms and Abbreviations                               | X-1          |

| -                                                                 |              |

| Index                                                             | X-19         |

VIII Functional Characteristics and Configuration Guide

Figures

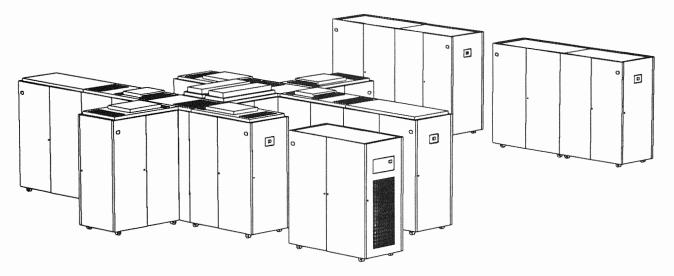

| 1-1. | IBM ES/9000 Model 900                                        | 1-2  |

|------|--------------------------------------------------------------|------|

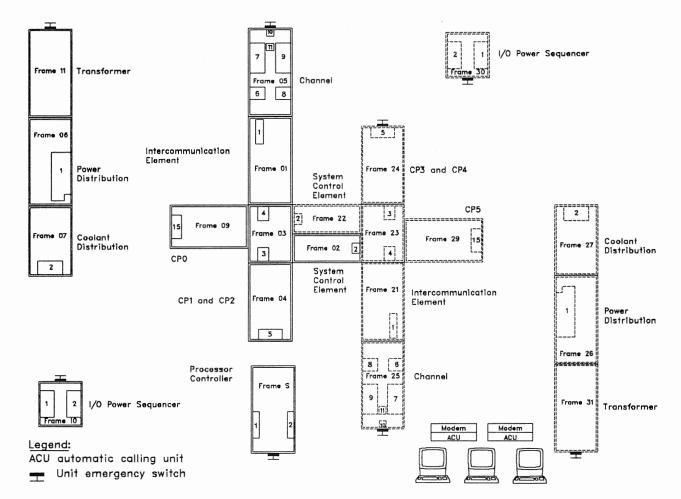

| 2-1. | Unit Identification for the ES/9000 Model 900 (not to scale) | 2-3  |

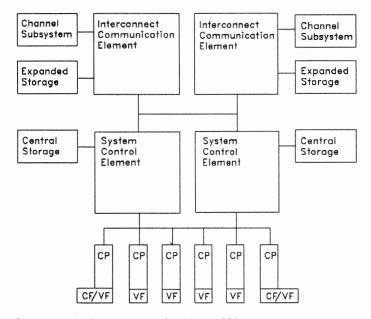

| 3-1. | Components for Model 900                                     | 3-2  |

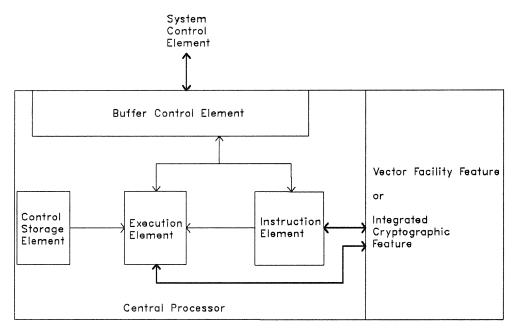

| 3-2. | Elements of a Central Processor                              | 3-3  |

| 3-3. | CPU ID - Doubleword Content in Basic Mode                    | 3-5  |

| 3-4. | CPU ID - Doubleword Content in LPAR Mode                     | 3-5  |

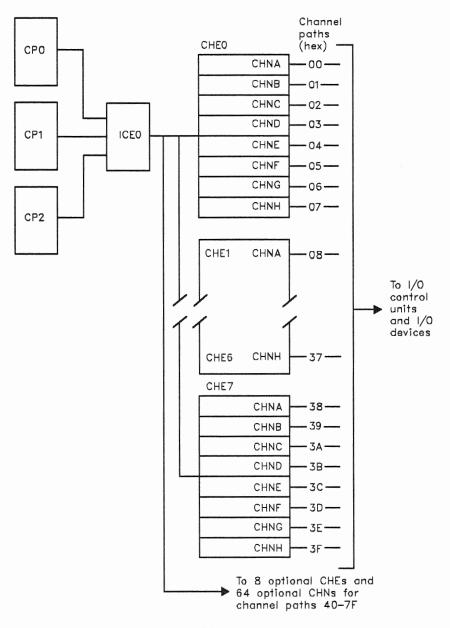

| 3-5. | Channel Subsystem Diagram                                    | 3-14 |

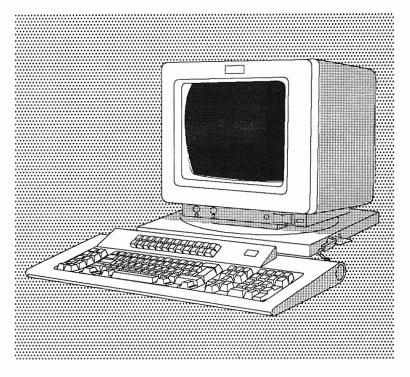

| 4-1. | IBM 3206 Display Station Model 100                           | 4-3  |

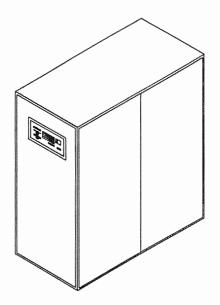

| 5-1. | IBM 9022 Processor Controller Model 1A                       | 5-2  |

| 5-2. | 9022 Model 1A System Power Panel                             | 5-3  |

| 8-1. | Device Priority on Parallel Channels                         | 8-7  |

|      |                                                              |      |

# Tables

| 1-1.         | Upgrade Progression                                              | 1-2  |

|--------------|------------------------------------------------------------------|------|

| 1-2.         | Connectivity Distances Using ESCON XDF                           | 1-9  |

| 3-1.         | HSA Sizing Table in LPAR Mode                                    | 3-11 |

| 6-1.         | Machine-Check Interruption Code (MCIC)                           | 6-4  |

| 7-1.         | Features Dependent on Architectural Mode                         | 7-5  |

| <b>7-2</b> . | Features Not Dependent on Architectural Mode                     | 7-8  |

| 7-3.         | Programming Assists Dependent on Architectural Mode              | 7-9  |

| 9-1.         | Channel Data Rate as a Function of Distance for Models 520 - 900 | 9-5  |

| B-1.         | Summary of the Configurations                                    | B-1  |

# Notices

References in this publication to IBM products, programs, or services do not imply that IBM intends to make these available in all countries in which IBM operates. Any reference to an IBM product, program, or service is not intended to state or imply that only IBM's product, program, or service may be used. Any functionally equivalent program that does not infringe any of IBM's intellectual property rights may be used instead of the IBM product, program, or service. Evaluation and verification of operation in conjunction with other products, except those expressly designated by IBM, is the user's responsibility.

IBM may have patents or pending patent applications covering subject matter in this document. The furnishing of this document does not give you any license to these patents. You can send license inquiries, in writing, to the IBM Director of Commercial Relations, IBM Corporation, Purchase, NY 10577.

# **Trademarks and Service Marks**

The following terms, denoted by an asterisk (\*) in this publication, are trademarks or service marks of IBM the Corporation in the United States or other countries:

AIX AT BookManager CICS/ESA DB2 ECKD Enterprise System/3090 Enterprise System/9000 Enterprise Systems Architecture/370 Enterprise Systems Architecture/390 Enterprise Systems Connection Architecture ESCON ESCON XDF ES/3090 ES/9000 ESA/370 ESA/390 Hardware Configuration Definition Hiperspace IBM **ICRF** IMS/ESA MVS/DFP MVS/ESA MVS/SP Personal Security Personal System/2 PR/SM Processor Resource/Systems Manager

PS/2 S/390 System/370 System/390 VM/ESA VM/XA VSE/ESA 3090

XII Functional Characteristics and Configuration Guide

# About This Publication

This publication describes the IBM\* Enterprise System/9000\* Models 520, 640, 660, 820, 860 and 900, their design, components, functions, features and their capability. It also provides basic guidelines and recommendations for configuring channel loads.

This publication is intended for executives, data processing managers, and data processing technical staff.

Before reading this publication you should be familiar with IBM System/390\* and IBM Enterprise Systems Architecture/390\* (ESA/390\*) as described in *IBM Enterprise Systems Architecture/390 Principles of Operation*, SA22-7201.

You should also be familiar with the IBM Enterprise Systems Connection Architecture\* (ESCON\* Architecture) as described in *Introducing Enterprise Systems Connection*, GA23-0383.

## What is Included in This Publication

This publication contains the following chapters and appendixes:

- Chapter 1, "Introduction" outlines each model's hardware configuration, design highlights, and control programs.

- Chapter 2, "Characteristics of the ES/9000" describes the characteristics of each model.

Chapter 3, "Processor Components" describes the logical components of the processor unit.

- Chapter 4, "Consoles and Displays" describes the interactive consoles and displays, and the facilities provided by the system console.

- Chapter 5, "Understanding the 9022 Processor Controller" describes the 9022 processor controller.

- Chapter 6, "Handling Errors" describes error recovery procedures the processor controller performes automatically, customer problem analysis procedures, and remote support facility procedures.

- Chapter 7, "Standard and Optional Features" describes the standard and optional features.

- Chapter 8, "Characteristics of Channel Operation" describes the characteristics, function, and structure of the channels.

- Chapter 9, "Channel Subsystem Performance" describes ESCON and parallel channel performance concepts and characteristics, and the criteria for determining the sequence of attachment of the input/output (I/O) devices for parallel channels.

- Chapter 10, "Guidelines for Channel Subsystem Configuration" provides recommendations for ESCON channel configurations and describes how to configure I/O devices for operation on block multiplexer or byte multiplexer channels.

- Appendix A, "Architectural Deviations" outlines the exceptions to the *IBM* Enterprise Systems Architecture/390 Principles of Operation.

xiii

• Appendix B, "Summary of the Configurations" contains a table that shows a summary outline of the configurations.

# **Related Publications**

Other IBM publications that you will find helpful and that you should use along with this publication include:

- System/360 and System/370 I/O Interface Channel to Control Unit Original Equipment Manufacturers' Information, GA22-6974.

- System/370: Principles of Operation, GA22-7000.

- System/370: Input/Output Configurator, GA22-7002.

- System/370 Extended Architecture Interpretive Execution, SA22-7095.

- Enterprise Systems Architecture/390 Vector Operations, SA22-7125.

- ES/9000 Processor Complex Models 330, 340, 500, 580, 620, and 720: Functional Characteristics and Configuration Guide, GA22-7138.

- Enterprise Systems Architecture/370: Principles of Operation, SA22-7200.

- Enterprise Systems Architecture/390: Principles of Operation, SA22-7201.

- Enterprise Systems Architecture/390: ESCON I/O Interface, SA22-7202.

- Enterprise Systems Architecture/390: Common I/O Device Commands, SA22-7204.

- Input/Output Device Summary, GA32-0039.

- Input/Output Equipment Installation Manual—Physical Planning for System/360, System/370, and 4300 Processors, GC22-7064.

- ES/9000, ES/3090\* Processor Resource/Systems Manager Planning Guide, GA22-7123.

- ES/9000 Models 330 900 Installation Manual-Physical Planning, GC22-7083.

- ES/9000 Models 520, 640, 660, 740, 820, 860, and 900 Operator Guide, GC38-0086.

- ES/9000 Models 520, 640, 660, 740, 820, 860, and 900 Recovery Guide, GC38-0090.

- ES/9000 Models 520, 640, 660, 740, 820, 860, and 900 Operator Messages, GC38-0094.

- ES/9000 ES/3090 Input/Output Configuration Program User Guide, GC38-0097.

- ES/9000 Models 330 900 Customer Library CD-ROM, GK2T-6685.

- Introducing Enterprise Systems Connection, GA23-0383.

- Introduction to Nonsynchronous Direct Access Storage Subsystems, GC26-4519.

- Enterprise Systems Connection: Planning for Migration, GC66-3181.

# Summary of Changes

This edition contains editorial updates and the following product updates:

- Three new processors Models 520, 640, 660, and 740 to complement Models 820, 860, and 900

- · Enhanced system reliability, availability, and serviceability

- Subsystem storage protection

- Storage background scrubbing

- Concurrent channel maintenance

- Concurrent CP TCM maintenance

- Concurrent power maintenance

- Concurrent sense

- Fault tolerant dynamic memory array

- Enhanced system performance functions

- Enhanced move page for VM

- Extended sorting

- Nine new vector instructions

- Two new scalar square root instructions

- Access-list-controlled protection

- Cancel I/O

- Channel subsystems

- Console integration

- Extended sorting

- I/O interface reset

- MVS dynamic physical partitioning

- Enhanced IBM Sysplex\* Timer functions

- External time source

- Automatic propagation delay adjustment

- New ESCON and channel functions

- ESCON Extended Distance Feature (ESCON XDF\*)

- ESCON data rate increase to 17 MB/sec

- · New Processor Resource/Systems Manager\* (PR/SM\*) functions

- LPAR high-performance parallel interface (HIPPI)

- LPAR support of ICRF

- LPAR preferred path

- LPAR auto-reconfiguration

- LPAR management time report

- · New Integrated Cryptographic Feature (ICRF) function

- ICRF Personal Security\* card

# Chapter 1. Introduction

1

1

| Overview                                                     | 1-2  |

|--------------------------------------------------------------|------|

| Upgrade Progression                                          |      |

| Hardware Configuration                                       | 1-3  |

| Model 520                                                    | 1-3  |

| Model 640                                                    | 1-3  |

| Model 660                                                    | 1-4  |

| Model 740                                                    | 1-4  |

| Model 820                                                    | 1-5  |

| Model 860                                                    | 1-5  |

| Model 900                                                    | 1-6  |

| Design Highlights                                            | 1-6  |

| ESA/390 Architectural Mode of Operation                      | 1-7  |

| Logically Partitioned (LPAR) Operating Mode                  | 1-7  |

| ESCON Architecture and Technology                            | 1-8  |

| ESCON Architecture                                           | 1-8  |

| ESCON Channels                                               | 1-9  |

| Fiber Optic Cabling, Transmission, and Reception             | 1-9  |

| Dynamic Connectivity (Switched Point-to-Point Topology)      | 1-10 |

| Interconnectivity with Other Networks                        | 1-10 |

| Expanded Storage (Optional)                                  | 1-10 |

| Vector Facility Feature (Optional)                           | 1-10 |

| Integrated Cryptographic Feature (Optional)                  | 1-10 |

| IBM 9037 Sysplex Timer Attachment (Optional)                 | 1-11 |

| High Levels of Reliability, Availability, and Serviceability | 1-11 |

| Softcopy Publications                                        | 1-11 |

| Programming Compatibility                                    | 1-11 |

| Programming Support                                          | 1-12 |

| Control Programs for Basic Modes                             | 1-12 |

| Control Programs for Guest                                   | 1-13 |

| Control Programs for Logically Partitioned Operation         | 1-13 |

|                                                              |      |

1-1

# Overview

The IBM ES/9000 9021 family of processors Models 520, 640, 660, 740, 820, 860, and 900 are general-purpose data processing systems that operate in ESA/390 mode (see "ESA/390 Architectural Mode of Operation" on page 1-7). The design of these models combined with their new functions contributes to improved reliability, availability, serviceability and performance. Figure 1-1 shows a standard Model 900.

| Upgrade Progres | ssion                                                                                   |                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                |

|-----------------|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | Models 330<br>provide cor<br>complex. F<br>620, and 72<br>For a list of<br>refer to ES/ | , 640, 660, 740, 820, 860, and 900 pr<br>, 340, 500, 580, 620, and 720. Mode<br>npatible growth from IBM Enterpris<br>for a list of the upgrade progressio<br>0 to Models 520, 640, 660, 740, 820,<br>7 the upgrade progression to Model<br>9000 Models 330, 340, 500, 580, 620<br>Configuration Guide. | Is 330, 340, 500, 580, 620, and 720<br>e System/3090* processor<br>n from Models 330, 340, 500, 580,<br>860, and 900 refer to Table 1-1.<br>s 330, 340, 500, 580, 620, and 720 |

|                 | Table 1-1                                                                               | . Upgrade Progression                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                |

|                 | Model                                                                                   | Upgrade Progression                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                |

|                 | 520                                                                                     | 640 or 660                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                |

|                 | 620                                                                                     | 720 or 820 (see note)                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                |

|                 | 640                                                                                     | 740 or 820                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                |

|                 | 660                                                                                     | 820                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                |

|                 | 720                                                                                     | 820, 860, or 900 (see note)                                                                                                                                                                                                                                                                             |                                                                                                                                                                                |

|                 | 740                                                                                     | 820, 860, or 900                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                |

|                 | 820                                                                                     | 860 or 900                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                |

|                 |                                                                                         |                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                |

860

900

**Note:** Upgrades from 620 to 820 and from 720 to 820, 860, or 900 involve substantial changes to the existing processor.

#### Hardware Configuration

The following describes the hardware configuration for Models 520, 640, 660, 740, 820, 860, and 900.

#### Model 520

Model 520 is a uniprocessor containing one integrated central processor (CP). The CP has access to a common central storage, expanded storage, and channels. Model 520 provides:

- · One integrated CP

- 128MB (MB equals 1 048 576 bytes) minimum of central storage, with a maximum of 256MB

- Channels: 32 minimum, 64 maximum in increments of 16. They can be installed in any valid combination of ESCON and parallel channels: 0, 16, 32, 48, or 64 ESCON channels or 0, 16, 32, or 48 can be parallel channels.

- Ability to operate with as many as seven logical partitions

- An optional shared expanded storage: 256MB, 512MB, 1GB, 1536MB, or 2GB (GB equals 1 073 741 824 bytes)

- An optional Integrated Cryptographic Feature (ICRF) that is mutually exclusive with the vector facility on the CP

- An optional vector facility feature on each CP that is mutually exclusive with ICRF.

#### Model 640

Model 640 is a two-way processor containing two integrated central processors (CPs). Each CP has access to a common central storage, expanded storage, and channels. Model 640 provides:

- Two integrated CPs

- 128MB (MB equals 1 048 576 bytes) minimum of central storage, with a maximum of 512MB, installed in increments of 128MB or 256MB

- Channels: 64 minimum, 128 maximum in increments of 16. They can be installed in any valid combination of ESCON and parallel channels: 16, 32, 48, 64, 80, 96, 112, or 128 ESCON channels or 0, 16, 32, or 48 can be parallel channels.

- · Ability to operate with as many as seven logical partitions

- An optional shared expanded storage: 256MB, 512MB, 1GB, 1536MB, 2GB, 3GB, or 4GB (GB equals 1 073 741 824 bytes)

- An optional Integrated Cryptographic Feature (ICRF) that is mutually exclusive with the vector facility on a CP

• An optional vector facility feature on each CP that is mutually exclusive with ICRF.

| Model 660 |                                                                                                                                                                                                                                                                                                         |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | Model 660 is a two-way multiprocessor containing two integrated central processors (CPs). Each CP has access to a common central storage, expanded storage, and channels. Model 660 provides:                                                                                                           |

| 1         | Two integrated CPs                                                                                                                                                                                                                                                                                      |

|           | <ul> <li>256MB (MB equals 1 048 576 bytes) minimum of central storage, with a<br/>maximum of 512MB, installed asymmetrically in increments of 128MB</li> </ul>                                                                                                                                          |

|           | <ul> <li>Channels: 64 minimum (32 per side), 128 maximum (64 per side) in increments of 16. They can be installed asymmetrically in any valid combination of ESCON and parallel channels: 0, 16, 32, 48 or 64 ESCON channels per side or 0, 16, 32, or 48 can be parallel channels per side.</li> </ul> |

|           | <ul> <li>Ability to operate in a physically partitioned configuration as two<br/>uniprocessors</li> </ul>                                                                                                                                                                                               |

|           | <ul> <li>Ability to operate with as many as seven logical partitions in a single-image<br/>configuration and with as many as 14 logical partitions in a physically parti-<br/>tioned configuration</li> </ul>                                                                                           |

|           | <ul> <li>An optional shared expanded storage: 256MB, 512MB, 1GB, 1536MB, or 2GB<br/>(GB equals 1 073 741 824 bytes) per side</li> </ul>                                                                                                                                                                 |

|           | <ul> <li>An optional Integrated Cryptographic Feature (ICRF) for each side that is<br/>mutually exclusive with the vector facility on a CP</li> </ul>                                                                                                                                                   |

|           | <ul> <li>An optional vector facility feature on each CP that is mutually exclusive with<br/>ICRF.</li> </ul>                                                                                                                                                                                            |

| Model 740 |                                                                                                                                                                                                                                                                                                         |

|           | Model 740 is a three-way (triadic) processor containing three integrated central processors (CPs). Each CP has access to a common central storage, expanded storage, and channels. Model 740 provides:                                                                                                  |

| 1         | Three integrated CPs                                                                                                                                                                                                                                                                                    |

|           | <ul> <li>256MB (MB equals 1 048 576 bytes) minimum of central storage, with a<br/>maximum of 512MB, installed in increments of 256MB</li> </ul>                                                                                                                                                         |

|           | <ul> <li>Channels: 64 minimum, 128 maximum in increments of 16. They can be<br/>installed in any valid combination of ESCON and parallel channels: 16, 32,<br/>48, 64, 80, 96, 112, or 128 ESCON channels or 0, 16, 32, or 48 can be parallel<br/>channels.</li> </ul>                                  |

| 1         | <ul> <li>Ability to operate with as many as seven logical partitions</li> </ul>                                                                                                                                                                                                                         |

|           | <ul> <li>An optional shared expanded storage: 256MB, 512MB, 1GB, 1536MB, 2GB,<br/>3GB, or 4GB (GB equals 1 073 741 824 bytes)</li> </ul>                                                                                                                                                                |

|           | <ul> <li>An optional Integrated Cryptographic Feature (ICRF) that is mutually exclusive with the vector facility on a CP</li> </ul>                                                                                                                                                                     |

|           | <ul> <li>An optional vector facility feature on each CP that is mutually exclusive with<br/>ICRF.</li> </ul>                                                                                                                                                                                            |

|           |                                                                                                                                                                                                                                                                                                         |

# Model 820

Model 820 is a four-way multiprocessor containing four integrated central processors (CPs). Each CP has access to a common central storage, expanded storage, and channels for single-image configuration or for physically partitioned configuration. Model 820 provides:

- Four integrated CPs

- 128MB (MB equals 1 048 576 bytes), 256MB, or 512MB of shared central storage on each side, installed asymmetrically in increments of 128MB and 256MB

- Channels: 64 minimum, 128 maximum per side in increments of 16. They can be installed asymmetrically in any valid combination of parallel and ESCON channels (16 ESCON channels per side are standard); 0, 16, 32, or 48 can be parallel channels and 16, 32, 48, 64, 80, 96, 112, 128, can be ESCON channels.

- Ability to operate in a physically partitioned configuration as two dyadic processors

- Ability to operate with as many as seven logical partitions in a single-image configuration and with as many as 14 logical partitions in a physically partitioned configuration

- An optional shared expanded storage: 256MB, 512MB, 1GB, 1536MB, 2GB, 3GB, or 4GB (GB equals 1 073 741 824 bytes) on each side installed asymmetrically in increments of 256MB and 512MB.

- An optional Integrated Cryptographic Feature (ICRF) for each side that is mutually exclusive with the vector facility on a CP

- An optional vector facility feature for each CP that is mutually exclusive with ICRF.

# Model 860

Model 860 is a five-way multiprocessor containing five integrated central processors (CPs). Each CP has access to a common central storage, expanded storage, and channels for single-image configuration or for physically partitioned configuration. Model 860 provides:

- Five integrated CPs

- 256MB (MB equals 1 048 576 bytes) or 512MB of shared central storage on A-side and 128MB, 256MB, or 512MB of shared central storage on B-side, installed asymmetrically in increments of 128MB and 256MB

- Channels: 64 minimum, 128 maximum per side in increments of 16. They can be installed asymmetrically in any valid combination of parallel and ESCON channels (16 ESCON channels per side are standard); 0, 16, 32, or 48 can be parallel channels and 16, 32, 48, 64, 80, 96, 112, 128, can be ESCON channels.

- Ability to operate in a physically partitioned configuration as one dyadic and one triadic processor

- Ability to operate with as many as seven logical partitions in a single-image configuration and with as many as 14 logical partitions in a physically partitioned configuration

- An optional shared expanded storage: 256MB, 512MB, 1GB, 1536MB, 2GB, 3GB, or 4GB (GB equals 1 073 741 824 bytes) on each side, installed asymmetrically in increments of 256MB, 512MB, and 1GB

- An optional Integrated Cryptographic Feature (ICRF) for each side that is mutually exclusive with the vector facility on a CP

- An optional vector facility feature for each CP that is mutually exclusive with ICRF.

### Model 900

Model 900 is a six-way multiprocessor containing six integrated central processors (CPs). Each CP has access to a common central storage, expanded storage, and channels for single-image configuration or for physically partitioned configuration. Model 900 provides:

- Six integrated CPs

- 256MB (MB equals 1 048 576 bytes) or 512MB of shared central storage on each side, installed asymmetrically in increments of 256MB

- Channels: 64 minimum, 128 maximum per side in increments of 16. They can be installed asymmetrically in any valid combination of parallel and ESCON channels (16 ESCON channels per side are standard); 0, 16, 32, or 48 can be parallel channels and 16, 32, 48, 64, 80, 96, 112, 128, can be ESCON channels.

- Ability to operate in a physically partitioned configuration as two triadic processors

- Ability to operate with as many as seven logical partitions in a single-image configuration and with as many as 14 logical partitions in a physically partitioned configuration

- An optional shared expanded storage: 256MB, 512MB, 1GB, 1536MB, 2GB, 3GB, 4GB (GB equals 1 073 741 824 bytes) on each side, installed asymmetrically in increments of 256MB, 512MB and 1GB

- An optional Integrated Cryptographic Feature for each side that is mutually exclusive with the vector facility on a CP.

- An optional vector facility feature on each CP that is mutually exclusive with ICRF.

# **Design Highlights**

Models 520, 640, 660, 740, 820, 860, and 900 provide high performance and flexibility due to its improved design and use of technology advances. The design of these models incorporates:

- ESA/390 architectural mode of operation

- Logically partitioned LPAR operating mode. LPAR mode provides both ESA/390 and System/370 logical partitions.

- IBM Enterprise Systems Connection Architecture (ESCON Architecture) and technology for the ESCON Channels

- Optional expanded storage

- Optional vector facility feature

- Optional Integrated Cryptographic Feature (ICRF)

- Optional IBM Sysplex Timer attachment

- High levels of reliability, availability, and serviceability (including concurrent CP TCM maintenance, concurrent power maintenance, and concurrent channel maintenance)

- Softcopy publications

# **ESA/390** Architectural Mode of Operation

Models 520, 640, 660, 740, 820, 860, and 900 provide the Enterprise Systems Architecture/390 (ESA/390) mode in three ways:

- Basic mode

- Mode of a logical partition in the LPAR mode

- Mode of a guest virtual machine.

In ESA/390 mode (which includes the functions of ESA/370\* mode), these models have problem-program compatibility with System/360\*, System/370\*, and 4300 processors. They can access virtual storage in multiple address spaces and data spaces. This extends addressability for system, subsystem, and application functions that use ESA/390.

ESA/390 mode provides:

- 31-bit addressing with a virtual address range of 2GB (2 147 483 648 bytes).

- ESCON and parallel channels.

- Channel path selection and I/O-busy-condition management as hardware functions (rather than control program functions) that provide:

- As many as eight channel paths available to each I/O device.

- Increased I/O device accessibility by allowing each central processor to initiate operations with any of the I/O devices and to handle any I/O interruption conditions.

- A significantly extended addressability through access to multiple address spaces and data spaces while maintaining compatibility with existing 24-bit and 31-bit subsystems and user applications. Each address space can contain as many as 2GB of programs and data. Each data space can contain as many as 2GB of data.

- Support for the Start Interpretive Execution (SIE) instruction, allowing support of guest ESA/390 and System/370 virtual machines.

- Support for the VM data space facility which makes the ESA/390 accessregister architecture more useful in virtual machine applications. For more information, see VM/ESA CP Programming Services, SC24-5520.

## Logically Partitioned (LPAR) Operating Mode

You select the operating mode during system initialization (power-on reset). This occurs for a single-image configuration or for each side of a physically partitioned configuration. The operating mode can be basic mode (ESA/390) or LPAR mode. When you select LPAR mode, you must specify the:

- Architectural mode (ESA/390 or System/370) of each partition

- Resources of each partition

You can reconfigure most resources without having to reinitialize the system. Before you can activate partitions, you must define central storage and optional expanded storage to the logical partitions. When a logical partition is activated, the storage resources are allocated in 1MB contiguous blocks. These allocations are dynamically reallocated. After you define and activate a System/370 or ESA/390 logical partition, you can load a supporting operating system into that logical partition.

**Note:** You cannot share allocated central storage or expanded storage among multiple logical partitions.

You can allocate individual channel paths to each logical partition. But a channel path can be allocated only to one logical partition at a time. Also, channel paths can be dynamically reconfigured between logical partitions. To share a device between logical partitions, you must use a separate channel path for each logical partition.

You can now specify preferred channel paths for devices in LPAR mode as well as basic mode. Use IOCP to define a preferred path for a device by coding the PATH parameter in the IODEVICE macroinstruction. For more information refer to the *ES/9000 ES/3090 Input/Output Configuration Program User Guide*, GC38-0097.

CPs can be dedicated to a single logical partition or shared among multiple logical partitions. The allocation of CPs to a logical partition is made when the partition is activated. The use of CP resources shared between logical partitions can be limited and modified by operator commands while the logical partitions are active.

If the optional vector facility feature or the optional ICRF feature is installed on a CP, it is available for use by all the partitions that share that CP. CPs that are dedicated to a logical partition (including associated vector or ICRF facilities) are available only to that logical partition.

# **ESCON** Architecture and Technology

ESCON combines technology, architecture, and a set of interrelated hardware and software products and services that provide:

- ESCON Architecture

- ESCON channels, including the ESCON extended distance feature (ESCON XDF)

- Fiber optic cabling, transmission, and reception

- Dynamic connectivity through switched point-to-point topology and data flow

- Interconnectivity with other networks.

For detailed information about the basic concepts of ESCON technology and architecture, see *Introducing Enterprise Systems Connection*, and *ESA/390 Principles of Operation*.

#### **ESCON Architecture**

ESCON Architecture, a channel architecture, is designed to support the fiber optic environment and dynamic connectivity.

ESCON Architecture uses link-level and device-level protocols for the transfer of information. Link-level protocols establish and maintain the physical and logical path for the transmission and reception of information. Device-level protocols

establish and maintain the transfer of information between a channel and control units that use device-level protocols.

For detailed information about the ESCON interface protocol, see *IBM Enterprise* Systems Architecture/390: ESCON I/O Interface.

#### **ESCON Channels**

ESCON Channels transfer information on a link in a serially transmitted synchronous bit stream (serial transmission) through fiber optic channel cables and:

- · Operate using link-level protocols and device-level protocols, or

- Attach to an IBM 9034 ESCON Converter to attach to control units with parallel interfaces, using bus and tag cable.

For detailed information about the I/O commands used to operate the new ESCON interface protocols in the fiber optic environment, see *IBM Enterprise Systems Architecture/390: Common I/O Device Commands.*

#### Fiber Optic Cabling, Transmission, and Reception

ESCON LED multimode fiber optic technology providing a direct channel attachment range of up to 3 kilometers (1.9 miles); and control units can be attached to a range of up to 9 kilometers (5.6 miles) from a channel through two optional ESCON Directors.

ESCON XDF uses single-mode fiber optic technology providing a direct channel attachment range of up to 60 kilometers (37.3 miles); and control unit attachment range of up 43 kilometers (26.7 miles) from a channel through two optional ESCON directors. The following table shows the maximum cable distances that ESCON I/O devices can be located from the processor using ESCON Directors with ESCON XDF.

| Table 1-2. Connectivity Di                                             | stances Using ESCON XDF                                        |                                                  |

|------------------------------------------------------------------------|----------------------------------------------------------------|--------------------------------------------------|

| Device                                                                 | Maximum Link Distance                                          | Minimum Number of<br>ESCON Directors<br>Required |

| ESCON Converter<br>Models 1 and 2                                      | 3 km (1.9 miles)                                               | 1                                                |

| 9343 Model D04                                                         | 9 km (5.6 miles)                                               | 1                                                |

| 3490 Models A01, A02,<br>A10, A20,D31, D32, D41,<br>and D42 (see note) | 23 km (14.3 miles)                                             | 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 -          |

| 3174 Models 12L and 22L                                                | 43 km (26.7 miles)                                             | 2                                                |

| 3172 Model 1                                                           | 43 km (26.7 miles)                                             | 2                                                |

| ES/9000<br>Channel-to-Channel<br>(CTC)                                 | 60 km (37.3 miles)                                             | 2                                                |

| •                                                                      | t be installed on the IBM 3490<br>distance greater than 9 km f |                                                  |

Combining fiber optic cable with ESCON Architecture, moves data faster than with copper wire cable (bus and tag cable for parallel channels). Using ESCON

channels, data can move at a rate of up to 17 million bytes per second (MB/s) compared to a maximum of 4.5 MB/s when using parallel channels.

### Dynamic Connectivity (Switched Point-to-Point Topology)

Using switched point-to-point topology and ESCON Directors, you can handle many channel and control unit connections simultaneously. The path between each point-to-point interconnection is called a link. With dynamic connectivity:

- Many control units can share a single link to a channel through an ESCON Director.

- Many channels can share a single link to a control unit through an ESCON Director.

- I/O configuration management is simplified through the use of dynamic reconfiguration management.

- Alternate paths can be used if a failure occurs.

#### Interconnectivity with Other Networks

Using the IBM 3172 Interconnect Controller and ESCON interface you can send large amounts of data at wideband speeds to remote processors, or a parallel (bus and tag) interface to an IBM 9034 ESCON Converter to use existing hard-ware and I/O interfaces that access commonly used local area networks.

# **Expanded Storage (Optional)**

Optional high-speed, high-capacity expanded storage is available as an integrated part of the ES/9000 Processor Complex. Expanded storage improves system response and system performance balancing. Models 820, 860, and 900 offer as many as 4GB (4 294 967 296 bytes) of optional expanded storage per side, for a total of 8GB.

See Appendix B, "Summary of the Configurations" for a list of the optional expanded storage for each side.

## **Vector Facility Feature (Optional)**

The optional vector facility feature improves the performance of applications that use a great deal of arithmetic or logical instructions. You can replace the scalar instruction loops with the vector instructions and the application will take advantage of the order inherent in vector data; thereby improving performance.

#### Integrated Cryptographic Feature (Optional)

The optional Integrated Cryptographic Feature (ICRF) improves the security of data. ICRF adheres to international encryption standards and resists tampering. ICRF is available for a central processor on Models 520, 640, and 740 and for one central processor on each side on Models 660, 820, 860, and 900. ICRF is mutually exclusive with the vector facility on a CP and uses the IBM Personal Security\* card to enter cryptographic key information.

For more information refer to "Integrated Cryptographic Feature" on page 3-7.

# **IBM 9037 Sysplex Timer Attachment (Optional)**

The optional IBM 9037 Sysplex Timer, supported by MVS/ESA\* SP Version 4.1 and subsequent releases, synchronizes the processor's time-of-day clock in multiple systems.

## High Levels of Reliability, Availability, and Serviceability

Models 520, 640, 660, 740, 820, 860, and 900 offer high levels of reliability, availability, and serviceability (RAS) by reducing down time and using the following standard features:

- Online error detection and fault isolation techniques

- Concurrent CP TCM maintenance

- · Concurrent channel maintenance

- · Concurrent power maintenance

- Concurrent sense

- Concurrent power subsystem

- · Enhanced power subsystem

- Dynamic modification of the I/O configuration

- · Deferred maintenance capability

- A remote support strategy

- Subsystem storage protection

- Storage background scrubbing

- Fault-tolerant dynamic memory array

- Automatic error detection

For more information, see "Reliability, Availability, and Serviceability" on page 2-8.

## **Softcopy Publications**

All ES/9000 customer publications are available on a CD-ROM disc. To view the CD-ROM disc, you need to use IBM BookManager\* READ licensed programs. One CD-ROM disc is included with the hardcopy publications shipped with all ES/9000 models. You can order, from IBM, additional copies of the CD-ROM disc (GK2T-6685).

### Programming Compatibility

This information applies to Models 520, 640, 660, 740, 820, 860, and 900 having a single-image configuration, independently to each side of an ES/9000 in the physically partitioned configuration, and to operation in a logical partition.

Any program written for ESA/390 mode can operate on Models 520, 640, 660, 740, 820, 860, and 900 operating in ESA/390 mode, provided that the program:

- Is not time-dependent.

- Does not depend on the presence of system facilities (such as storage capacity, I/O equipment, or optional features) when the facilities are not included in the configuration.

- Does not depend on the absence of system facilities when the facilities are included in the configuration.

- Does not depend on results or functions that are defined as unpredictable or model dependent in the IBM Enterprise Systems Architecture/390 Principles of Operation.

- Does not depend on results or functions that are defined in this publication (or, for logically partitioned operation, in the ES/9000, ES/3090 Processor Resource/Systems Manager Planning Guide, GA22-7123.) as being differences or deviations from the appropriate Principles of Operation publication.

- Does not depend on the contents of instruction parameter fields B and C on interception of the SIE instruction. See *IBM System/370 Extended Architec-ture Interpretive Execution* for additional information.

Any problem state program written for System/370 operates in ESA/390 mode and any problem state or control program written for 370-XA or ESA/370 operates in ESA/390 mode, provided that in each case the program:

- Observes the limitations in the preceding statements.

- Does not depend on any programming support facilities that are not provided or that have been modified.

- Takes into account other changes made that affect compatibility between modes. These changes are described in the *IBM Enterprise Systems Architecture/390: Principles of Operation.*

In general, any program, including its programming support, that complies with the programming compatibility statements described above for Models 520, 640, 660, 740, 820, 860, and 900 will operate in a logical partition with the following exceptions:

- VM/XA\* Migration Aid, VM/XA Systems Facility, and VM/XA System Product Release 1 are not supported in a logical partition.

- When operating in a logical partition, the CPU ID presented to that logical partition is not the same as when operating in basic mode. This may impact operation of software products that use the CPU ID field.

For more information, see the *IBM Processor Resource/Systems Manager Plan*ning Guide.

# **Programming Support**

The control program you use depends on the mode in which the processor complex is operating. For example, an ES/9000 operating in ESA/390 mode (basic mode) requires a control program for ESA/390 mode.

The term *basic mode* refers to the mode the processor complex is operating in when it is not operating in LPAR mode. ESA/390 is an example of a basic mode and guest.

# **Control Programs for Basic Modes**

The following IBM control programs operate in basic mode:

- MVS/ESA System Product Version 4 Release 1 and subsequent releases

- MVS/SP Version 3 Release 1 and subsequent releases

- MVS/SP Version 2 Release 2 and subsequent releases

- VM/ESA System Product Releases 1 (ESA Feature) and 1.1

- VM/XA System Product Release 2.1

- Transaction Processing Facility (TPF) Version 3 Release 1

# **Control Programs for Guest**

VM/XA SP Release 2.1 and VM/ESA System Product Releases 1 and 1.1 provide Start Interpretive Execution (SIE) support for the following guest environments when operating in basic mode:

- MVS/SP Release 3.5

- MVS/SP Version 2 Release 1.3

- MVS/SP Version 3 (requires VM/XA System Product Release 2); Release 2.1 supports the use of the Move Page facility by an MVS/SP Version 3 Release 3.1 guest

- VM/SP Release 4

- VM/SP High Performance Option (HPO) Release 4.2

- OS/VS1 Release 7 with Basic Programming Extensions Release 4

- VSE/Advanced Function Version 2 and Version 4

- VSE/SP Version 2, Version 3, and Version 4

- VM/XA Systems Facility (V=V only)

- VM/XA System Product (V=V only, except that a V=R or V=F VM/XA SP 2.1 guest is supported with a VM/XA SP 2.1 host of Models 520, 640, 660, 740, 820, 860, and 900)

- Advanced Interactive Executive/370 (AIX\*/370) (V=V and V=R only).

# **Control Programs for Logically Partitioned Operation**

The following IBM control programs operate in LPAR mode:

- MVS/SP Version 2 Release 1.3 and subsequent releases

- MVS/SP Release 3.5

- VM/SP Release 5 and subsequent releases

- VM/XA SP Release 2.1

- VM/ESA 1 Release 1 (370 Feature)

- VM/SP HPO Release 5.0 and subsequent releases

- VM/SP Release 5 and subsequent releases

- VSE/ESA Release 1

- VSE/SP Version 4 with APAR DY39560

- Transaction Processing Facility (TPF) Version 3 Release 1

- MUSIC/SP Version 2 Release 2 or Version 2 Release 3

- AIX/ESA

The following ESA/390 control programs operate in LPAR mode:

- MVS/ESA Version 4 Release 1 and subsequent releases

- MVS/SP Version 3 Release 1 and subsequent releases

- VM/ESA System Product Release 1 (ESA Feature) and 1.1

For information about the characteristics of those control programs operating in LPAR mode, see the *ES/9000, ES/3090 Processor Resource/Systems Manager Planning Guide*, GA22-7123. Complex, copyrighted and licensed by IBM.

# Chapter 2. Characteristics of the ES/9000

| Dverview                                                                                                                                                                                                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Achine Requirements 2-2                                                                                                                                                                                                                                            |

| Standard Requirements 2-3                                                                                                                                                                                                                                          |

| Corequisite Requirements 2-3                                                                                                                                                                                                                                       |

| Optional Machines and Features                                                                                                                                                                                                                                     |

| Console and Display Configuration 2-4                                                                                                                                                                                                                              |

| Power and Cooling Functions                                                                                                                                                                                                                                        |

| Power                                                                                                                                                                                                                                                              |

| Cooling                                                                                                                                                                                                                                                            |

| nput/Output Operations                                                                                                                                                                                                                                             |

| Channel-to-Channel Connection                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                    |

| ESCON Channels (Attached to a 9034) and Parallel Channels 2-6                                                                                                                                                                                                      |

| ESCON Channels (Using Link-Level and Device-Level Protocols) 2-6                                                                                                                                                                                                   |

| ESCON Channels (Using Link-Level and Device-Level Protocols) 2-6<br>Storage Operations                                                                                                                                                                             |