# VAX MACRO and Instruction Set Reference Manual

Order Number: AA-LA89B-TE

#### June 1990

This document describes the features of the VAX MACRO instruction set and assembler. It includes a detailed description of MACRO directives and instructions, as well as information about MACRO source program syntax.

**Revision/Update Information:**

This manual supersedes the VAX MACRO

and Instruction Set Reference Manual,

Version 5.2

**Software Version:**

VMS Version 5.4

digital equipment corporation maynard, massachusetts

#### June 1990

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

The software described in this document is furnished under a license and may be used or copied only in accordance with the terms of such license.

No responsibility is assumed for the use or reliability of software on equipment that is not supplied by Digital Equipment Corporation or its affiliated companies.

Restricted Rights: Use, duplication, or disclosure by the U.S. Government is subject to restrictions as set forth in subparagraph (c)(1)(ii) of the Rights in Technical Data and Computer Software clause at DFARS 252.227-7013.

© Digital Equipment Corporation 1990.

All Rights Reserved. Printed in U.S.A.

The postpaid Reader's Comments forms at the end of this document request your critical evaluation to assist in preparing future documentation.

The following are trademarks of Digital Equipment Corporation:

| CDA        | DEQNA       | MicroVAX       | VAX RMS           |

|------------|-------------|----------------|-------------------|

| DDIF       | Desktop-VMS | PrintServer 40 | VAXserver         |

| DEC        | DIGITAL     | Q-bus          | <b>VAXstation</b> |

| DECdtm     | GIGI        | ReGIS          | VMS               |

| DECnet     | HSC         | ULTRIX         | VT                |

| DECUS      | LiveLink    | UNIBUS         | XUI               |

| DECwindows | LN03        | VAX            |                   |

| DECwriter  | MASSBUS     | VAXcluster     | digital           |

The following is a third-party trademark:

PostScript is a registered trademark of Adobe Systems Incorporated.

#### **Production Note**

This book was produced with the VAX DOCUMENT electronic publishing system, a software tool developed and sold by Digital. In this system, writers use an ASCII text editor to create source files containing text and English-like code; this code labels the structural elements of the document, such as chapters, paragraphs, and tables. The VAX DOCUMENT software, which runs on the VMS operating system, interprets the code to format the text, generate a table of contents and index, and paginate the entire document. Writers can print the document on the terminal or line printer, or they can use Digital-supported devices, such as the LN03 laser printer and PostScript printers (PrintServer 40 or LN03R ScriptPrinter), to produce a typeset-quality copy containing integrated graphics.

| Ó |

|---|

|   |

|   |

|   |

#### **Contents PREFACE** xxiii **VAX MACRO LANGUAGE CHAPTER 1 INTRODUCTION** 1-1 **CHAPTER 2 VAX MACRO SOURCE STATEMENT FORMAT** 2-1 2.1 LABEL FIELD 2–2 2.2 **OPERATOR FIELD** 2–3 2.3 **OPERAND FIELD** 2-3 2.4 **COMMENT FIELD** 2-3 CHAPTER 3 COMPONENTS OF MACRO SOURCE STATEMENTS 3-1 **CHARACTER SET** 3.1 3-1 3.2 **NUMBERS** 3–2 3.2.1 Integers \_ 3-3 3.2.2 Floating-Point Numbers 3-3 Packed Decimal Strings 3.2.3 3-4 3.3 **SYMBOLS** 3-4 3.3.1 3-5 Permanent Symbols \_\_\_\_\_ 3.3.2 User-Defined Symbols and Macro Names \_\_\_\_\_ 3-5 3.3.3 Determining Symbol Values \_\_\_\_ 3-6

| 3.4     | LOCAL LABELS                         | 3–7  |

|---------|--------------------------------------|------|

| 3.5     | TERMS AND EXPRESSIONS                | 3–9  |

| 3.6     | UNARY OPERATORS                      | 3–10 |

| 3.6.1   | Radix Control Operators              | 3–11 |

| 3.6.2   | Textual Operators                    | 3–12 |

| 3.6.2.1 | ASCII Operator • 3–12                |      |

| 3.6.2.2 | Register Mask Operator • 3–13        |      |

| 3.6.3   | Numeric Control Operators            | 3–14 |

| 3.6.3.1 | Floating-Point Operator • 3–14       |      |

| 3.6.3.2 | Complement Operator • 3–14           |      |

| 3.7     | BINARY OPERATORS                     | 3–15 |

| 3.7.1   | Arithmetic Shift Operator            | 3–16 |

| 3.7.2   | Logical AND Operator                 |      |

| 3.7.3   | Logical Inclusive OR Operator        |      |

| 3.7.4   | Logical Exclusive OR Operator        |      |

| 3.8     | DIRECT ASSIGNMENT STATEMENTS         | 3–17 |

| 3.9     | CURRENT LOCATION COUNTER             | 3–17 |

| ER4 M   | IACRO ARGUMENTS AND STRING OPERATORS | 4–1  |

| 4.1     | ARGUMENTS IN MACROS                  | 4–1  |

| 4.2     | DEFAULT VALUES                       | 4–2  |

| 4.3     | KEYWORD ARGUMENTS                    | 4–3  |

| 4.4     | STRING ARGUMENTS                     | 4–3  |

| 4.5     | ARGUMENT CONCATENATION               | 4–5  |

| 4.6     | 3   | PASSING NUMERIC VALUES OF SYMBOLS |               | 4–6  |

|---------|-----|-----------------------------------|---------------|------|

| 4.7     | 7   | CREATED LOCAL LABELS              |               | 4–7  |

| 4.8     | 3   | MACRO STRING OPERATORS            |               | 4–8  |

| 4.8     | 3.1 | %LENGTH Operator                  |               | 4–8  |

| 4.8     | 3.2 | %LOCATE Operator                  |               | 4–9  |

| 4.8     | 3.3 | %EXTRACT Operator                 |               | 4–10 |

| CHAPTER | ₹ 5 | VAX MACRO ADDRESSING MODES        |               | 5–1  |

| 5.1     | 1   | GENERAL REGISTER MODES            |               | 5–1  |

| 5.1     | 1.1 | Register Mode                     |               | 5-4  |

| 5.1     | 1.2 | Register Deferred Mode            |               | 5–5  |

| 5.1     | 1.3 | Autoincrement Mode                |               | 5–5  |

| 5.1     | 1.4 | Autoincrement Deferred Mode       |               | 5–6  |

| 5.1     | 1.5 | Autodecrement Mode                |               | 5–7  |

| 5.1     | 1.6 | Displacement Mode                 |               | 5–8  |

| 5.1     | 1.7 | Displacement Deferred Mode        |               | 5–9  |

| 5.1     | 1.8 | Literal Mode                      |               | 5–10 |

| 5.2     | 2   | PROGRAM COUNTER MODES             |               | 5–12 |

| 5.2     | 2.1 | Relative Mode                     |               | 5–12 |

| 5.2     | 2.2 | Relative Deferred Mode            |               | 5–13 |

| 5.2     | 2.3 | Absolute Mode                     |               | 5–14 |

| 5.2     | 2.4 | Immediate Mode                    | <del></del>   | 5–14 |

| 5.2     | 2.5 | General Mode                      | <del></del>   | 5–15 |

| 5.3     | 3   | INDEX MODE                        |               | 5–16 |

| 5.4     | 1   | BRANCH MODE                       |               | 5–18 |

| CHAPTER | R 6 | VAX MACRO ASSEMBLER DIRECTIVES    |               | 6–1  |

|         | -   | .ADDRESS                          | 6–4           |      |

|         |     | .ALIGN                            | 6–5           |      |

|         |     | .ASCIX                            | 6–7           |      |

|         |     | ASCIC                             | 6–8           |      |

|         |     | .ASCID                            | 6–9           |      |

|         |     | .70010                            | <del></del> 3 |      |

| .ASCII        | 6–10 |

|---------------|------|

| .ASCIZ        | 6–11 |

| .BLK <i>X</i> | 6–12 |

| .BYTE         | 6–14 |

| .CROSS        | 6–16 |

| .DEBUG        | 6–18 |

| .DEFAULT      | 6–19 |

| .D_FLOATING   | 6–20 |

| .DISABLE      | 6–21 |

| .ENABLE       | 6–22 |

| .END          | 6–25 |

| .ENDC         | 6–26 |

| .ENDM         | 6–27 |

| .ENDR         | 6–28 |

| .ENTRY        | 6–29 |

| .ERROR        | 6–31 |

| .EVEN         | 6–33 |

| .EXTERNAL     | 6–34 |

| .F_FLOATING   | 6–35 |

| .G_FLOATING   | 6–36 |

| .GLOBAL       | 6–37 |

| .H_FLOATING   | 6–38 |

| .IDENT        | 6–39 |

| .IF           | 6-40 |

| .IF_X         | 6–43 |

| .IIF          | 6–46 |

| .IRP          | 6–47 |

| .IRPC         | 6–49 |

| .LIBRARY      | 6–51 |

| .LINK         | 6–52 |

| .LIST         | 6–55 |

| .LONG         | 6–56 |

| .MACRO        | 6–57 |

| .MASK         | 6–59 |

| .MCALL        | 6–60 |

| .MDELETE      | 6–61 |

| .MEXIT        | 6–62 |

| .NARG         | 6–63 |

| .NCHR         | 6–64 |

| .NLIST        | 6–65 |

| .NOCROSS      | 6–66 |

| NOSHOW        | 6_67 |

| .NTYPE         | 6–68  |

|----------------|-------|

| .OCTA          | 6–70  |

| .ODD           | 6–71  |

| .OPDEF         | 6–72  |

| .PACKED        | 6–74  |

| .PAGE          | 6–75  |

| .PRINT         | 6–76  |

| .PSECT         | 6–77  |

| .QUAD          | 6–82  |

| .REFN          | 6–83  |

| REPEAT         | 6–84  |

| .RESTORE_PSECT | 686   |

| .SAVE_PSECT    | 6–87  |

| .SHOW          | 6-89  |

| .SIGNED_BYTE   | 6–91  |

| .SIGNED_WORD   | 6–92  |

| .SUBTITLE      | 6–94  |

| .TITLE         | 6–95  |

| .TRANSFER      | 6–96  |

| .WARN          | 699   |

| .WEAK          | 6–101 |

| .WORD          | 6–102 |

# **VAX DATA TYPES AND INSTRUCTION SET**

| CHAPTER 7 | TERMINOLOGY AND CONVENTIONS | 7–1 |

|-----------|-----------------------------|-----|

| 7.1       | NUMBERING                   | 7–1 |

| 7.2       | UNPREDICTABLE AND UNDEFINED | 7–1 |

| 7.3       | RANGES AND EXTENTS          | 7–1 |

| 7.4       | MD7                         | 7 1 |

| 7.5        | RAZ                             | 7–2               |

|------------|---------------------------------|-------------------|

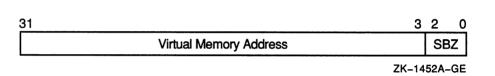

| 7.6        | SBZ                             | 7–2               |

| 7.7        | RESERVED                        | 7–2               |

| 7.8        | FIGURE DRAWING CONVENTIONS      | 7–2               |

| IAPTER 8 E | BASIC ARCHITECTURE              | 8–1               |

| 8.1        | VAX ADDRESSING                  | 8–1               |

| 8.2        | DATA TYPES                      | 8–1               |

| 8.2.1      | Byte                            | 8–1               |

| 8.2.2      | Word                            |                   |

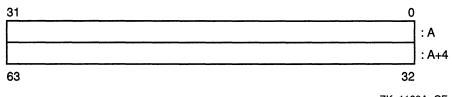

| 8.2.3      | Longword                        | 8–2               |

| 8.2.4      | Quadword                        |                   |

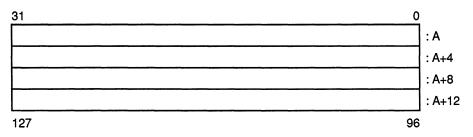

| 8.2.5      | Octaword                        | 8–3               |

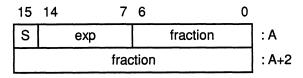

| 8.2.6      | F floating                      | 8–3               |

| 8.2.7      | D floating                      |                   |

| 8.2.8      | G_floating                      |                   |

| 8.2.9      | H floating                      |                   |

| 8.2.10     | Variable-Length Bit Field       | 8–6               |

| 8.2.11     | Character String                |                   |

| 8.2.12     | Trailing Numeric String         | 8–8               |

| 8.2.13     | Leading Separate Numeric String | 8–11              |

| 8.2.14     | Packed Decimal String           | 8 <del>_</del> 13 |

| 8.3        | PROCESSOR STATUS LONGWORD (PSL) | 8–14              |

| 8.3.1      | C Bit                           | 8–15              |

| 8.3.2      | V Bit                           | 8–15              |

| 8.3.3      | Z Bit                           | 8 <del>_</del> 15 |

| 8.3.4      | N Bit                           | 8–15              |

| 8.3.5      | T Bit                           | 8 <del>_</del> 15 |

| 8.3.6      | IV Bit                          | 8 <del>_</del> 15 |

| 8.3.7      | FU Bit                          | 8 <del>_</del> 16 |

| 8.3.8      | DV Bit                          | 8–16              |

| 8.4   | PERMANENT EXCEPTION ENABLES                 |              | 8–16 |

|-------|---------------------------------------------|--------------|------|

| 8.4.1 | Divide by Zero                              |              | 8–16 |

| 8.4.2 | Floating Overflow                           |              | 8–16 |

| 8.5   | INSTRUCTION AND ADDRESSING MODE FORMATS     |              | 8–16 |

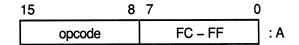

| 8.5.1 | Opcode Formats                              |              | 8–16 |

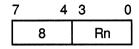

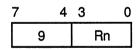

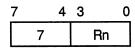

| 8.5.2 | Operand Specifiers                          |              | 8–17 |

| 8.6   | GENERAL ADDRESSING MODE FORMATS             |              | 8–18 |

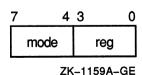

| 8.6.1 | Register Mode                               | <del> </del> | 8–19 |

| 8.6.2 | Register Deferred Mode                      |              | 8–19 |

| 8.6.3 | Autoincrement Mode                          |              | 8–19 |

| 8.6.4 | Autoincrement Deferred Mode                 |              | 8-20 |

| 8.6.5 | Autodecrement Mode                          |              | 8–21 |

| 8.6.6 | Displacement Mode                           |              | 8–21 |

| 8.6.7 | Displacement Deferred Mode                  |              | 8–22 |

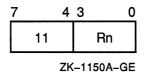

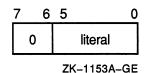

| 8.6.8 | Literal Mode                                |              | 8-23 |

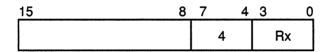

| 8.6.9 | Index Mode                                  | <del></del>  | 8–26 |

| 8.7   | SUMMARY OF GENERAL MODE ADDRESSING          |              | 8–27 |

| 8.7.1 | General Register Addressing                 |              | 8–27 |

| 8.7.2 | Program Counter Addressing                  |              | 8–28 |

| 8.8   | BRANCH MODE ADDRESSING FORMATS              |              | 8–29 |

| ER9 V | /AX INSTRUCTION SET                         |              | 9–1  |

| 9.1   | INTRODUCTION TO THE VAX INSTRUCTION SET     |              | 9–1  |

| 9.2   | INSTRUCTION DESCRIPTIONS                    |              | 9–1  |

| 9.2.1 | Integer Arithmetic and Logical Instructions |              | 9–5  |

|       | ADAWI                                       | 9–7          |      |

|       | ADD                                         | 9–8          |      |

|       | ADWC                                        | 9–9          |      |

|       | ASH                                         | 9–10         |      |

|       | BIC                                         | 9–11         |      |

|       | BIS                                         | 9–12         |      |

|       | BIT                                         | 9–12<br>9–13 |      |

|       |                                             |              |      |

|       | CLR                                         | 9–14         |      |

|       | CMP                                    | 9–15 |      |

|-------|----------------------------------------|------|------|

|       | CVT                                    | 9–16 |      |

|       | DEC                                    | 9–17 |      |

|       | DIV                                    | 9–18 |      |

|       | EDIV                                   | 9–19 |      |

|       | EMUL                                   | 9–20 |      |

|       | INC                                    | 9–21 |      |

|       | MCOM                                   | 9–22 |      |

|       | MNEG                                   | 9–23 |      |

|       | MOV                                    | 9–24 |      |

|       | MOVZ                                   | 9–25 |      |

|       | MUL                                    | 9–26 |      |

|       | PUSHL                                  | 9–27 |      |

|       | ROTL                                   | 9–28 |      |

|       | SBWC                                   | 9–29 |      |

|       | SUB                                    | 9–30 |      |

|       | TST                                    | 9–31 |      |

|       | XOR                                    | 9–32 |      |

| 9.2.2 | Address Instructions                   |      | 9–33 |

|       | MOVA                                   | 9–34 |      |

|       | PUSHA                                  | 9–35 |      |

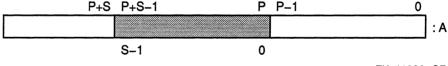

| 9.2.3 | Variable-Length Bit Field Instructions |      | 9–36 |

|       | CMP                                    | 9–38 |      |

|       | EXT                                    | 9–39 |      |

|       | FF                                     | 9–40 |      |

|       | INSV                                   | 9–41 |      |

| 9.2.4 | Control Instructions                   |      | 9-42 |

|       | ACB                                    | 9–44 |      |

|       | AOBLEQ                                 | 9–46 |      |

|       | AOBLSS                                 | 9–47 |      |

|       | В                                      | 9–48 |      |

|       | ВВ                                     | 9–50 |      |

|       | ВВ                                     | 9–51 |      |

|       | ВВ                                     | 9–52 |      |

|       | BLB                                    | 9–53 |      |

|       | BR                                     | 9–54 |      |

|       | BSB                                    | 9–55 |      |

|       | CASE                                   | 9–56 |      |

|       | JMP                                    | 9–58 |      |

|       | JSB                                    | 9–59 |      |

|       | RSB                                    | 9–60 |      |

|       | SOBGEQ                                 | 9_61 |      |

|         | SOBGTR                                  | 9–62  |      |

|---------|-----------------------------------------|-------|------|

| 9.2.5   | Procedure Call Instructions             |       | 9–63 |

|         | CALLG                                   | 9–65  |      |

|         | CALLS                                   | 9–67  |      |

|         | RET                                     | 9–69  |      |

| 9.2.6   | Miscellaneous Instructions              |       | 9–70 |

|         | BICPSW                                  | 9–71  |      |

|         | BISPSW                                  | 9–72  |      |

|         | ВРТ                                     | 9–73  |      |

|         | HALT                                    | 9–74  |      |

|         | INDEX                                   | 9–75  |      |

|         | MOVPSL                                  | 9–77  |      |

|         | NOP                                     | 9–78  |      |

|         | POPR                                    | 9–79  |      |

|         | PUSHR                                   | 9–80  |      |

|         | XFC                                     | 9–81  |      |

| 9.2.7   | Queue Instructions                      |       | 9–82 |

| 9.2.7.1 | Absolute Queues • 9–82                  |       |      |

| 9.2.7.2 | Self-Relative Queues • 9–85             |       |      |

| 9.2.7.3 | Instruction Descriptions • 9–88         |       |      |

|         | INSQHI                                  | 9–89  |      |

|         | INSQTI                                  | 9–91  |      |

|         | INSQUE                                  | 9–93  |      |

|         | REMQHI                                  | 9–95  |      |

|         | REMQTI                                  | 9–97  |      |

|         | REMQUE                                  | 9–99  |      |

| 9.2.8   | Floating-Point Instructions             | 9     | -101 |

| 9.2.8.1 | Introduction • 9–101                    |       |      |

| 9.2.8.2 | Overview of the Instruction Set • 9–103 |       |      |

| 9.2.8.3 | Accuracy • 9–103                        |       |      |

| 9.2.8.4 | Instruction Descriptions • 9–105        |       |      |

|         | ADD                                     | 9–107 |      |

|         | CLR                                     | 9–108 |      |

|         | CMP                                     | 9–109 |      |

|         | CVT                                     | 9–110 |      |

|         | DIV                                     | 9–113 |      |

|         | EMOD                                    | 9–115 |      |

|         | MNEG                                    | 9–117 |      |

|         | MOV                                     | 9–118 |      |

|         | MUL                                     | 9–119 |      |

|         | POLY                                    | 9–120 |      |

|         | SUB                                     | 9–123 |      |

|         | TST                                     | 9–125 |      |

| 9.2.9    | Character String Instructions                    |                | 9-126         |

|----------|--------------------------------------------------|----------------|---------------|

|          | CMPC                                             | 9–128          |               |

|          | LOCC                                             | 9–130          |               |

|          | MATCHC                                           | 9–131          |               |

|          | MOVC                                             | 9–132          |               |

|          | MOVTC                                            | 9–134          |               |

|          | MOVTUC                                           | 9–136          |               |

|          | SCANC                                            | 9–138          |               |

|          | SKPC                                             | 9–139          |               |

|          | SPANC                                            | 9–140          |               |

| 9.2.10   | Cyclic Redundancy Check Instruction              |                | 9–141         |

|          | CRC                                              | 9–142          | •             |

| 9.2.11   | Decimal String Instructions                      |                | 9–144         |

| 9.2.11.1 | Decimal Overflow • 9–145                         |                |               |

| 9.2.11.2 | Zero Numbers • 9–145                             |                |               |

| 9.2.11.3 | Reserved Operand Exception • 9-145               |                |               |

| 9.2.11.4 | UNPREDICTABLE Results • 9–145                    |                |               |

| 9.2.11.5 | Packed Decimal Operations • 9-145                |                |               |

| 9.2.11.6 | Zero-Length Decimal Strings • 9-146              |                |               |

| 9.2.11.7 | Instruction Descriptions • 9-146                 |                |               |

|          | ADDP                                             | 9–148          |               |

|          | ASHP                                             | 9–150          |               |

|          | CMPP                                             | 9–152          |               |

|          | CVTLP                                            | 9–153          |               |

|          | CVTPL                                            | 9–154          |               |

|          | CVTPS                                            | 9–155          |               |

|          | CVTPT                                            | 9–157          |               |

|          | CVTSP                                            | 9–159          |               |

|          | CVTTP                                            | 9–161          |               |

|          | DIVP                                             | 9–163          |               |

|          | MOVP                                             | 9–165          |               |

|          | MULP                                             | 9–166          |               |

|          | SUBP                                             | 9–167          |               |

| 9.2.12   | The EDITPC Instruction and Its Pattern Operators | 3-107          | 9–169         |

|          | EDITPC                                           | 9–170          | <b>5</b> -105 |

|          | EO\$ADJUST_INPUT                                 | 9–175          |               |

|          | EO\$BLANK_ZERO                                   | 9–175<br>9–176 |               |

|          | EO\$END                                          | 9–170<br>9–177 |               |

|          | EO\$END_FLOAT                                    |                |               |

|          | EO\$FILL                                         | 9–178<br>0–170 |               |

|          | EO\$FLOAT                                        | 9–179          |               |

|          |                                                  | 9–180          |               |

|          | EO\$INSERT                                       | 9–181          |               |

|          | EO\$LOAD_                                        | 9–182          |               |

|            | EO\$MOVE                                | 9–183       |       |

|------------|-----------------------------------------|-------------|-------|

|            | EO\$REPLACE_SIGN                        | 9–184       |       |

|            | EO\$_SIGNIF                             | 9–185       |       |

|            | EO\$STORE_SIGN                          | 9–186       |       |

| 9.2.13     | Other VAX Instructions                  | <b>***</b>  | 9–187 |

|            | PROBE <i>X</i>                          | 9–188       |       |

|            | CHM                                     | 9–190       |       |

|            | REI                                     | 9–192       |       |

|            | LDPCTX                                  | 9–193       |       |

|            | SVPCTX                                  | 9–194       |       |

|            | MTPR                                    | 9–195       |       |

|            | MFPR                                    | 9–196       |       |

|            | BUG                                     | 9–197       |       |

|            |                                         |             |       |

| CHAPTER 10 | VAX VECTOR ARCHITECTURE                 |             | 10–1  |

| 10.1       | INTRODUCTION TO VAX VECTOR ARCHITECTURE |             | 10–1  |

| 10.2       | VAX VECTOR ARCHITECTURE REGISTERS       |             | 10–1  |

| 10.2.1     | Vector Registers                        |             | 10–1  |

| 10.2.2     | Vector Control Registers                |             | 10–2  |

| 10.2.3     | Internal Processor Registers            |             | 10–3  |

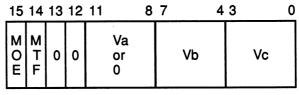

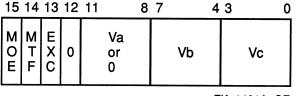

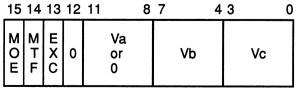

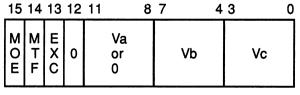

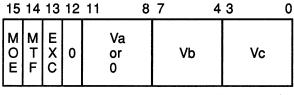

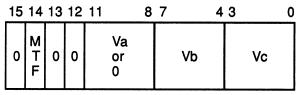

| 10.3       | VECTOR INSTRUCTION FORMATS              | <del></del> | 10–9  |

| 10.3.1     | Masked Operations                       |             | 10–12 |

| 10.3.2     | Exception Enable Bit                    |             | 10–12 |

| 10.3.3     | Modify Intent Bit                       |             | 10–12 |

| 10.3.4     | Register Specifier Fields               |             | 10–13 |

| 10.3.5     | Vector Control Word Formats             |             | 10–13 |

| 10.3.6     | Restrictions on Operand Specifier Usage |             | 10–16 |

| 10.3.7     | VAX Condition Codes                     |             | 10–17 |

| 10.3.8     | Illegal Vector Opcodes                  |             | 10–17 |

| 10.4       | ASSEMBLER NOTATION                      |             | 10–17 |

| 10.5       | EXECUTION MODEL                         |             | 10–18 |

| 10.5.1     | Access Mode Restrictions                |             | 10–20 |

| 10.5.2     | Scalar Context Switching                |             | 10–20 |

| 10.5.3     | Overlapped Instruction Execution        |             | 10–21 |

| 10.5.3.1   | Vector Chaining • 10-22                 |             |       |

| 10.5.3.2<br>10.5.3.3 |                                                                |                  |       |

|----------------------|----------------------------------------------------------------|------------------|-------|

| 10.6                 | VECTOR PROCESSOR EXCEPTIONS                                    |                  | 10–28 |

| 10.6.1               | Vector Memory Management Exception Handling                    |                  | 10–28 |

| 10.6.2               | Vector Arithmetic Exceptions                                   |                  | 10-30 |

| 10.6.3               | Vector Processor Disabled                                      | <u>-</u>         | 10-31 |

| 10.6.4               | Handling Disabled Faults and Vector Context Switching          |                  | 10–32 |

| 10.6.5               | MFVP Exception Reporting Examples                              |                  | 10–35 |

| 10.7                 | SYNCHRONIZATION                                                |                  | 10–37 |

| 10.7.1               | Scalar/Vector Instruction Synchronization (SYNC)               |                  | 10–37 |

| 10.7.2               | Scalar/Vector Memory Synchronization                           |                  | 10–38 |

| 10.7.2.1             | Memory Instruction Synchronization (MSYNC) • 10-39             |                  |       |

| 10.7.2.2             | Memory Activity Completion Synchronization (VMAC) • 10-40      | )                |       |

| 10.7.3               | Other Synchronization Between the Scalar and Vector Processors |                  | 10–41 |

| 10.7.4               | Memory Synchronization Within the Vector Processor (VSYNC)     |                  | 10–41 |

| 10.7.5               | Required Use of Memory Synchronization Instructions            |                  | 10-42 |

| 10.7.5.1             | When VSYNC Is Not Required • 10-44                             |                  |       |

| 10.8                 | MEMORY MANAGEMENT                                              |                  | 10–47 |

| 10.9                 | HARDWARE ERRORS                                                |                  | 10–47 |

| 10.10                | VECTOR MEMORY ACCESS INSTRUCTIONS                              |                  | 10–49 |

| 10.10.1              | Alignment Considerations                                       |                  | 10-49 |

| 10.10.2              | Stride Considerations                                          |                  | 10-49 |

| 10.10.3              | Context of Address Specifiers                                  |                  | 10-49 |

| 10.10.4              | Access Mode                                                    |                  | 10-49 |

| 10.10.5              | Memory Instructions                                            |                  | 10-49 |

|                      | VLD 10                                                         | <b>)–50</b>      |       |

|                      | VGATH 10                                                       | <b>)–52</b>      |       |

|                      | VST 10                                                         | <b>)</b> –54     |       |

|                      | VSCAT 10                                                       | <b>)–56</b>      |       |

| 10.11                | VECTOR INTEGER INSTRUCTIONS                                    |                  | 10–57 |

|                      | VADDL 10                                                       | <b>)–58</b>      |       |

|                      |                                                                | ) <del></del> 59 |       |

|                      | •                                                              | 61               |       |

|          | VSUBL                                      | 10–63 |       |

|----------|--------------------------------------------|-------|-------|

| 10.12    | VECTOR LOGICAL AND SHIFT INSTRUCTIONS      |       | 10–64 |

|          | VBIC, VBIS, AND VXOR                       | 10–65 |       |

|          | VSL                                        | 10–67 |       |

| 10.13    | VECTOR FLOATING-POINT INSTRUCTIONS         |       | 10–68 |

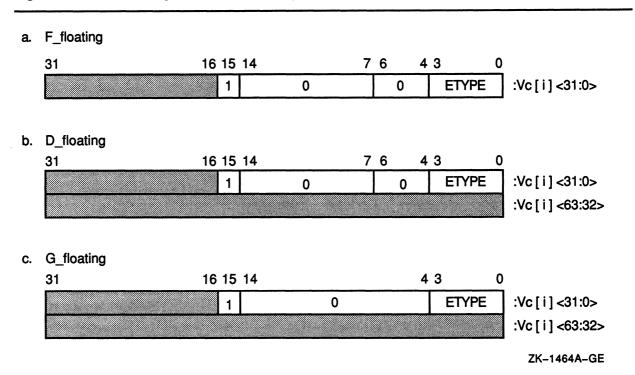

| 10.13.1  | Vector Floating-Point Exception Conditions |       | 10–68 |

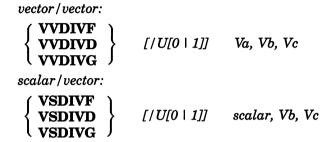

| 10.13.2  | Floating-Point Instructions                |       | 10–69 |

|          | VADD                                       | 10–70 |       |

|          | VCMP                                       | 10–72 |       |

|          | VVCVT                                      | 10–75 |       |

|          | VDIV                                       | 10–78 |       |

|          | VMUL                                       | 10–80 |       |

|          | VSUB                                       | 10–82 |       |

| 10.14    | VECTOR EDIT INSTRUCTIONS                   |       | 10–83 |

|          | VMERGE                                     | 10-84 |       |

|          | IOTA                                       | 10–86 |       |

| 10.15    | MISCELLANEOUS INSTRUCTIONS                 |       | 10–87 |

|          | MFVP                                       | 1088  |       |

|          | MTVP                                       | 10–90 |       |

|          | VSYNC                                      | 10–91 |       |

| ENDIX A  | ASCII CHARACTER SET                        |       | A-1   |

| PENDIX B | HEXADECIMAL/DECIMAL CONVERSION             |       | B-1   |

| B.1      | HEXADECIMAL TO DECIMAL                     |       | B-1   |

| B.2      | DECIMAL TO HEXADECIMAL                     |       | B-2   |

|          |                                            |       |       |

| APPENDIX C |        | VAX MACRO ASSEMBLER DIRECTIVES AND LANGUAGE SUMMARY    | C-1  |   |

|------------|--------|--------------------------------------------------------|------|---|

|            | C.1    | ASSEMBLER DIRECTIVES                                   | C-1  |   |

|            | C.2    | SPECIAL CHARACTERS                                     | C6   |   |

|            | C.3    | OPERATORS                                              | C-7  |   |

|            | C.3.1  | Unary Operators                                        | C-7  |   |

|            | C.3.2  | Binary Operators                                       | C-8  |   |

|            | C.3.3  | Macro String Operators                                 | C-8  |   |

|            | C.4    | ADDRESSING MODES                                       | C-10 |   |

| APPEN      | NDIX D | PERMANENT SYMBOL TABLE DEFINED FOR USE WITH VAX MACRO  | D-1  | ( |

| APPEN      | NDIX E | EXCEPTIONS THAT MAY OCCUR DURING INSTRUCTION EXECUTION | E-1  |   |

|            | E.1    | ARITHMETIC TRAPS AND FAULTS                            | E-1  |   |

|            | E.1.1  | Integer Overflow Trap                                  | E-2  |   |

|            | E.1.2  | Integer Divide-by-Zero Trap                            | E-2  | 4 |

|            | E.1.3  | Floating Overflow Trap                                 | E-2  |   |

|            | E.1.4  | Divide-by-Zero Trap                                    | E-2  |   |

|            | E.1.5  | Floating Underflow Trap                                | E-3  |   |

|            | E.1.6  | Decimal String Overflow Trap                           | E-3  |   |

|            | E.1.7  | Subscript-Range Trap                                   | E-3  |   |

|            | E.1.8  | Floating Overflow Fault                                | E-3  |   |

|            | E.1.9  | Divide-by-Zero Floating Fault                          | E-3  |   |

|            | E.1.10 | Floating Underflow Fault                               | E-4  |   |

|            | E.2    | MEMORY MANAGEMENT EXCEPTIONS                           | E-4  |   |

|            | E.2.1  | Access Control Violation Fault                         | E-4  |   |

|            | E.2.2  | Translation Not Valid Fault                            |      |   |

|       | E.3            | EXCEPTIONS DETECTED DURING OPERAND REFERENCE              | E-4        |

|-------|----------------|-----------------------------------------------------------|------------|

|       | E.3.1          | Reserved Addressing Mode Fault                            | E-4        |

|       | E.3.2          | Reserved Operand Exception                                | E-4        |

|       | E.4            | EXCEPTIONS OCCURRING AS THE CONSEQUENCE OF AN             |            |

|       |                | INSTRUCTION                                               | E-6        |

|       | E.4.1          | Reserved or Privileged Instruction Fault                  | E-6        |

|       | E.4.2          | Operand Reserved to Customers Fault                       | E-6        |

|       | E.4.3          | Instruction Emulation Exceptions                          | E-6        |

|       | E.4.4          | Compatibility Mode Exception                              | E-7        |

|       | E.4.5<br>E.4.6 | Change Mode Trap  Breakpoint Fault                        | E-8<br>E-8 |

|       | E.5            | TRACE FAULT                                               | E-8        |

|       | E.5.1          | Trace Operation When Entering a Change Mode Instruction   | E-9        |

|       | E.5.2          | Trace Operation Upon Return From Interrupt                | E9         |

|       | E.5.3          | Trace Operation After a BISPSW Instruction                | E-10       |

|       | E.5.4          | Trace Operation After a CALLS or CALLG Instruction        | E-10       |

|       | E.6            | SERIOUS SYSTEM FAILURES                                   | E-10       |

|       | E.6.1          | Kernel Stack Not Valid Abort                              | E-10       |

|       | E.6.2          | Interrupt Stack Not Valid Halt                            | E-10       |

|       | E.6.3          | Machine Check Exception                                   | E-11       |

| INDEX | (              |                                                           |            |

| FIGUF | RES            |                                                           |            |

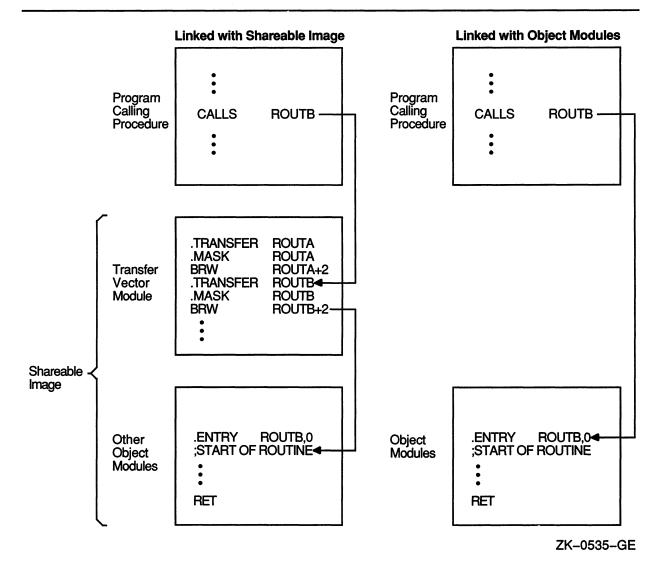

|       | 6–1            | Using Transfer Vectors                                    | 6–97       |

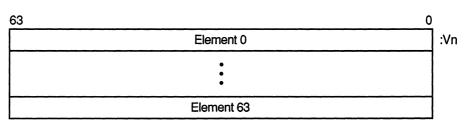

|       | 10–1           | Vector Register                                           | 10–2       |

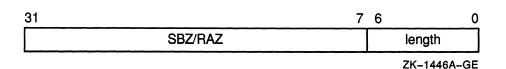

|       | 10–2           | Vector Length Register (VLR)                              | 10–3       |

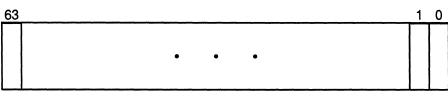

|       | 10–3           | Vector Mask Register (VMR)                                | 10-3       |

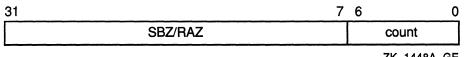

|       | 10-4           | Vector Count Register (VCR)                               | 10–3       |

|       | 10–5           | Vector Processor Status Register (VPSR)                   | 10–4       |

|       | 10–6           | Vector Arithmetic Exception Register (VAER)               | 10–6       |

|       | 10–7           | Vector Memory Activity Check (VMAC) Register              | 10–7       |

|       | 10-7           | Vector Translation Buffer Invalidate All (VTBIA) Register | 10-7       |

|       |                | , , ,                                                     | 10-7       |

|       | 10–9           | Vector State Address Register (VSAR)                      |            |

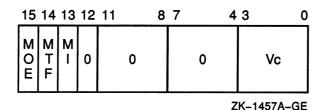

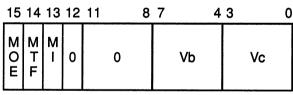

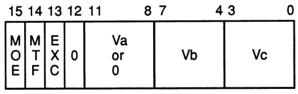

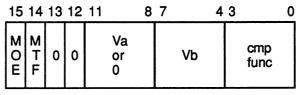

|       | 10–10          | Vector Control Word Operand (cntrl)                       | 10–10      |

|       | 10–11          | Vector Control Word Format                                | 10–15      |

|       |                |                                                           | xix        |

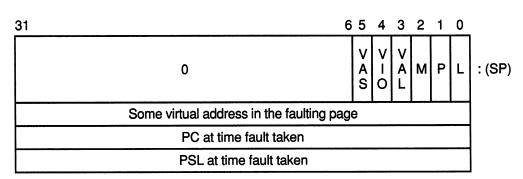

|     | 10–12 | Memory Management Fault Stack Frame (as Sent by the Vector Processor)      | 10–29 |   |

|-----|-------|----------------------------------------------------------------------------|-------|---|

|     | 10–13 | Encoding of the Reserved Operand                                           | 10–69 |   |

|     | E-1   | Compatibility Mode Exception Stack Frame                                   | E-7   |   |

| TAB | LES   |                                                                            |       |   |

|     | 3–1   | Special Characters Used in VAX MACRO Statements                            | 3–1   |   |

|     | 3–2   | Separating Characters in VAX MACRO Statements                              | 3–2   |   |

|     | 3–3   | Unary Operators                                                            | 3–11  |   |

|     | 3–4   | Binary Operators                                                           | 3–15  |   |

|     | 5–1   | Addressing Modes                                                           | 5–2   |   |

|     | 5–2   | Floating-Point Literals Expressed as Decimal Numbers                       | 5–11  |   |

|     | 5–3   | Floating-Point Literals Expressed as Rational Numbers                      | 511   |   |

|     | 5-4   | Index Mode Addressing                                                      | 5–18  |   |

|     | 6–1   | Summary of General Assembler Directives                                    | 6–1   |   |

|     | 6–2   | Summary of Macro Directives                                                | 6–3   |   |

|     | 6–3   | .ENABLE and .DISABLE Symbolic Arguments                                    | 6–22  |   |

|     | 6–4   | Condition Tests for Conditional Assembly Directives                        | 6-41  | - |

|     | 6–5   | Operand Descriptors                                                        | 6–72  |   |

|     | 66    | Program Section Attributes                                                 | 6–78  |   |

|     | 6–7   | Default Program Section Attributes                                         | 6–79  |   |

|     | 6-8   | .SHOW and .NOSHOW Symbolic Arguments                                       | 6–89  |   |

|     | 8–1   | Representation of Least-Significant Digit and Sign in Zoned Numeric Format | 8–9   |   |

|     | 8–2   | Representation of Least-Significant Digit and Sign in Overpunch Format     | 8–10  | ( |

|     | 8–3   | Floating-Point Literals Expressed as Decimal Numbers                       | 8–25  |   |

|     | 8-4   | Floating-Point Literals Expressed as Rational Numbers                      | 8–25  |   |

|     | 8–5   | General Register Addressing                                                | 8–28  |   |

|     | 8–6   | Program Counter Addressing                                                 | 8–29  |   |

|     | 9–1   | Summary of EDITPC Pattern Operators                                        | 9–172 |   |

|     | 9–2   | EDITPC Pattern Operator Encoding                                           | 9–173 |   |

|     | 10–1  | Description of the Vector Processor Status Register (VPSR)                 | 10–4  |   |

|     | 10–2  | Possible VPSR<3:0> Settings for MTPR                                       | 10–5  |   |

|     | 10–3  | State of the Vector Processor                                              | 10–6  |   |

|     | 10–4  | VAER Exception Condition Summary Word Encoding                             | 10-7  |   |

|     | 10–5  | IPR Assignments                                                            | 10–9  | ĺ |

|     | 10–6  | Description of the Vector Control Word Operand                             | 10–11 | 1 |

|     | 10–7  | Dependences for Vector Operate Instructions                                | 10–25 |   |

| 10–8  | Dependences for Vector Load and Gather Instructions                                                                                                                             | 10–25             |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 10-9  | Dependences for Vector Store and Scatter Instructions                                                                                                                           | 10–26             |

| 10–10 | Dependences for Vector Compare Instructions                                                                                                                                     | 10–26             |

| 10–11 | Dependences for Vector MERGE Instructions                                                                                                                                       | 10–27             |

| 10–12 | Dependences for IOTA Instruction                                                                                                                                                | 10–27             |

| 10–13 | Dependences for MFVP Instructions                                                                                                                                               | 10–27             |

| 10–14 | Miscellaneous Dependences                                                                                                                                                       | 10–28             |

| 10–15 | Possible Pairs of Read and Write Operations When Scalar/Vector Memory Synchronization (M) or VSYNC (V) Is Required Between Instructions That Reference the Same Memory Location | 10 <del>-44</del> |

| 10–16 | Encoding of the Exception Condition Type (ETYPE)                                                                                                                                | 10–69             |

| C-1   | Assembler Directives                                                                                                                                                            | C-1               |

| C-2   | Special Characters Used in VAX MACRO Statements                                                                                                                                 | C-6               |

| C-3   | Summary of Unary Operators                                                                                                                                                      | C-7               |

| C-4   | Summary of Binary Operators                                                                                                                                                     | C-8               |

| C-5   | Macro String Operators                                                                                                                                                          | C-9               |

| C-6   | Summary of Addressing Modes                                                                                                                                                     | C-10              |

| D-1   | Opcodes (Alphabetic Order) and Functions                                                                                                                                        | D-1               |

| D-2   | One_Byte Opcodes (Numeric Order)                                                                                                                                                | D-12              |

| D-3   | Two_Byte Opcodes (Numeric Order)                                                                                                                                                | D-16              |

| E-1   | Arithmetic Exception Type Codes                                                                                                                                                 | E-1               |

| E-2   | Compatibility Mode Exception Type Codes                                                                                                                                         | E-7               |

| O |

|---|

#### **Preface**

This manual describes the VAX MACRO language and the VAX instruction set. It includes the format and function of each feature of the language. The VAX Architecture Reference Manual describes the instruction set in greater detail.

#### **Intended Audience**

This manual is intended for all programmers writing VAX MACRO programs. You should be familiar with assembly language programming, the VAX instruction set, and the VMS operating system before reading this manual.

#### **Document Structure**

This manual is divided into two parts, each of which is subdivided into several chapters.

Part I describes the VAX MACRO language.

- Chapter 1 introduces the features of the VAX MACRO language.

- Chapter 2 describes the format used in VAX MACRO source statements.

- Chapter 3 describes the following components of VAX MACRO source statements:

- Character set

- Numbers

- Symbols

- Local labels

- Terms and expressions

- Unary and binary operators

- Direct assignment statements

- Current location counter

- Chapter 4 describes the arguments and string operators used with macros.

- Chapter 5 summarizes and gives examples of using the VAX MACRO addressing modes.

- Chapter 6 describes the VAX MACRO general assembler directives and the directives used in defining and expanding macros.

Part II describes the VAX data types, the instruction and addressing mode formats, and the instruction set.

- Chapter 7 summarizes the terminology and conventions used in the descriptions in Part II.

- Chapter 8 describes the basic VAX architecture, including the following:

- Address space

- Data types

- Processor status longword

- Permanent exception enables

- Instruction and addressing mode formats

- Chapter 9 describes the native-mode instruction set. The instructions are divided into groups according to their function and are listed alphabetically within each group.

- Chapter 10 describes the extension to the VAX architecture for integrated vector processing.

This manual also contains the following five appendixes:

- Appendix A lists the ASCII character set used in VAX MACRO programs.

- Appendix B gives rules for hexadecimal/decimal conversion.

- Appendix C summarizes the general assembler and macro directives (in alphabetical order), special characters, unary operators, binary operators, macro string operators, and addressing modes.

- Appendix D lists the permanent symbols (instruction set) defined for use with VAX MACRO.

- Appendix E describes the exceptions (traps and faults) that may occur during instruction execution.

#### **Associated Documents**

The following documents are relevant to VAX MACRO programming:

- VAX Architecture Reference Manual

- VMS DCL Dictionary

- The descriptions of the VMS Linker and Symbolic Debugger in:

- VMS Linker Utility Manual

- VMS Debugger Manual

- Introduction to VMS System Routines

- VMS Run-Time Library Routines Volume

#### **Conventions**

The following conventions are used in this manual:

Ctrl/x

A sequence such as Ctrl/x indicates that you must hold down the key labeled Ctrl while you press another key or a pointing device button.

Return

In examples, a key name is shown enclosed in a box to indicate that you press a key on the keyboard. (In text, a key name is not enclosed in a box.)

In examples, a horizontal ellipsis indicates one of the following possibilities:

- Additional optional arguments in a statement have been omitted.

- The preceding item or items can be repeated one or more times.

- Additional parameters, values, or other information can be entered.

A vertical ellipsis indicates the omission of items from a code example or command format; the items are omitted because they are not important to the topic being discussed.

[]

In format descriptions, brackets indicate that whatever is enclosed within the brackets is optional; you can select none, one, or all of the choices. (Brackets are not, however, optional in the syntax of a directory name in a file specification or in the syntax of a substring specification in an assignment statement.)

{}

In format descriptions, braces surround a required choice of options; you must choose one of the options

listed.

boldface text

Boldface text represents the introduction of a new term or the name of an argument, an attribute, or a

Boldface text is also used to show user input in online versions of the book.

**UPPERCASE TEXT**

Uppercase letters indicate that you must enter a command (for example, enter OPEN/READ), or they indicate the name of a routine, the name of a file, the name of a file protection code, or the abbreviation for

a system privilege.

Hyphens in coding examples indicate that additional arguments to the request are provided on the line that

follows.

numbers

Unless otherwise noted, all numbers in the text are assumed to be decimal. Nondecimal radixes—binary, octal, or hexadecimal—are explicitly indicated.

| · Cosi |

|--------|

|        |

|        |

# **VAX MACRO Language**

Part I provides an overview of the features of the VAX MACRO language. It includes an introduction to the structure and components of VAX MACRO source statements. Part I also contains a detailed discussion of the VAX MACRO addressing modes, general assembler directives, and macro directives.

# 1 Introduction

VAX MACRO is an assembly language for programming VAX computers using the VMS operating system. Source programs written in VAX MACRO are translated into object (or binary) code by the VAX MACRO assembler, which produces an object module and, optionally, a listing file. The features of the language are introduced in this chapter.

VAX MACRO source programs consist of a sequence of source statements. These source statements may be any of the following:

- VAX native-mode instructions

- Direct assignment statements

- Assembler directives

Instructions manipulate data. They perform such functions as addition, data conversion, and transfer of control. Instructions are usually followed in the source statement by operands, which can be any kind of data needed for the operation of the instruction. The VAX instruction set is summarized in Appendix D of this volume and is described in detail in Chapter 9. Direct assignment statements equate symbols to values. Assembler directives guide the assembly process and provide tools for using the instructions. There are two classes of assembler directives: general assembler directives and macro directives.

General assembler directives can be used to perform the following operations:

- Store data or reserve memory for data storage

- Control the alignment of parts of the program in memory

- Specify the methods of accessing the sections of memory in which the program will be stored

- Specify the entry point of the program or a part of the program

- Specify the way in which symbols will be referenced

- Specify that a part of the program is to be assembled only under certain conditions

- Control the format and content of the listing file

- Display informational messages

- Control the assembler options that are used to interpret the source program

- Define new opcodes

# Introduction

Macro directives are used to define macros and repeat blocks. They allow you to perform the following operations:

- Repeat identical or similar sequences of source statements throughout a program without rewriting those sequences

- Use string operators to manipulate and test the contents of source statements

Use of macros and repeat blocks helps minimize programmer errors and speeds the debugging process.

# YAX MACRO Source Statement Format

A source program consists of a sequence of source statements that the assembler interprets and processes, one at a time, generating object code or performing a specific assembly-time process. A source statement can occupy one source line or can extend onto several source lines. Each source line can be up to 132 characters long; however, to ensure that the source line fits (with its binary expansion) on one line in the listing file, no line should exceed 80 characters.

VAX MACRO statements can consist of up to four fields, as follows:

- Label field—symbolically defines a location in a program.

- Operator field—specifies the action to be performed by the statement; can be an instruction, an assembler directive, or a macro call.

- Operand field—contains the instruction operands or the assembler directive arguments or the macro arguments.

- Comment field—contains a comment that explains the meaning of the statement; does not affect program execution.

The label field and the comment field are optional. The label field ends with a colon (:) and the comment field begins with a semicolon (;). The operand field must conform to the format of the instruction, directive, or macro specified in the operator field.

Although statement fields can be separated by either a space or a tab (see Table 3–2), formatting statements with the tab character is recommended for consistency and clarity and is a Digital convention.

| Field    | Begins in Column | Tab Characters to Reach Column |

|----------|------------------|--------------------------------|

| Label    | 1                | 0                              |

| Operator | 9                | 1                              |

| Operand  | 17               | 2                              |

| Comment  | 41               | 5                              |

#### For example:

```

.TITLE ROUT1

.ENTRY START, ^M<> ; Beginning of routine

CLRL RO ; Clear register

LABT: SUBL3 #10,4(AP),R2 ; Subtract 10

LAB2: BRB CONT ; Branch to another routine

```

Continue a single statement on several lines by using a hyphen (-) as the last nonblank character before the comment field, or at the end of line (when there is no comment). For example:

LAB1: MOVAL W^BOO\$AL\_VECTOR,- ; Save boot driver RPB\$L IOVEC(R7)

#### **VAX MACRO Source Statement Format**

VAX MACRO treats the preceding statement as equivalent to the following statement:

```

LAB1: MOVAL W^BOO$AL VECTOR, RPB$L IOVEC(R7) ; Save boot driver

```

A statement can be continued at any point. Do not continue permanent and user-defined symbol names on two lines. If a symbol name is continued and the first character on the second line is a tab or a blank, the symbol name is terminated at that character. Section 3.3 describes symbols in detail.

Note that when a statement occurs in a macro definition (see Chapter 4 and Chapter 6), the statement cannot contain more than 1000 characters.

Blank lines are legal, but they have no significance in the source program except that they terminate a continued line.

The following sections describe each of the statement fields in detail.

#### 2.1 Label Field

A label is a user-defined symbol that identifies a location in the program. The symbol is assigned a value equal to the location counter where the label occurs. The user-defined symbol name can be up to 31 characters long and can contain any alphanumeric character and the underscore (\_), dollar sign (\$), and period (.) characters. See Section 3.3.2 for a description of the rules for forming user-defined symbol names in more detail.

If a statement contains a label, the label must be in the first field on the line.

A label is terminated by a colon (:) or a double colon (::). A single colon indicates that the label is defined only for the current module (an internal symbol). A double colon indicates that the label is globally defined; that is, the label can be referenced by other object modules.

Once a label is defined, it cannot be redefined during the source program. If a label is defined more than once, VAX MACRO displays an error message when the label is defined and again when it is referenced.

If a label extends past column 7, place it on a line by itself so that the following operator field can start in column 9 of the next line.

The following example illustrates some of the ways you can define labels:

```

EXP:

50

.BLKL

; Table stores expected values

DATA::

.BLKW

25

; Data table accessed by store

routine in another module

EVAL:

CLRL

RΩ

; Routine evaluates expressions

ERROR IN ARG:

; The arg-list contains an error

INCL

R0

increment error count

TEST::

MOVO

EXP,R1

; This tests routine

referenced externally

TEST1:

BRW

EXIT

; Go to exit routine

```

The label field is also used for the symbol in a direct assignment statement (see Section 3.8).

## 2.2 Operator Field

The operator field specifies the action to be performed by the statement. This field can contain an instruction, an assembler directive, or a macro call

When the operator is an instruction, VAX MACRO generates the binary code for that instruction in the object module. The binary codes are listed in Appendix D; the instruction set is described in Chapter 9. When the operator is a directive, VAX MACRO performs certain control actions or processing operations during source program assembly. The assembler directives are described in Chapter 6. When the operator is a macro call, VAX MACRO expands the macro. Macro calls are described in Chapter 4 and in Chapter 6 (.MACRO directive).

Use either a space or a tab character to terminate the operator field; however, the tab is the recommended termination character.

# 2.3 Operand Field

The operand field can contain operands for instructions or arguments for either assembler directives or macro calls.

Operands for instructions identify the memory locations or the registers that are used by the machine operation. These operands specify the addressing mode for the instruction, as described in Chapter 5. The operand field for a specific instruction must contain the number of operands required by that instruction. See Chapter 9 for descriptions of the instructions and their operands.

Arguments for a directive must meet the format requirements of that directive. Chapter 6 describes the directives and the format of their arguments.

Operands for a macro must meet the requirements specified in the macro definition. See the description of the .MACRO directive in Chapter 6.

If two or more operands are specified, they must be separated by commas (,). VAX MACRO also allows a space or tab to be used as a separator for arguments to any directive that does not accept expressions (see Section 3.5 for a discussion of expressions). However, a comma is required to separate operands for instructions and for directives that accept expressions as arguments.

The semicolon that starts the comment field terminates the operand field. If a line does not have a comment field, the operand field is terminated by the end of the line.

## 2.4 Comment Field

The comment field contains text that explains the function of the statement. Every line of code should have a comment. Comments do not affect assembly processing or program execution. You can cause user-written messages to be displayed during assembly by the .ERROR, .PRINT, and .WARN directives (see descriptions in Chapter 6).

#### **VAX MACRO Source Statement Format**

#### 2.4 Comment Field

The comment field must be preceded by a semicolon; it is terminated by the end of the line. The comment field can contain any printable ASCII character (see Appendix A).

To continue a lengthy comment to the next line, write the comment on the next line and precede it with another semicolon. If a comment does not fit on one line, it can be continued on the next, but the continuation must be preceded by another semicolon. A comment can appear on a line by itself.

Write the text of a comment to convey the meaning rather than the action of the statement. The instruction MOVAL BUF\_PTR\_1,R7, for example, should have a comment such as "Get pointer to first buffer," not "Move address of BUF\_PTR\_1 to R7."

#### For example:

```

MOVAL STRING_DES_1,R0 ; Get address of string ; descriptor

MOVZWL (R0),R1 ; Get length of string MOVL 4(R0),R0 ; Get address of string

```

# 3 Components of MACRO Source Statements

This chapter describes the following components of VAX MACRO source statements:

- Character set

- Numbers

- Symbols

- Local labels

- Terms and expressions

- Unary and binary operators

- Direct assignment statements

- Current location counter

### 3.1 Character Set

The following characters can be used in VAX MACRO source statements:

- The letters of the alphabet, A to Z, uppercase and lowercase. Note that the assembler considers lowercase letters equivalent to uppercase letters except when they appear in ASCII strings.

- The digits 0 to 9.

- The special characters listed in Table 3–1.

Table 3–1 Special Characters Used in VAX MACRO Statements

| Character | Character Name | Function                                                               |

|-----------|----------------|------------------------------------------------------------------------|

| _         | Underscore     | Character in symbol names                                              |

| \$        | Dollar sign    | Character in symbol names                                              |

| •         | Period         | Character in symbol names, current location counter, and decimal point |

| :         | Colon          | Label terminator                                                       |

| =         | Equal sign     | Direct assignment operator and macro keyword argument terminator       |

|           | Tab            | Field terminator                                                       |

|           | Space          | Field terminator                                                       |

| #         | Number sign    | Immediate addressing mode indicator                                    |

(continued on next page)

# **Components of MACRO Source Statements**

#### 3.1 Character Set

Table 3-1 (Cont.) Special Characters Used in VAX MACRO Statements

| Character | Character Name          | Function                                                                                                                        |

|-----------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| @         | At sign                 | Deferred addressing mode indicator and arithmetic shift operator                                                                |

| ,         | Comma                   | Field, operand, and item separator                                                                                              |

| ;         | Semicolon               | Comment field indicator                                                                                                         |

| +         | Plus sign               | Autoincrement addressing mode indicator, unary plus operator, and arithmetic addition operator                                  |

| _         | Minus sign or<br>hyphen | Autodecrement addressing mode indicator, unary minus operator, arithmetic subtraction operator, and line continuation indicator |

| *         | Asterisk                | Arithmetic multiplication operator                                                                                              |

| 1         | Slash                   | Arithmetic division operator                                                                                                    |

| &         | Ampersand               | Logical AND operator                                                                                                            |

| !         | Exclamation point       | Logical inclusive OR operator point                                                                                             |

| 1         | Backslash               | Logical exclusive OR and numeric conversion indicator in macro arguments                                                        |

| ٨         | Circumflex              | Unary operators and macro argument delimiter                                                                                    |

| []        | Square brackets         | Index addressing mode and repeat count indicators                                                                               |

| ()        | Parentheses             | Register deferred addressing mode indicators                                                                                    |

| <>        | Angle brackets          | Argument or expression grouping delimiters                                                                                      |

| ?         | Question mark           | Created local label indicator in macro arguments                                                                                |

| ,         | Apostrophe              | Macro argument concatenation indicator                                                                                          |

| %         | Percent sign            | Macro string operators                                                                                                          |

Table 3-2 defines the separating characters used in VAX MACRO.

Table 3–2 Separating Characters in VAX MACRO Statements

| Character        | Character Name | Usage                                                                                                                                       |

|------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| (space)<br>(tab) | Space or tab   | Separator between statement fields. Spaces within expressions are ignored.                                                                  |

|                  | Comma          | Separator between symbolic arguments within<br>the operand field. Multiple expressions in the<br>operand field must be separated by commas. |

# 3.2 Numbers

Numbers can be integers, floating-point numbers, or packed decimal strings.

# Components of MACRO Source Statements 3.2 Numbers

## 3.2.1 Integers

Integers can be used in any expression including expressions in operands and in direct assignment statements (Section 3.5 describes expressions).

#### **Format**

snn

S

An optional sign: plus sign (+) for positive numbers (the default) or minus sign (-) for negative numbers.

#### nn

A string of numeric characters that is legal for the current radix.

VAX MACRO interprets all integers in the source program as decimal unless the number is preceded by a radix control operator (see Section 3.6.1).

Integers must be in the range of -2,147,483,648 to +2,147,483,647 for signed data or in the range of 0 to 4,294,967,295 for unsigned data.

Negative numbers must be preceded by a minus sign; VAX MACRO translates such numbers into two's complement form. In positive numbers, the plus sign is optional.

# 3.2.2 Floating-Point Numbers

A floating-point number can be used in the .F\_FLOATING (.FLOAT),.D\_FLOATING (.DOUBLE), .G\_FLOATING, and .H\_FLOATING directives (described in Chapter 6) or as an operand in a floating-point instruction. A floating-point number cannot be used in an expression or with a unary or binary operator except the unary plus, unary minus, and unary floating-point operator, ^F (F\_FLOATING). Section 3.6 and Section 3.7 describe unary and binary operators.

A floating-point number can be specified with or without an exponent.

### **Formats**

Floating-point number without exponent:

snn snn.nn snn.

Floating-point number with exponent:

snnEsnn snn.nnEsnn snn.Esnn

# **Components of MACRO Source Statements**

### 3.2 Numbers

S

An optional sign.

#### nn

A string of decimal digits in the range of 0 to 9.

The decimal point can appear anywhere to the right of the first digit. Note that a floating-point number cannot start with a decimal point because VAX MACRO will treat the number as a user-defined symbol (see Section 3.3.2).

Floating-point numbers can be single-precision (32-bit), double-precision (64-bit), or extended-precision (128-bit) quantities. The degree of precision is 7 digits for single-precision numbers, 16 digits for double-precision numbers, and 33 digits for extended-precision numbers.

The magnitude of a nonzero floating-point number cannot be smaller than approximately 0.29E-38 or greater than approximately 1.7E38.

Single-precision floating-point numbers can be rounded (by default) or truncated. The .ENABLE and .DISABLE directives (described in Chapter 6) control whether single-precision floating-point numbers are rounded or truncated. Double-precision and extended-precision floating-point numbers are always rounded.

Section 8.2.6, Section 8.2.7, Section 8.2.8, and Section 8.2.9 describe the internal format of floating-point numbers.

# 3.2.3 Packed Decimal Strings

A packed decimal string can be used only in the .PACKED directive (described in Chapter 6).

#### **Format**

snn

S

An optional sign.

#### nn

A string containing up to 31 decimal digits in the range of 0 to 9.

A packed decimal string cannot have a decimal point or an exponent.

Section 8.2.14 describes the internal format of packed decimal strings.

# 3.3 Symbols

Three types of symbols can be used in VAX MACRO source programs: permanent symbols, user-defined symbols, and macro names.

# Components of MACRO Source Statements 3.3 Symbols

# 3.3.1 Permanent Symbols

Permanent symbols consist of instruction mnemonics (see Appendix D), VAX MACRO directives (see Chapter 6), and register names. You need not define instruction mnemonics and directives before you use them in the operator field of a VAX MACRO source statement. Also, you need not define register names before using them in the addressing modes (see Chapter 5).

Register names cannot be redefined; that is, a symbol that you define cannot be one of the register names contained in the following list. You can express the 16 general registers of the VAX processor in a source program only as follows:

| Register     |                                                                                                                                                                                |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name         | Processor Register                                                                                                                                                             |

| R0           | General register 0                                                                                                                                                             |

| R1           | General register 1                                                                                                                                                             |

| R2           | General register 2                                                                                                                                                             |

|              | •                                                                                                                                                                              |

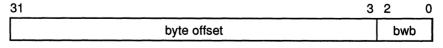

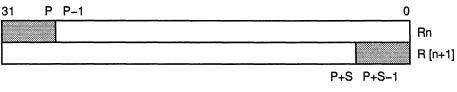

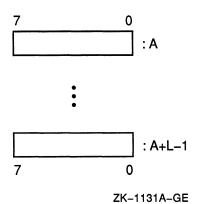

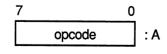

| •            |                                                                                                                                                                                |