# Reference Manual **CONTROL DATA 8528** DIGITAL COMMUNICATIONS TERMINAL

# Reference Manual **CONTROL DATA 8528** DIGITAL COMMUNICATIONS TERMINAL

Publication No. 60041001 January 1964

© 1964, Control Data Corporation Printed in the United States of America Address comments concerning this manual to:

Control Data Corporation Technical Publications Department 501 Park Avenue Minneapolis 15, Minnesota

|           |                    | RECORD          | OF CH    | ANGE NOTICES                          |

|-----------|--------------------|-----------------|----------|---------------------------------------|

| C. N. NO. | DATE<br>ORIGINATED | DATE<br>ENTERED | INITIALS | REMARKS                               |

|           | 10 C               |                 |          |                                       |

|           |                    |                 |          |                                       |

|           |                    |                 |          |                                       |

|           |                    |                 |          |                                       |

|           |                    |                 |          | 2                                     |

|           |                    |                 |          |                                       |

|           |                    |                 |          |                                       |

|           |                    |                 |          |                                       |

|           |                    |                 |          |                                       |

|           |                    |                 |          |                                       |

|           |                    |                 |          |                                       |

|           |                    |                 |          |                                       |

|           |                    |                 |          |                                       |

|           |                    |                 |          |                                       |

|           |                    | 1               |          | · · · · · · · · · · · · · · · · · · · |

|           |                    |                 |          |                                       |

|           |                    |                 |          |                                       |

|           |                    |                 |          |                                       |

|           |                    |                 |          |                                       |

|           |                    |                 |          |                                       |

|           |                    |                 |          |                                       |

|           |                    |                 |          |                                       |

|           |                    |                 |          |                                       |

|           |                    |                 |          |                                       |

|           |                    |                 |          |                                       |

|           |                    |                 |          |                                       |

|           |                    |                 |          |                                       |

| 1         |                    |                 |          |                                       |

|           |                    |                 |          |                                       |

|           | э.                 |                 |          |                                       |

|           |                    |                 |          | ¥                                     |

# CONTENTS

| Chapter 1 - Description                                     |     |

|-------------------------------------------------------------|-----|

| Physical Description                                        | 1-1 |

| Cabinet                                                     | 1-1 |

| Control Head                                                | 1-3 |

| Principles of Operation                                     | 1-3 |

| Control Signals                                             | 1-3 |

| Function Codes                                              | 1-4 |

| 8528 Characteristics                                        | 1-7 |

| Standard                                                    | 1-7 |

| Options                                                     | 1-8 |

| Chapter 2 - Operation                                       |     |

| Main Cabinet Controls and Indicators                        | 2-1 |

| External                                                    | 2-1 |

| Internal                                                    | 2-1 |

| Control Head Indicators and Switches                        | 2-4 |

| Chapter 3 - Programming                                     |     |

| Example A (Two Computer Private System)                     | 3-1 |

| Example B (Multi-Computer<br>Network)                       | 3-4 |

| Programming Aids                                            | 3-7 |

| Effects of Fake Ready or WBB                                | 3-7 |

| Fake Ready When No Data is<br>Being Received                | 3-7 |

| Line Selection                                              | 3-7 |

| Interrupt on Error or Fake Ready                            | 3-7 |

| Status and Sense                                            | 3-7 |

| Receive and Interrupt Selection<br>With Timed Wait for Data | 3-8 |

| Disconnect (160/160-A Only)                                 | 3-8 |

| Restrictions                                                | 3-8 |

| Chapter 4 - Principles of Operat     | ion    |

|--------------------------------------|--------|

| Timing                               | 4-1    |

| Transmit                             | 4-1    |

| Receive                              | 4-3    |

| Circuits                             | 4-6    |

| Function Control Circuits            | 4-6    |

| 1604/1604-A Sense Codes              | 4-8    |

| 160/160-A Status Request             | 4-9    |

| Interrupt                            | 4-10   |

| Output Resume                        | 4-11   |

| Input Ready/Resume<br>(1604/1604-A)  | 4-12   |

| Input Request/Ready (160/160-A)      | ) 4-12 |

| Fake Ready Time Delay                | 4-14   |

| Main Timing                          | 4-15   |

| Transmit Pyramid and Mixer FF        | 4-15   |

| Bit and Timing Detector              | 4-17.  |

| Error Detector                       | 4-19   |

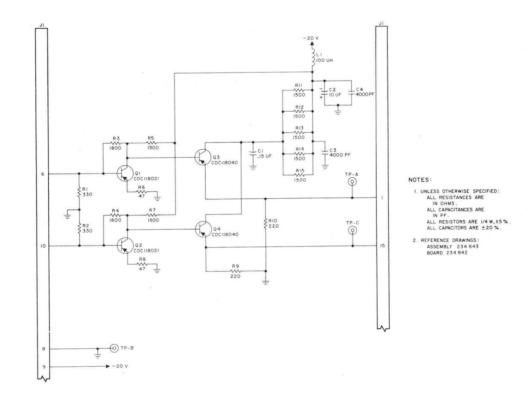

| Audio Communication                  | 4-20   |

| Chapter 5 - Installation and Mainter | nance  |

| Installation                         | 5-1    |

| Maintenance                          | 5-1    |

| Simulator                            | 5-3    |

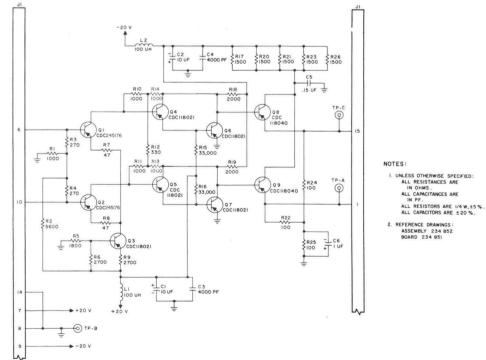

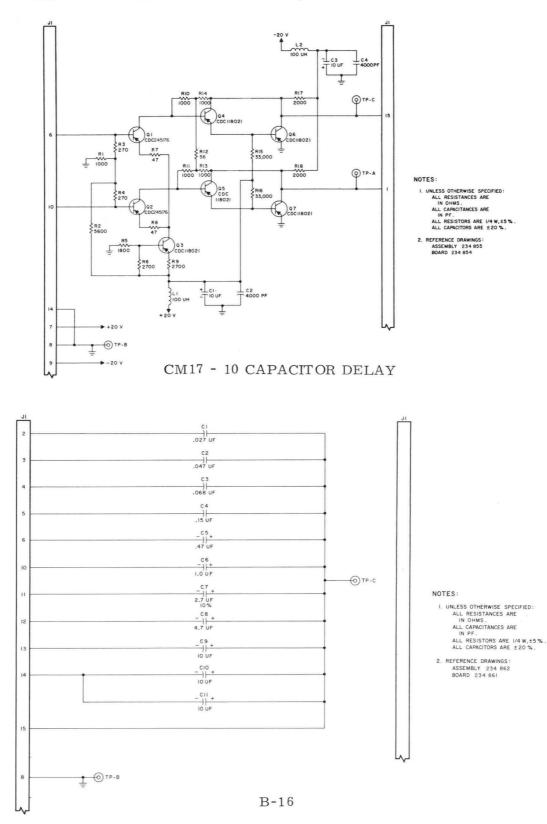

| Delays                               | 5-3    |

| Serial Communication Channels        | 5-6    |

| Appendix A                           |        |

| Cabling                              | A-1    |

| Appendix B                           |        |

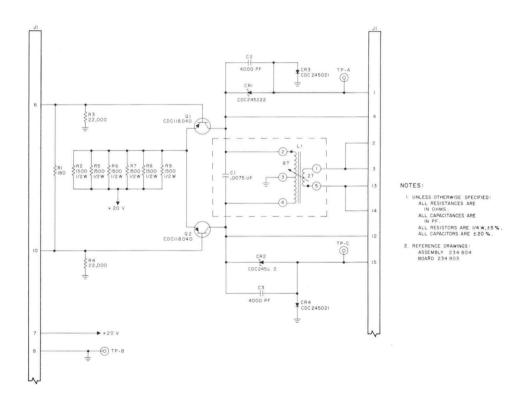

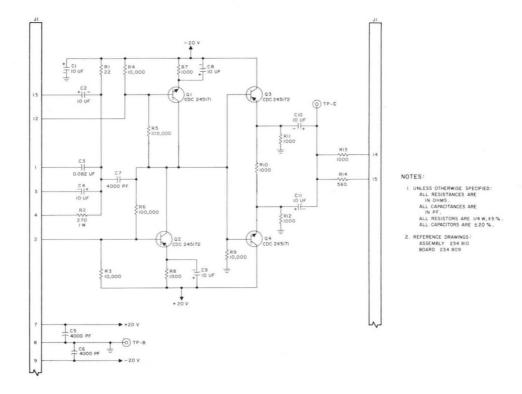

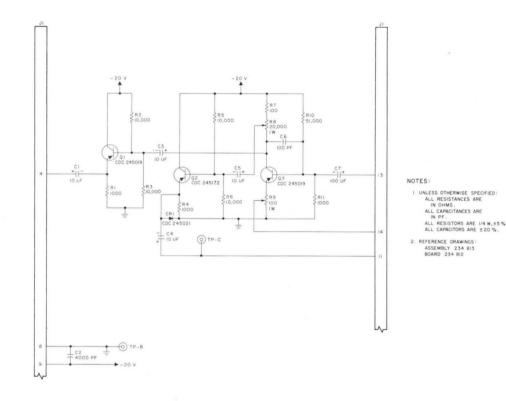

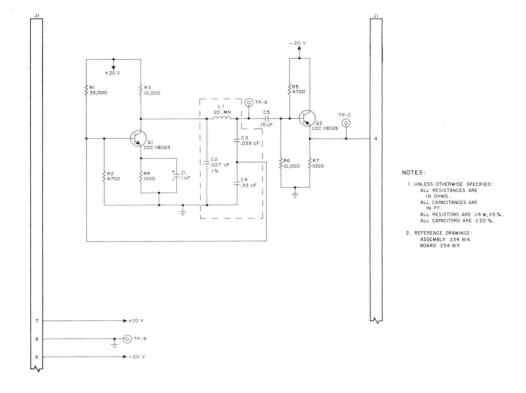

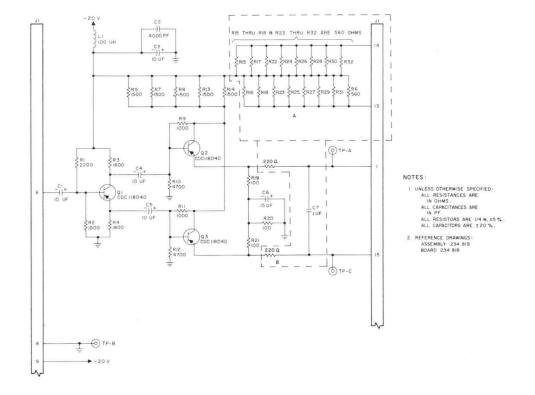

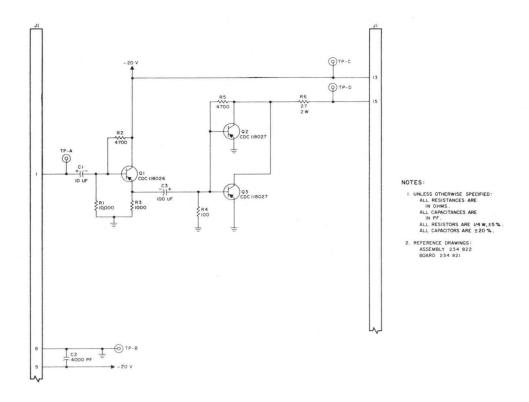

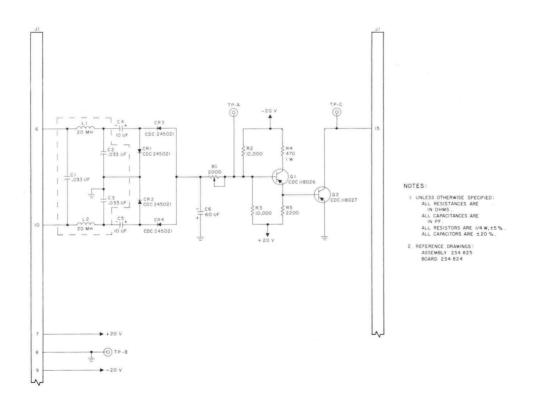

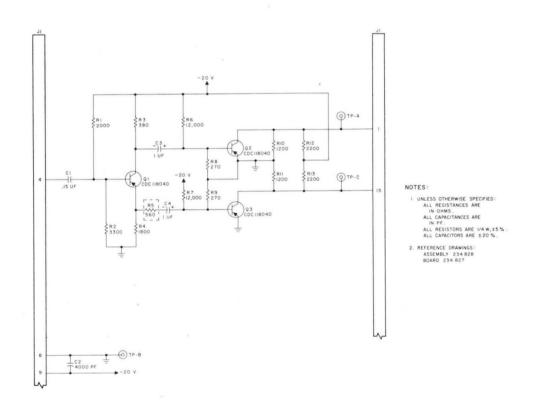

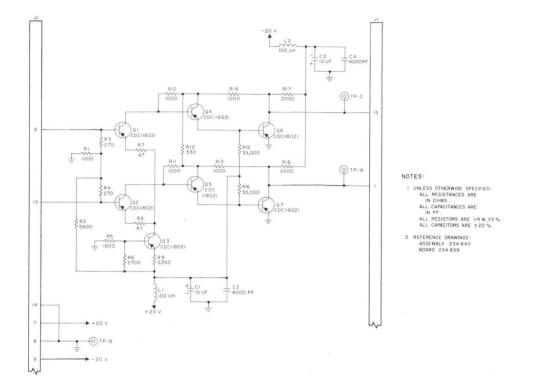

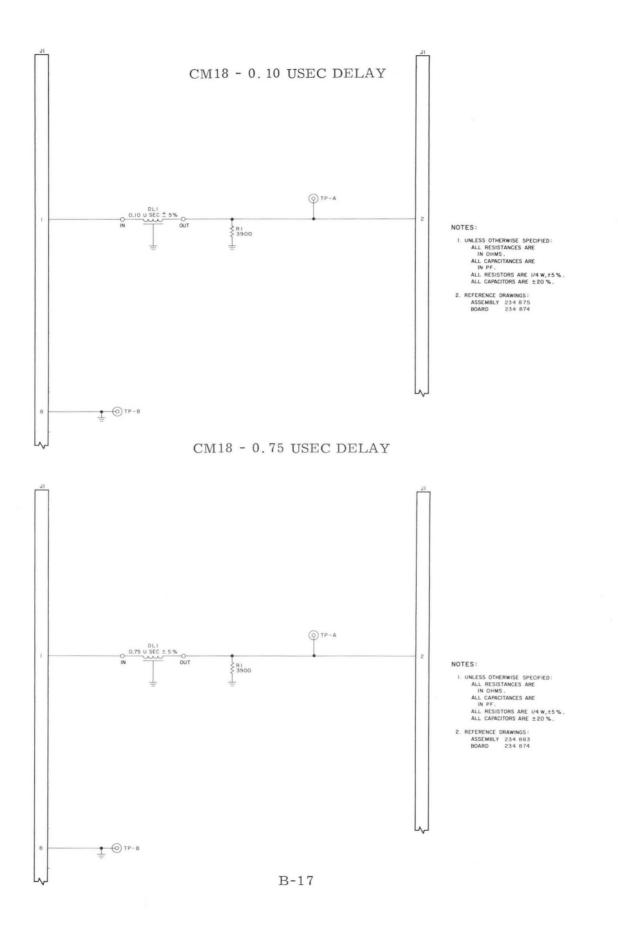

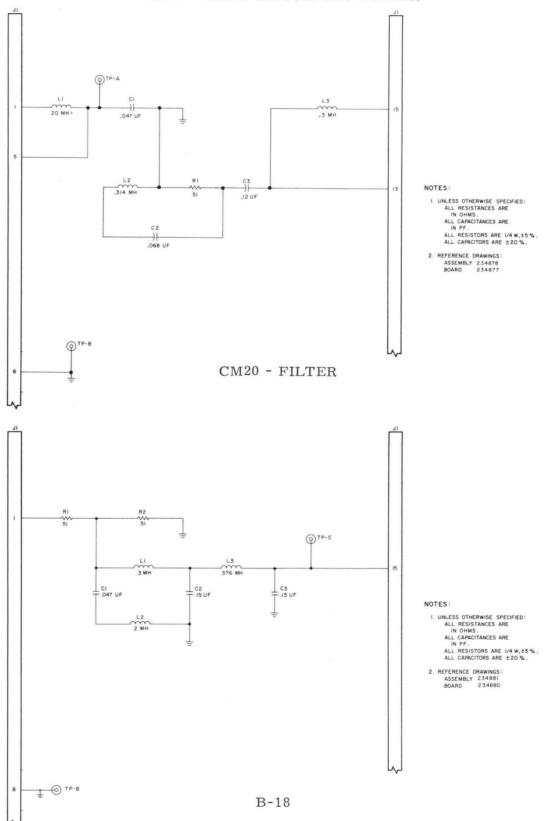

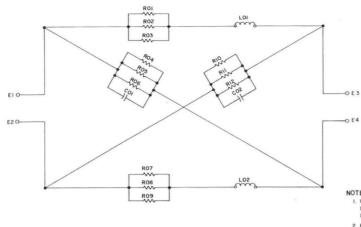

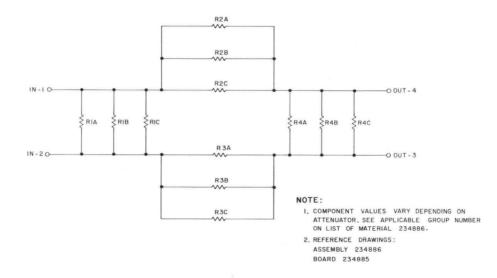

| Schematics                           | B-1    |

## FIGURES

| 1-1 | Digital Communication<br>Terminal                   | 1-2  |

|-----|-----------------------------------------------------|------|

| 2-1 | Internal Controls                                   | 2-1  |

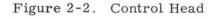

| 2-2 | Control Head                                        | 2-5  |

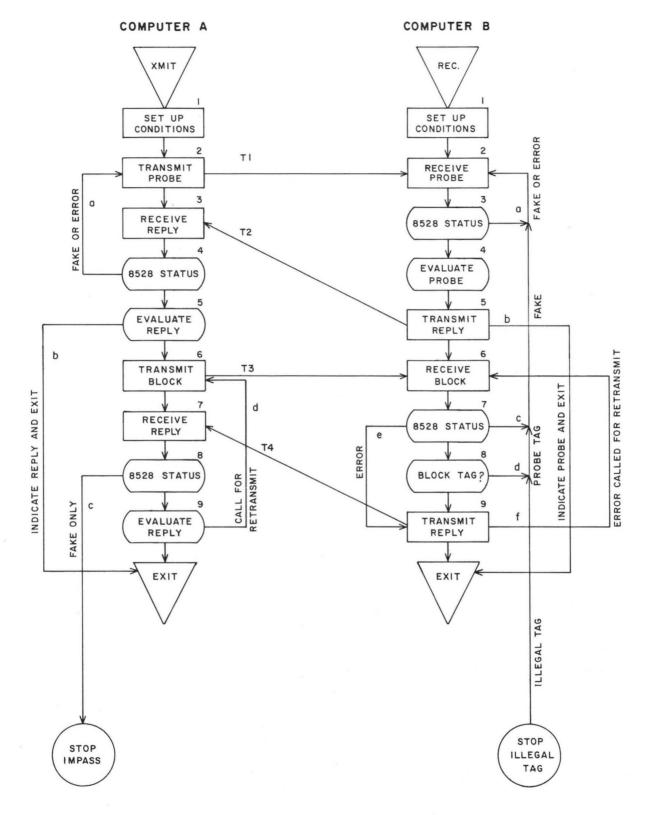

| 3-1 | Typical General Purpose<br>Receive/Transmit Routine | 3-3  |

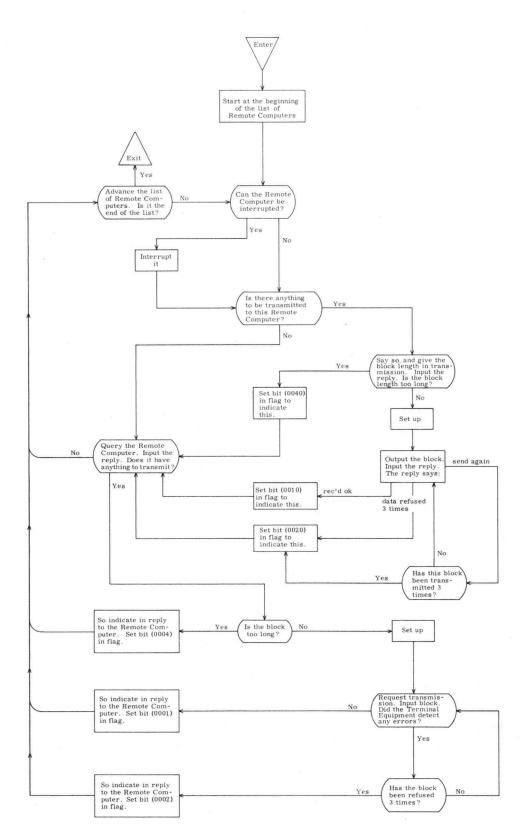

| 3-2 | Master Computer Routine                             | 3-5  |

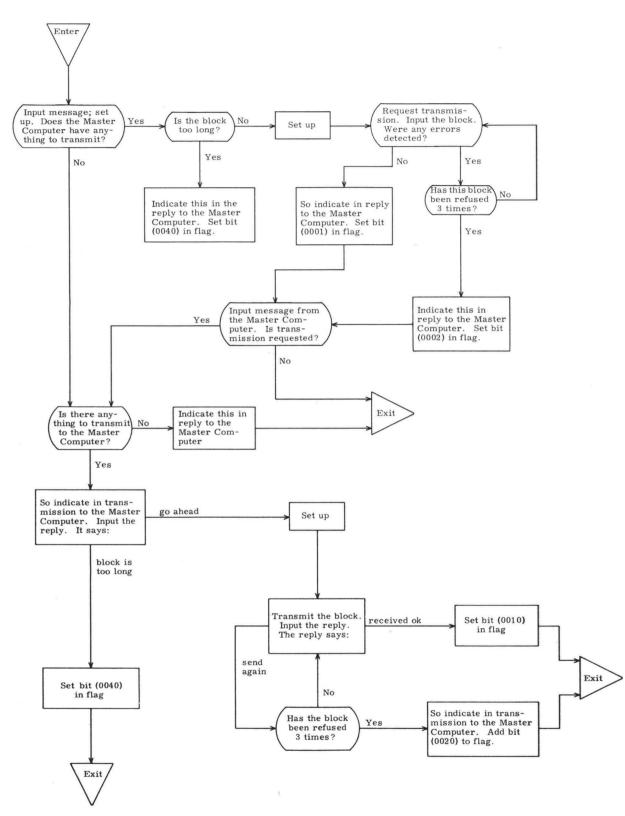

| 3-3 | Remote Computer Routine                             | 3-6  |

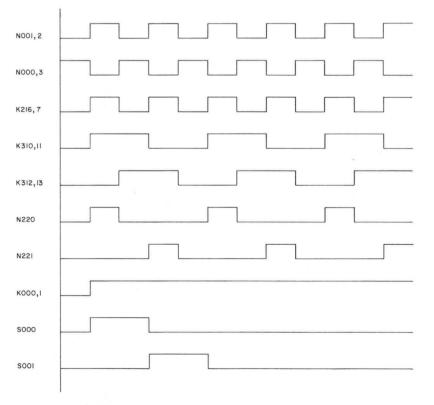

| 4-1 | Transmit Timing                                     | 4-1  |

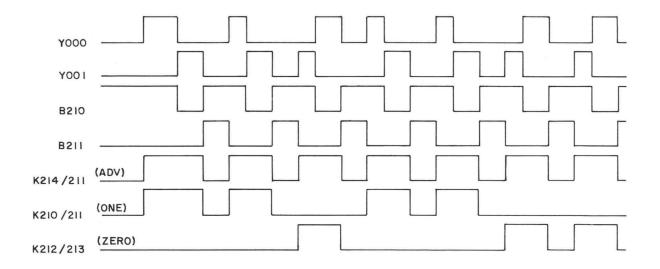

| 4-2 | Receive Timing                                      | 4-4  |

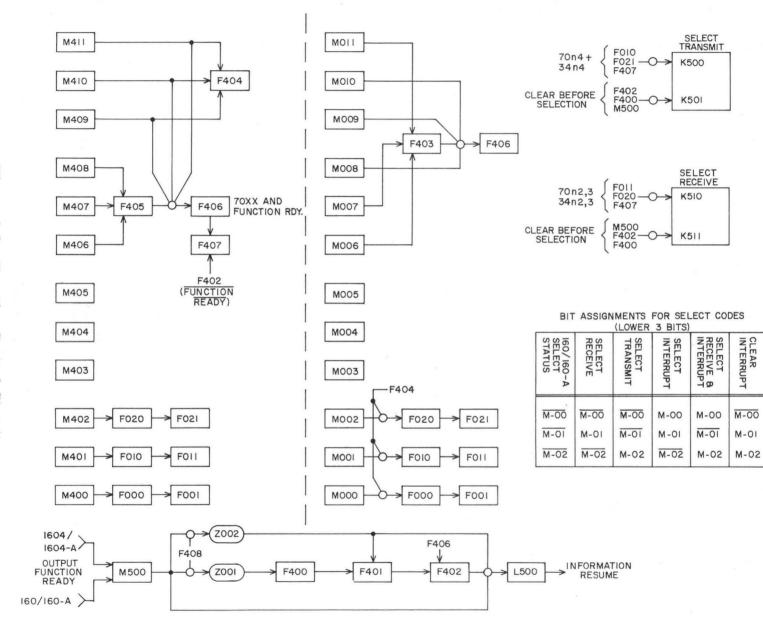

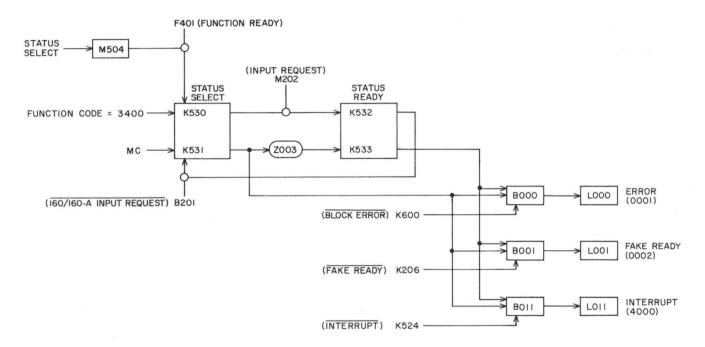

| 4-3 | Function Control Circuits                           | 4-7  |

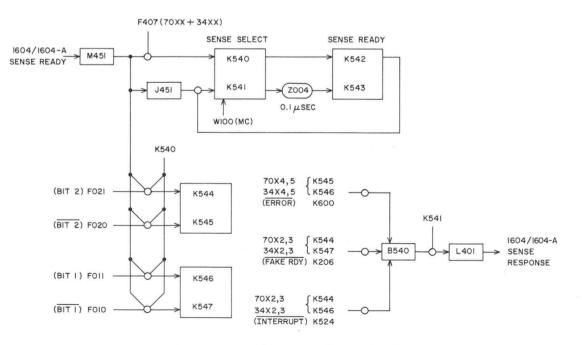

| 4-4 | 1604/1604-A Sense Codes                             | 4-8  |

| 4-5 | 160/160-A Status Response                           | 4-9  |

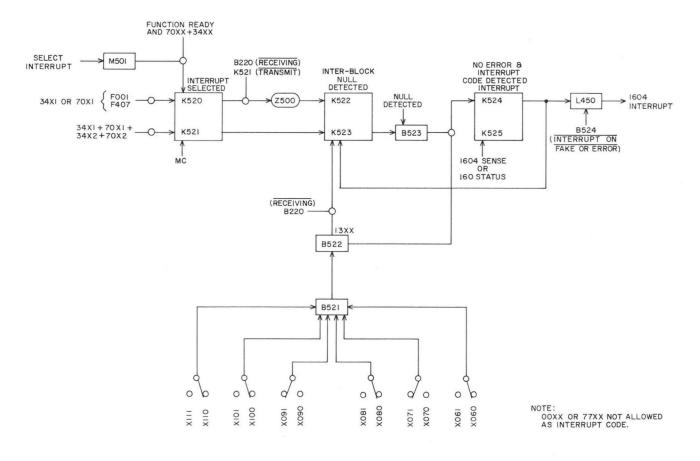

| 4-6 | Interrupt Logic                                     | 4-10 |

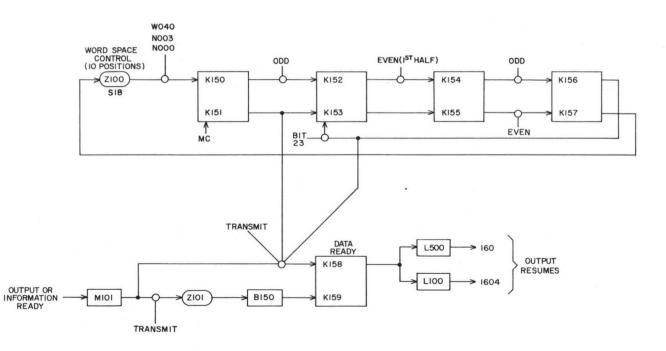

| 4-7 | Output Resume                                       | 4-11 |

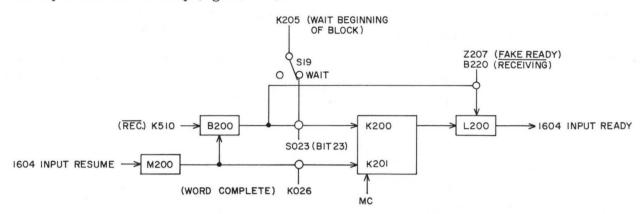

| 4-8 | 1604/1604-A Input Ready/<br>Resume                  | 4-12 |

| 4-9  | Input Request Ready            | 4-13 |

|------|--------------------------------|------|

| 4-10 | Ready/Resume Timing            | 4-13 |

| 4-11 | Transmission Circuits          | 4-16 |

| 4-12 | Mixer Input                    | 4-17 |

| 4-13 | Transmit Pyramid and<br>Output | 4-18 |

| 4-14 | Bit and Timing Detector        | 4-19 |

| 5-1  | Cabinet Interior               | 5-2  |

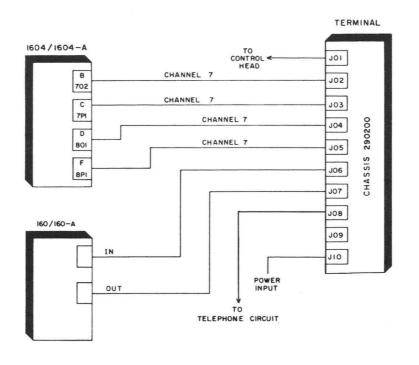

| 5-2  | Cabling Diagram                | 5-3  |

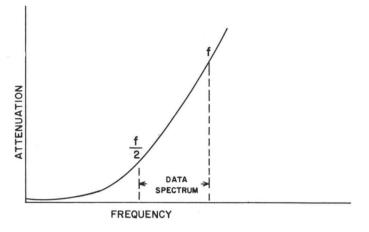

| 5-3a | Cable Response Curve<br>(Best) | 5-9  |

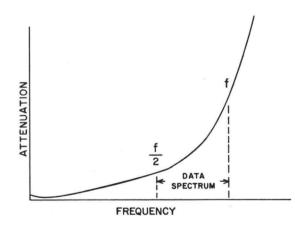

| 5-3b | Cable Response Curve<br>(Poor) | 5-9  |

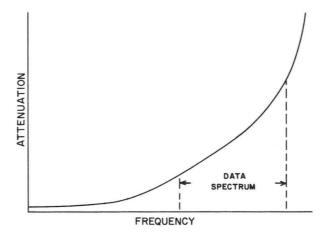

| 5-3c | Cable Response Curve<br>(Good) | 5-10 |

|      |                                |      |

## TABLES

| 1-1 | $1604/1604-A$ $\longrightarrow$ Terminal | 1-3 | 1-3 | Select and Sense Codes | 1-5 |

|-----|------------------------------------------|-----|-----|------------------------|-----|

| 1-2 | 160/160-A ←→ Terminal                    | 1-4 | 5-1 | Maximum Cable Lengths  | 5-8 |

# CHAPTER I DESCRIPTION

The CONTROL DATA<sup>\*</sup> 8528 Digital Communication Terminal is an inter-computer communication device which provides long distance serial data transfer at high speeds under program control.

Twelve bits of data are transferred between computer and terminal over standard parallel logic cables; the terminal equipments transmit and receive 24 serial bits for each 12-bit computer word. The first 12 serial bits are data; 100% redundancy is used for error detection at the receiving terminal equipment. The data and redundancy are transmitted as one 24-bit word. The serial data can be transferred on a single duplex channel by coaxial cable, microwave, or leased landline telephone.

Either party line or private line techniques can be used on as many as seven independent serial communication channels. (Logic for one channel is furnished as standard equipment; the other six are optional.) Communication networks can be expanded almost indefinitely by using combinations of the two techniques.

One audio communication facility between terminal locations is provided as standard equipment for the first channel. A test simulator for computer free maintenance is incorporated in the equipment.

## PHYSICAL DESCRIPTION

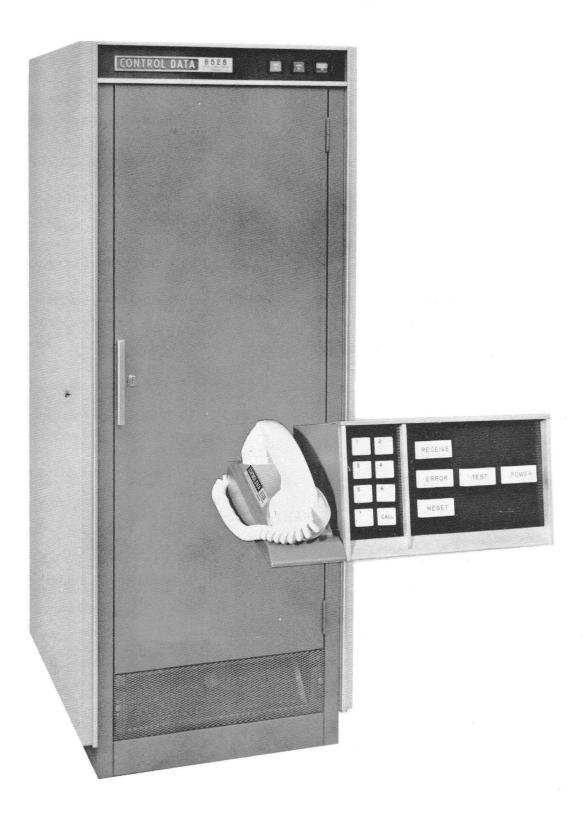

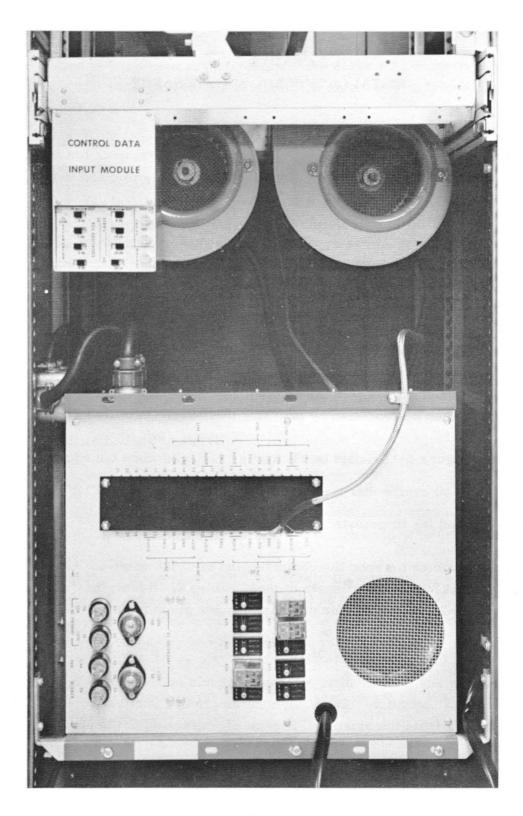

### CABINET

The logic chassis containing the printed circuit logic cards, power supply, blower unit, and video logic are housed in a cabinet. The cabinet is 61 inches high,  $25 \ 1/2$  inches deep,  $24 \ 1/2$  inches wide and weighs approximately 400 pounds. The logic chassis are slide mounted in the cabinet. There are three blowers in the cabinet; one at the base for pressurizing and two under the chassis for cooling.

Equipment operating requirements are a maximum of 400 watts of 110 volt, 60 cycle power, and a normal room temperature not exceeding  $80^{\circ}$ F.

<sup>\*</sup>Registered trademark of Control Data Corporation.

1 - 2

## CONTROL HEAD

The main operation switches and the audio handset are in a desk-top control head which can be placed near the operator.

## PRINCIPLES OF OPERATION

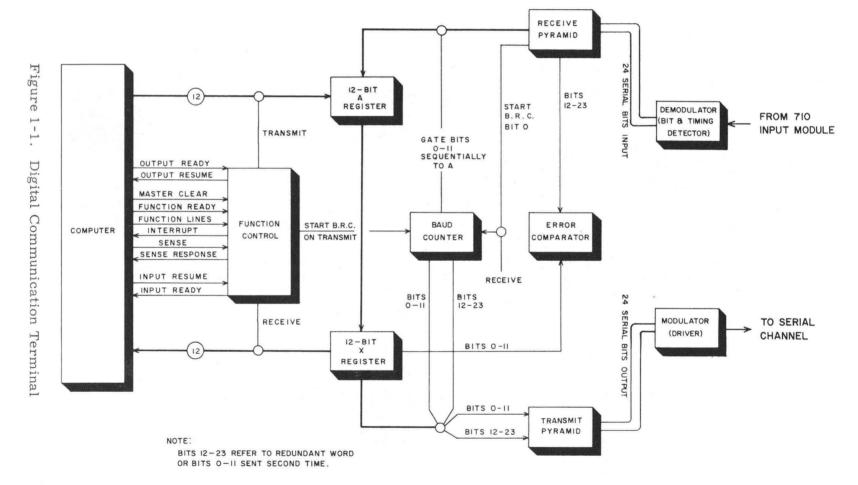

Parallel data and control signals are conveyed between the computer and terminal equipment over standard parallel logic cables. Four cables connect the terminal to the high speed transfer channel of the 1604/1604-A computer, two cables to channel 7 (input) and two cables to channel 8 (output). Two cables are required when a 160/160-A or 924/924-A computer is being used, one for normal or buffer input and one for normal or buffer output. Only one computer can be connected to a terminal at any time via parallel logic cables. The block diagram (figure 1-1) shows the terminal and control signals when the terminal equipment is connected to the 1604/1604-A computer. The terminal can operate with the 924/924-A in 160 mode without modification.

## CONTROL SIGNALS

Data flow between computer and terminal is maintained by a sequence of control signals (tables 1-1 and 1-2).

| Signal         | Origin   | Description                                                                                                                                  |

|----------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------|

| Function Ready | Computer | A 12-bit external function code is available for<br>translation. Translation is contingent on proper<br>equipment select digits in the code. |

| Output Ready   | Computer | A 12-bit word is available to the terminal for transmission.                                                                                 |

| Output Resume  | Terminal | Response to Output Ready which indicates terminal<br>has accepted computer word and is ready for<br>another.                                 |

| Input Ready    | Terminal | Terminal has a word available for computer.                                                                                                  |

| Input Resume   | Computer | Computer has accepted a word and is ready for another.                                                                                       |

| Sense Ready    | Computer | Samples sense circuit of terminal for presence of condition specified by external function code.                                             |

| Sense Response | Terminal | Response to Sense Ready which indicates presence<br>of condition specified by external function code.                                        |

| TABLE 1-1 | . 1604 | 1604-A | ←→TERMINAL |

|-----------|--------|--------|------------|

|-----------|--------|--------|------------|

## TABLE 1-1. $1604/1604-A \leftrightarrow TERMINAL$ (Cont'd)

| Signal       | Origin   | Description                                                                                         |

|--------------|----------|-----------------------------------------------------------------------------------------------------|

| Interrupt    | Terminal | Causes computer to interrupt main program, deter-<br>mine cause of interrupt and take action on it. |

| Master Clear | Computer | Establishes initial operating conditions within terminal.                                           |

| Signal            | Origin   | Description                                                                                                                                                                                      |

|-------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Function Ready    | Computer | Accompanies external function code and causes<br>equipment to examine the external function code<br>(turned off by Output Resume).                                                               |

| Information Ready | Computer | A 12-bit word is available to the terminal for transmission. Turned off by Output Resume.                                                                                                        |

| Output Resume     | Terminal | Response to Information Ready or Function Ready<br>indicating terminal has accepted computer word<br>and is ready for another. Turned off by dropping<br>of Information Ready or Function Ready. |

| Input Ready       | Terminal | Terminal has a word available for computer.                                                                                                                                                      |

| Input Request     | Computer | Computer is ready for an input word.                                                                                                                                                             |

| Interrupt         | Terminal | Causes computer to interrupt main program, determine cause of interrupt and take action on it.                                                                                                   |

| Master Clear      | Computer | Establishes initial operating conditions within terminal.                                                                                                                                        |

| Input Active      | Computer | 160 only.                                                                                                                                                                                        |

| Disconnect        | Terminal | Discontinues input operation.                                                                                                                                                                    |

## TABLE 1-2. 160/160-A ↔ TERMINAL

#### FUNCTION CODES

Local terminal equipment operations are initiated by coded external function instructions. The upper 6 bits select the terminal equipment; the lower bits specify the serial communication channel and operation requested. An accompanying Function Ready signal allows recognition of the 12 bits as an external function code. The external function codes vary with the type of computer using the terminal equipment.

The sense code or status response indicates to the computer conditions within the terminal equipment. Either the presence or absence of the condition can be sensed.

## TABLE 1-3. SELECT AND SENSE CODES

|        | Select Co | odes                        |                           | Function          | •                |

|--------|-----------|-----------------------------|---------------------------|-------------------|------------------|

| 1604/1 | 604-A     | 160/160-A                   | -                         |                   |                  |

| 7407   | 70n1      | 34n1*                       | Select Interr             | upt and Select Ch | nannel n         |

| 7407   | 70n2      | 34n2                        | Select Recei              | ve and Select Cha | annel n          |

| 7407   | 70n3      | 34n3                        | Select Recei<br>Channel n | ve and Interrupt  | and Select       |

| 7407   | 70n4      | 34n4                        | Select Trans              | mit and Select C  | hannel n         |

| 7407   | 70n6      | 34n6                        | Clear Interr              | upt Selection and | Select Channel n |

|        |           | 34n0                        | Select Status             | and Select Chan   | nel n            |

|        |           |                             |                           |                   |                  |

|        |           | 1604/1604-A                 |                           | 160               | )/160-A          |

| Sense  | Code      | Indica                      | tion                      | Status Reply      | Indication       |

| 7477   | 70n0      | Exit on Data T              | erminal                   | 0001              | Error            |

|        | -         | Interrupt                   |                           | 0002              | Fake Ready Set   |

| 7477   | 70n1      | Exit on No Dat<br>Interrupt | a Terminal                | 4000              | Interrupt        |

| 7477   | 70n2      | Exit on Fake Block          |                           |                   |                  |

| 7477   | 70n3      | Exit on No Fake Block       |                           |                   |                  |

| 7477   | 70n4      | Exit on Detected Errors     |                           |                   |                  |

| 7477   | 70n5      | Exit on No Det              | ected Errors              |                   |                  |

## Select Codes

<u>Select Transmit and Select Channel n</u>: Upon receipt and translation of this code, the terminal prepares to transmit data on the independent serial communication channel n. If n = 0 the terminal will transmit on all connected channels simultaneously.

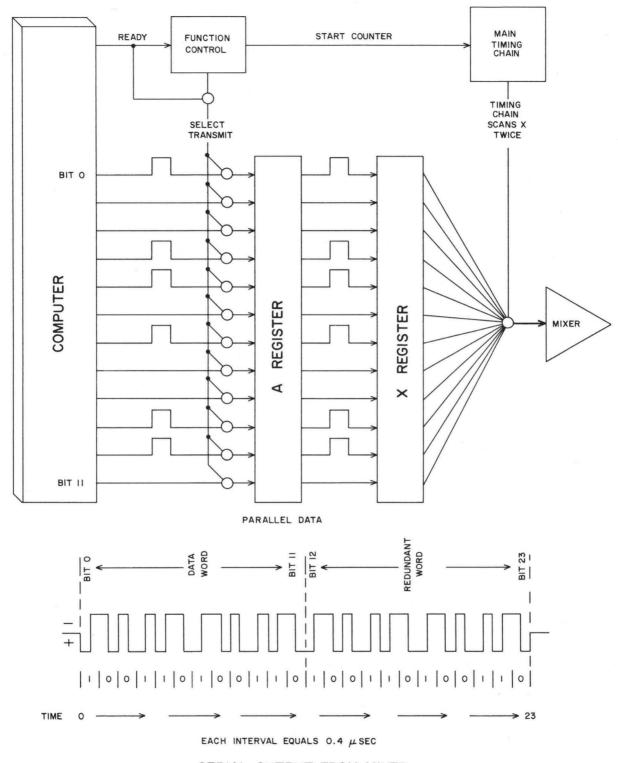

After the terminal has established the initial transmission conditions, the computer places a 12-bit (parallel) word and a ready signal on the output lines. The word is passed into a Buffer register, A, and transferred to a second register, X. A baud counter scans the X register at a predetermined rate, gating bits 0 through 11 sequentially to the transmission line. The X register is immediately scanned a second time, gating bits 12 through 23 to the transmission line. These bits form the redundant word for error detection at the receiving terminal equipment. (Data plus redundancy comprise a 24-bit serial word.)

<sup>\*</sup>Only 160-A or 924/924-A in 160 mode will be interrupted.

When the entire 24 bits have been transmitted and an exchange of ready and resume signals has occurred, the next computer word is ready to be serialized.

Words are separated by short controlled null periods; blocks are separated by longer nulls. The length of inter-block null periods varies according to the computer program and is set to a minimum limit by the terminal. Inter-word null periods are selected by the Word Space Control (WSC) switch and remain constant during an operation.

<u>Select Receive and Select Line n</u>: Unless transmit is selected, a terminal will monitor the serial channel. Any data received will be assembled as though the data were being transferred to the computer. A receive selection enables the actual transfer of data to the computer.

During reception, the A register acts as an assembly register. Incoming serial data after an inter-word null causes the counter to start gating bits 0 through 11 into A. When assembly of the first 12 bits is complete, the word is transferred to X; an error detection circuit compares each incoming bit of the redundant word with its corresponding stage of X. The contents of X are sent to the computer. If a block or word received is in error a FF will set, lighting the red Error light on the control head.

The 24th bit signifies the end of a word and the A register is cleared (after error comparison) to receive the following word. The X register is cleared after receipt of bit 10 of the following word. This allows for data comparison without interferring with the incoming word.

Select Receive and Interrupt and Select Channel n: This code is permissible only under certain program conditions. If it is programmed on a 160/160-A or 924/924-A computer, it may be followed by an input instruction. One of the following instances will apply:

- a) Input word is the correct interrupt code word (no error). An interrupt will occur.

- b) Input word is not the correct interrupt code word.

No interrupt will occur.

- c) No input word at all. (A status check should reveal a Fake Ready if timed wait for data is in effect.) No interrupt will occur.

If this code is programmed on the 1604/1604-A following a 62 instruction, the interrupt and a ready may occur simultaneously, permitting an entire block to be accepted before recognizing the interrupt.

Select Interrupt and Select Line n: During an interrupt selection the terminal equipment compares the first word<sup>\*</sup> of each block of data received with a predesignated interrupt code. If the two match and no error is detected, an interrupt signal is activated and the main computer program is interrupted. The interrupt code word is set manually by six switches. The word can be anything except 00XX<sub>8</sub>.

A switch provides two options for this select code: Program Cleared Interrupt Selection (PCI) and Function Cleared Interrupt Selection (FCI).

- PCI In this position a sense code or status request will clear the interrupt condition (not the selection) after sampling. The selection can be cleared by a computer master clear or by a clear interrupt selection (34n6) only.

- FCI In this position, a 34nX function code, with X even, will clear the Interrupt Selected FF when executed. If X is odd, the Interrupt Selected FF will be set, or will remain set.

## 8528 CHARACTERISTICS

### STANDARD

Communication established and transfer effected through program control. Error detection hardware incorporated.

Parallel Interface (12 bits)

Compatible with - 160/160-A 924/924-A (160 mode) 1604/1604-A

A test simulator is provided for computer free serial channel maintenance.

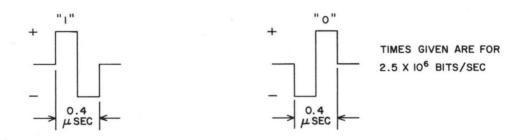

Serial Data Format

Split Phase Discontinuous; word by word basis Asynchronous on serial input Variable block lengths 12-bit serial word plus 12-bit redundancy

<sup>\*</sup> First word is the word preceded by an inter-block null.

Peak Serial Data Rate Word Rate During Block 2.5 x  $10^{6}$  bits per second (fixed) Adjustable to maximum determined by formula:

$$\frac{1}{25 \text{ x} 1}$$

peak rate

20v p-p, 75  $\Omega$  load, balanced 10 mv p-p, 75  $\Omega$  load, balanced 0.5 mc to 3.5 mc at 2.5 x 10<sup>6</sup> bits per second

Multiplexed into data channel

Output Input Requirements Band Width Required

Audio

Equalization for up to 1.5 miles of RG-22/BU cable.

Coded Interrupt

Switch Selections

Time/Indefinite Wait for Data Wait/Not Wait Beginning of Block Interrupt on Error Interrupt on Fake Ready Disconnect on Error Disconnect on Fake Ready Interrupt Selection cleared under program control in two ways:

| PCI | 34n6         |

|-----|--------------|

| FCI | 34nX, X even |

## OPTIONS

Up to six additional serial communication channels Any fixed bit rate from  $3 \times 10^3$  to  $5 \times 10^6$  bits/sec  $512_{10}$  word error counter Output impedance of 50, 75, 100, or 125  $\Omega$ Equalization as required for cable other than RG-22/BU Cable exchange boxes other than those required to connect RG-108/U to RG-22/BU External pads and attenuators Receive and transmit on single cable Single ended operation Audio on/off data channel - must be removed at peak bit rates less than

$0.5 \times 10^6$  bits/sec

# CHAPTER II OPERATION

This chapter contains information necessary for operating the digital communication terminal after the power, communication channels, and control cables have been connected.

## MAIN CABINET CONTROLS AND INDICATORS

Switches on the main cabinet are used primarily for establishing initial operating conditions or for maintenance.

| EXTERNAL             |      |                                                                                                                                            |

|----------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------|

| Power On (Blue)      | S/I* | When pressed, full operating power is applied to the terminal equipment.                                                                   |

| Power Off (Red)      | S/I  | When pressed, turns off all operating power and the Power On light.                                                                        |

| +20/-20 (White/Blue) | Ι    | The upper half of this indicator lights when $+20$ vdc is being applied to the system. The lower half indicates that $-20$ vdc is applied. |

## INTERNAL

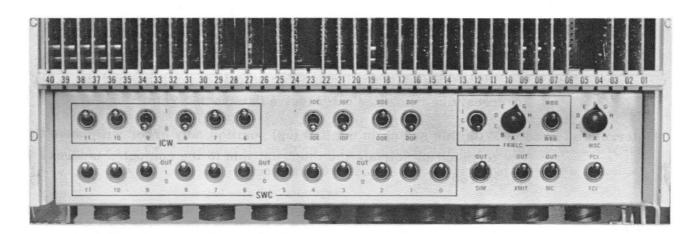

These controls are located on the lower quarter of the logic chassis (figure 2-1).

Figure 2-1. Internal Controls

\* S = Switch

I = Indicator

#### Interrupt Code Word (ICW)

The position of these six switches determines the interrupt code word. This word can be anything except  $00XX_8$ . In most instances each terminal in a network is assigned a different interrupt code, corresponding to the master program. If the computer connected is a 160-A, an address 40 interrupt will occur if bit 0 of the interrupt word is even; an address 30 interrupt will occur if bit 0 is odd.

Simulator

The switches controlling simulator operation consist of the 12 Simulator Word Control (SWC) switches, and three master switches. The master switches are SIM, XMIT, and MC.

To use the simulator, throw the SIM switch down. Select a word by setting the SWC switches to some combination of "1's" and "0's". Placing the XMIT switch in the down position will cause the selected word (the one set by the SWC switches) to be continuously transmitted. To return the 8528 to normal operation, throw all simulator switches to the OUT position and toggle the MC switch. All of these switches must be the OUT position for normal operation.

Word Space Control This ten-position rotary switch controls the spacing between each (WSC) This ten-position rotary switch controls the spacing between each transmitted word and is variable at each installation. The 160/ 160-A computers can send one 12-bit word every 19.0 usec. Since it takes the terminal 9.6 usec to send a 24-bit serial word (at  $2.5 \ge 10^6$  bits/sec), the time between words will be approximately 9.4 usec. The 1604/1604-A can send one every 6.8 usec; in this case the word space can be cut to a minimum if the receiving computer can receive data at that rate.

\*Interrupt on Error With this switch in the IOE (up) position, any error will cause the terminal to activate the interrupt line to the computer (address 40 on 160-A).

\*Interrupt on Fake If the IOF switch is in the IOF (up) position, a Fake Ready signal (IOF) (see FRWLC) causes the terminal to activate the interrupt line (address 40 on 160-A).

\* Sense or status responses will not indicate an interrupt.

Disconnect on Error (DOE) -(160/160-A only)

Disconnect on Fake (DOF) -(160/160-A only)

Fake Ready Wait Length Control (FRWLC) If this switch is in the DOE (up) position, an error in reception will cause an Input Disconnect signal to be sent to the computer. This terminates the input instruction without counting up the buffer field.

With the switch in the DOF (up) position, the terminal will activate the Input Disconnect line when a Fake Ready signal is generated (see FRWLC). This will terminate the input instruction without counting the buffer field further.

These controls consist of a three-position switch, a ten-position rotary switch and the WBB switch.

The ten-position rotary switch varies the length of time the terminal will hang up the computer to await data. If receive is selected immediately before the input instruction and no data is received within the specified time limit, the terminal generates Fake Ready signals for the computer. This allows the input instruction to be completed.

By placing the three-position switch in the INDEFINITE (I) position, the operator can terminate the input instruction by momentarily pressing the Reset button on the control head. The CONTINUOUS (C) position causes Fake Ready signals as soon as receive is selected. In the TIMED WAIT (T) position, Fake Ready signals are sent to the computer after a predetermined delay. The timed wait is determined by the ten-position rotary switch.

With receive selected and the Wait Beginning of Block switch in the WBB (up) position, the terminal cannot transfer any words it may receive until it senses the beginning of a block. This prevents the computer from receiving a block of data out of sequence.

If this switch is in the  $\overline{\text{WBB}}$  (down) position, the terminal will transfer incoming data to the computer as soon as the terminal is selected to receive.

Normally this switch will remain in the WBB position because programming usually stipulates that the computer examine the first several words (depending on format) in each block for procedural data and/or tags. In the WBB position it would be possible for the computer to examine any word of a block as though it were the first word.

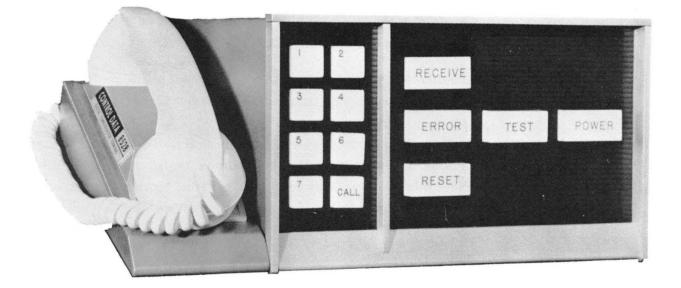

## CONTROL HEAD INDICATORS AND SWITCHES

The more frequently used indicators and switches are on the control head. A single logic cable connects the control head to the main cabinet.

| Power (Green)   | I*   | When lit, indicates that 115 vac is applied to circuits in the terminal.                                                                                                                                                                                                                                                   |

|-----------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Test (White)    | I    | Lights if any of the simulator switches are in a position other than OUT.                                                                                                                                                                                                                                                  |

| Receive (Green) | I    | Lights when the computer has selected the terminal to<br>receive. If short blocks of data are being received, the<br>time period will be too short for the light to change state.                                                                                                                                          |

| Error (Red)     | I    | Lights if an error occurred during reception of a block of<br>data. A sense or status function code automatically clears<br>the indication. If short blocks are being received and<br>errors are sensed at the end of each block, the light will<br>not be visible.                                                        |

| Reset (Amber)   | S/I* | If the terminal has been selected to receive and data does<br>not arrive by the time the FRWLC signal terminates, the<br>Reset indicator lights. This signifies that a false block of<br>data has been sent to the computer to terminate the input<br>instruction (short blocks may not change the state of the<br>light). |

|                 |      | If the FRWLC switch is in the I position and receive is<br>selected, the operator can terminate the input instruction<br>at any time by momentarily pressing the Reset button. If<br>data is present no Fake Ready will occur.                                                                                             |

|                 |      | If the FRWLC switch is in the T position, the operator can<br>change to I by holding down the button before receive is<br>selected, and continuing to hold it down. Releasing the<br>button returns the terminal equipment to timed wait status.                                                                           |

| * S = Switch    |      |                                                                                                                                                                                                                                                                                                                            |

I = Indicator

#### Call (White)

Any or all of the stations on a network may be signalled by removing the handset from the cradle and pressing the appropriate Audio Line Selector buttons and then the Call button. Hold the Call button in until the parties answer or until it is determined they are not available.

Audio Line Selector S/I (1 through 7)

S/I

An incoming call will light the Audio Line Selector indicator corresponding to the number of the calling station and an audio tone will emanate from the loudspeaker.

To answer a call remove the handset from the cradle, momentarily press the appropriate Audio Line Selector button to engage the line, and push the Push to Talk button on the handset. Replacing the handset removes all selections.

#### CHAPTER III

## PROGRAMMING

Programming information in this section presupposes some knowledge of programming procedures. The material is intended to serve as a guide for establishing communication between computers linked by terminal equipments.

Each computer on a serial communication network must have a transmit routine and a receive routine previously programmed before data can be transferred. The receive routine must designate the initial and terminal addresses of the block reserved for receipt of data; the only other major consideration is that the transmit and receive routines be able to accommodate each other with minimum loss of time.

The terminal equipment does not differentiate between straight data and procedural information. This distinction must be made in programming. Usually it will be necessary for both routines to contain transmit and receive subroutines in order to establish terms of contact.

#### EXAMPLE A (TWO COMPUTER PRIVATE SYSTEM)

The flow chart in figure 3-1 illustrates a data transfer without the use of interrupt. The transfer is initiated by the computer which is to transmit.

Assume that computer B is in the receive subroutine (loop Ba), and that computer A is to enter the transmit subroutine. Whichever computer enters the transmit or receive subroutine first must wait for the other to respond. The length of the wait period will depend on the relative events in the two main programs which lead to the entrance of the subroutines.

#### Computer B

- B1 Computer B enters receive subroutine. The conditions inserted by the main program are: loop limits, initial and terminal addresses, maximum block limits, line selection.

- B2 Select 8528 to receive. The FRWLC must be in the T position and WBB in effect.

- B3 Interrogate 8528. If response does not indicate a fake block or an error, continue to B4.

If an error or fake block is indicated, take loop Ba to B2.

- B4 If in B3 neither an error nor a fake block is found, the block length is compared with the predetermined limit. If it is in excess, go to B5. If not, go to B6.

- B5 If limit was exceeded, indicate and exit or stop.

- B6 Wait for block of data.

- B7 Interrogate. A fake block indicates either that B did not select receive quickly enough to satisfy WBB or the reply back to A was in error. In either case, loop Bc will be cycled.

- B8 If no error or fake block was indicated in B7, examine first word (tag) of block. If tag indicates A is still in loop Aa, B cycles loop Bd. If tag is not listed, stop. If an error is detected, call for retransmission and go to B9.

- B9 Transmit call for retransmission if necessary, then return to B6 (loop Bf). If no retransmission is necessary, exit.

#### Computer A

- A1 Enter transmit subroutine, set initial conditions.

- A2 Select 8528 to transmit and send message indicating block length.

- A3 Select receive with timed wait for data and WBB in effect.

- A4 Interrogate. If an error or a fake block is indicated, cycle back to A2 through loop Aa.

- A5 If, in A4, no error or fake block was indicated, evaluate reply. If negative, indicate and exit or stop. If affirmative, proceed to A6.

- A6 Transmit block.

- A7 Select receive and await reply.

A8 If fake block terminates transmission, interrogate. If no fake or error, exit. If an error occurs assume a call for retransmission was sent.

Unless computer A receives an affirmative final reply without error, computer A cannot be certain that the block was received. Likewise computer B cannot be certain that its reply was received, but the exchange of replies must stop eventually if any additional information is to be transferred. The action of the last reply will be greatly influenced by the initial choice of the mode of communication (interrupt or probe) and which computer initiates the transaction.

Figure 3-1. Typical General Purpose Receive/Transmit Routine.

#### EXAMPLE B (MULTI-COMPUTER NETWORK)

When more than two computers are to communicate on a party line basis, it is convenient to assign the task of directing the flow of information to a master computer; other computers on the line are referred to as remote computers. The master computer program must include a subroutine for each remote computer. This subroutine includes (1) the unique designation of the remote computer (2) starting and terminating addresses of the data to be transmitted to the remote computer (3) starting and terminating addresses of the block reserved for receipt of data from the remote computer, and (4) the flag which indicates to the main program what the subroutine accomplishes. When the main program enters the list of subroutines, each remote terminal is probed in turn. If the remote terminal can be interrupted, the subroutine interrupts it. The terminal equipment continuously monitors the serial communication channels unless selected to transmit. If the correct interrupt code word is received at the beginning of a block and the word is not in error, an Interrupt FF sets and the interrupt line to the computer is activated. If the remote terminal cannot be interrupted, it must sense the Interrupt FF to determine if it is being probed. For programming simplification, the following rules are arbitrarily adopted:

- Remote computers can communicate only with the master computer. The master computer must periodically interrogate (probe) the remote computers to determine what action, if any, should be taken on or by a specific remote computer.

- 2) Remote computers cannot interrupt the master computer. The remote computer must recognize the probe.

The probe from the master computer may be a procedural probe or an interrupt (if the remote computer can be interrupted). The procedural probe (data in a fixed format) is used to define communications procedures to a receiving computer. An interrupt code word sent by the master computer will cause a remote computer to cycle until it receives instructions via a procedural message.

A typical master computer routine for a number of remote computers is shown in figure 3-2. It will accommodate computers which can or cannot be interrupted. The routine for a remote computer is shown in figure 3-3.

Figure 3-2. Master Computer Routine

Figure 3-3. Remote Computer Routine

Only a few programming possibilities have been touched on here. In a sense there is as much flexibility in the system as there is flexibility in programming. The use of interrupt will prevent one computer from waiting for data for any great length of time; however, unless fixed block lengths are to be used, the length of each block and conditions of contact must be communicated as in example A.

## PROGRAMMING AIDS

## EFFECTS OF FAKE READY OR WBB

If receive is selected while data is coming in and WBB is in effect, the fake ready will not occur until the end of the block has been received and the timed wait period has expired. If the interrupted portion of the block is longer than the timed wait, the fake ready will occur at the end of the block. If the timed wait expires after the block has been received, the fake ready will occur at the time of expiration.

When the input is terminated, all remaining locations in the memory block used will be filled with the last word received in the interrupted block.

## FAKE READY WHEN NO DATA IS BEING RECEIVED

If receive is selected, no data is being received, and the fake ready delay expires, the fake ready will cause input words consisting of  $0000_8$  to be sent to the computer until the block is terminated.

#### LINE SELECTION

All function codes are translated relative to a line selection. However, the status or sense code responses indicate the status irrespective of line selection.

#### INTERRUPT ON ERROR OR FAKE READY

The interrupt line to the computer is activated as soon as an error or fake ready occurs. When an interrupt occurs because of the error or fake ready, a status or sense response would indicate this condition rather than an interrupt.

## STATUS AND SENSE

A status or sense code automatically clears the FFs indicating the conditions when the response has been returned to the computer.

## Status (160/160-A Only)

A status selection must be followed by a one word input. The program may provide for a status response by selecting receive without a one word input. The block received will then contain, as its first word, the status prior to the first word received. The first word of data will be the second word in the input block. The input block length must be increased by one to allow for the address occupied by the status response.

## RECEIVE AND INTERRUPT SELECTION WITH TIMED WAIT FOR DATA

After this selection a fake ready will occur if the block input is not terminated by a status or sense selection before the time period expires. From the occurrence of the fake ready until data is again being received, the word loaded into memory will be the last word of the previous block.

## DISCONNECT (160/160-A ONLY)

A disconnect caused by a fake ready or an error will terminate the input and stop the address count.

## RESTRICTIONS

- An input instruction must be initiated immediately after execution of select receive. Reasons:

- a) The computer data channels do not provide a Channel Active signal. Therefore, the timed wait for data must be conditioned on the receive selection.

- b) To insure that the input request is up by bit 11 time when the 160/160-A computer is being used.

- 2. A status request or sense code must be executed immediately after the termination of the input instruction. Reasons:

- a) To disengage the timed wait for data by clearing the receive selection.

- b) The terminal, unless actually transmitting, is always on line. Therefore, an error might occur after the information is correctly received.

- 3. In a multi-line system, if the remote stations are allowed to initiate transfers independently of the master, a status or sense request with a line selection other than "0" must be executed after a master clear. Reason:

- a) A master clear selects all lines; if data arrives on more than one line at the same time, an error will result.

- 4. On computers where the input/output rate is determined by the number of active channels, the activity of these channels must be eliminated during receive or transmit or the word rate and relative time delays must be slowed so that words during block transfers are uniformly spaced. Reasons:

- a) If the channels are active, the spacing between words on the serial channel will become greater than the WBB delay or interrupt null detector, thus causing an inter-word null to appear as an inter-block null.

- b) The terminal is basically a one word buffer. If the computer is not always ready to accept the following word by bit 11 time (160/160-A) or by bit 24 time (1604/1604-A) it will miss the words resulting in a fake ready.

## CHAPTER IV PRINCIPLES OF OPERATION

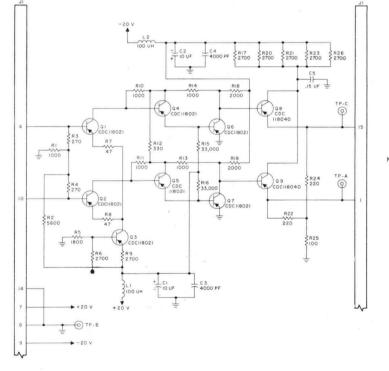

This chapter covers the logical operations occurring in the terminal equipment. The terminal equipment logic is constructed from standard CONTROL DATA 3600 building blocks. The special circuits in the terminal equipment are described in appendix B.

## TIMING

## TRANSMIT

Transmit operations are accomplished by executing an external function code (Select Transmit On Line n) followed by an output instruction. Receipt of the select code and subsequent execution of an output instruction causes the terminal equipment to react as described below. Figure 4-1 shows the main steps in transmit timing.

Those events which occur simultaneously are given in the sequence which has the most apparent logical significance.

Figure 4-1. Transmit Timing

| Step   | Event                                                           | Remarks                                                                                                                                                                                                                                                                                           |

|--------|-----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | Function Lines Up                                               | External function code made available to terminal.                                                                                                                                                                                                                                                |

| 2      | Function Ready                                                  | Appears after function lines have stabilized; permits ter-<br>minal to recognize data on function lines. In the case of<br>a 1604/1604-A this signal drops after 8 usec; if 160/160-A<br>computer is connected, the signal remains up until the<br>terminal equipment generates an Output Resume. |

| 2a     | Select Transmit FF                                              | Set by translation of the proper EF code in conjunction<br>with a Function Ready signal. Outputs of this FF enable<br>the transmit logic to respond when the computer begins<br>output operation.                                                                                                 |

| 3      | Output Resume<br>(160/160-A only)                               | This signal is generated by the terminal equipment after<br>the EF code has been translated; causes Function Ready<br>signal to drop; absence of Function Ready causes Output<br>Resume to drop.                                                                                                  |

| 4      | Output Ready (1604/<br>1604-A) Information<br>Ready (160/160-A) | Indicates that 12 bits of output data are available on the output lines.                                                                                                                                                                                                                          |

| 5      | $M \rightarrow A$                                               | After the data lines have had time to stabilize, the data<br>is transferred to the A register.                                                                                                                                                                                                    |

| 6      | $A \rightarrow X$                                               | Data in the X register is available for transmission; therefore the $A \rightarrow X$ transfer is effected early.                                                                                                                                                                                 |

| 7      | Timing Enable FF                                                | This FF is set on the first odd clock phase after the $M \rightarrow A$ transfer; clock pulses can then trigger the baud counter.                                                                                                                                                                 |

| 7a     | Baud Counter                                                    | The first even output of the frequency divider enables the<br>baud counter to begin its cycle. Successive stages in the<br>baud counter are set alternately by odd and even clock<br>phases.                                                                                                      |

| 8<br>9 | Sync FF<br>Sync Check FF                                        | These FFs synchronize the setting of the Drive Enable FF<br>with the gating of the first bit from the X register out of<br>the transmit pyramid into the serial channel.                                                                                                                          |

| 10     | Drive Enable                                                    | Set when first bit is available for transfer.                                                                                                                                                                                                                                                     |

4-2

| Step | Event         | Remarks                                                                                                                                                                                                                                                                                                                                                         |

|------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10a  | Data Ready    | Set when drive lines are enabled; enables Output Resume to computer.                                                                                                                                                                                                                                                                                            |

| 11   | Mixer FF      | Each bit from the transmit pyramid is gated into both<br>sides of the Mixer FF by odd and even clock pulses. The<br>output of the Mixer FF will therefore consist of a single<br>cycle for each bit.                                                                                                                                                            |

| 12   | Output Resume | This signal indicates to the computer that the word has<br>been serialized and that the terminal is ready for another<br>word. The Word Space Control (WSC) is adjusted to fix<br>the space between each word. Z099 is adjusted to control<br>the minimum delay between blocks. Serialization of the<br>next word cannot begin until these delays have expired. |

The baud counter transfers the 12 consecutive stages of the X register into the transmit pyramid as each counter stage sets. When all 12 stages of X have been gated into the transmit pyramid, the counter begins clearing on consecutive odd and even clock phases. This action gates the contents of X into the transmit pyramid for the second time to form the redundant part of the 24-bit word.

Transmission of the entire 24 bits occurs in 24 times the bit rate frequency. As bit 24 is sent, the A and X registers are cleared. An Output Resume signal is sent to the computer as soon as serialization is completed.

The entire sequence from step 4 is repeated for each word in the block.

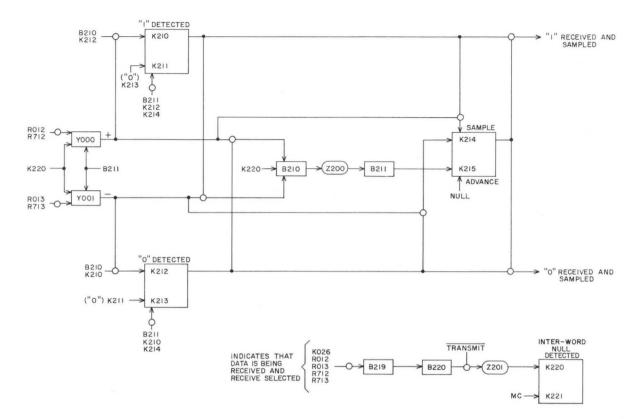

## RECEIVE

A receive operation is initiated by executing a Select Receive external function code followed by an input instruction.<sup>\*</sup> Figure 4-2 shows the main steps in receive timing.

<sup>\*</sup> Select Receive must be followed by an input instruction in the next program step if timed wait for data is used.

Figure 4-2. Receive Timing

| Step | Event                             | Remarks                                                                                                                                                                                                                                                                      |

|------|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | Function Lines Up                 | Function code appears on output lines.                                                                                                                                                                                                                                       |

| 2    | Function Ready                    | This signal from the computer appears after function<br>lines have stabilized and permits the 8528 to recognize<br>and translate function code.                                                                                                                              |

| 3    | Receive Selected FF               | This FF is set by the proper external function code in<br>conjunction with a Function Ready signal. Outputs enable<br>the receive circuits to react when input data is received.                                                                                             |

| 4    | Output Resume<br>(160/160-A only) | An Output Resume signal is generated by the terminal<br>equipment after the external function code is translated.<br>The Output Resume causes the computer to drop the<br>Function Ready signal. Absence of the Function Ready<br>causes the 8528 to drop the Output Resume. |

When the 8528 is not selected to transmit, the receive circuits continuously monitor the last selected serial channel. The data is received and assembled as it would be for a normal receive operation, but none of this data can be sent to the computer until receive

is selected. However, when receive is selected, the input data lines are enabled to the computer. This means that, immediately after receive is selected, either an input instruction must be executed or the FRWLC switch must be in the INDEFINITE WAIT position. In the Wait Beginning of Block (WBB) mode Input Ready signals are blocked if data is being received when receive is selected; the Input Ready cannot be sent until an inter-block null is detected by the WBB circuit. This insures that the computer will always begin receiving from the first word of a block. The following events occur:

| Step | Event                         | Remarks                                                                                                                                                                                                                                                                                      |

|------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5a   | Wait Beginning of<br>Block FF | If no information is presently being received, this FF sets<br>and enables the Input Ready FF.                                                                                                                                                                                               |

| 5b   | Signal Present<br>B220 = 0    | If information is being received, the output of this inverter<br>will prevent setting the Input Ready FF until one inter-<br>block null is detected. Failure to select receive before<br>the beginning of a block will cause a Fake Ready at the<br>end of the incoming data if WBB is used. |

| 6    | Sample Advance FF             | As information begins to trigger the threshold amplifiers,<br>this FF sets and clears at the rate of the incoming data.                                                                                                                                                                      |

| 7    | Timing Slave                  | This FF is set and cleared by the Sample Advance FF.<br>The output of the Timing Slave FF drives the frequency<br>divider during reception.                                                                                                                                                  |

| 8    | Baud Counter                  | The counter, indirectly driven by the incoming data, gates<br>the first 12 serial bits into consecutive stages of A.                                                                                                                                                                         |

| 9    | $A \rightarrow X$             | As bit 12 of the incoming word is gated into A, the con-<br>tents of A are transferred to the X register.                                                                                                                                                                                    |

| 10   | Error Detection               | The counter gates the second 12 bits received (the redun-<br>dant word) into a bank of inverters with the corresponding<br>bit of the data word in the X register. If the two agree,<br>no error is registered.                                                                              |

If an error occurs because of a mismatch between the contents of the X register and the incoming data, the Word and Block Error FF will be set. All data in the block will be transferred to the computer, even though there was an error. If the receiving computer is a 1604/1604-A, a "1" bit is transmitted to the computer and stored as bit 23 in the

same storage location as the word in error. The Word Error FF is cleared at bit 10 time of each word; that is, before the redundancy of the next word is compared to the data in X.

The Block Error FF is set when the Word Error FF is set for the first time during the receipt of any block. The Block Error FF and the Word Error FF light the red Error light on the control head. The light is cleared by a master clear, or sense or status request, if the last word received was correct. Thus, if any errors have occurred during the receipt of a block, that fact can be sensed at the end of a block.

| Step | Event                         | Remarks                                                                                                                                                                                                                                 |

|------|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11   | Input Ready                   | Signal from 8528 indicating to computer that a word is<br>available on the input lines. If the 160/160-A is being<br>used, the signal is initiated at bit 12 time; if 1604/1604-A<br>is being used, signal is initiated at bit 23 time. |

| 12   | $X \rightarrow \Gamma$        | The transfer is enabled when receive is selected and effected when the Input Ready FF is set.                                                                                                                                           |

| 13   | Input Resume<br>(1604/1604-A) | Signal to 8528 from computer indicating that the computer<br>has accepted the word. Receipt of the Input Resume<br>causes the 8528 to drop the Input Ready signal; the com-<br>puter then drops the Input Resume.                       |

| 14   | Clear A<br>Clear Counter      | Cleared prior to receipt of next word.                                                                                                                                                                                                  |

Steps 5-14 are repeated for each word of data received. When the computer buffer field has been filled, the input instruction is terminated at the computer. Fake Ready signals are generated by the 8528 to terminate the input instruction if data is absent for a time designated by the Fake Ready Wait Length Control position.

## CIRCUITS

#### FUNCTION CONTROL CIRCUITS

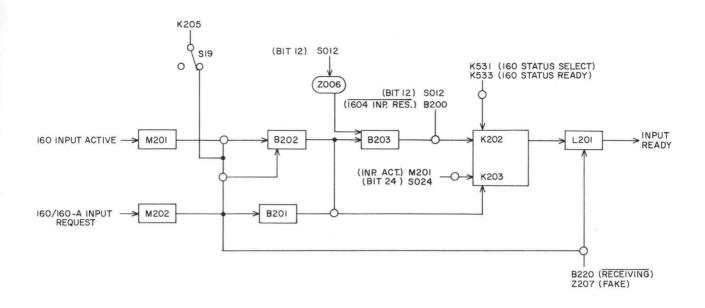

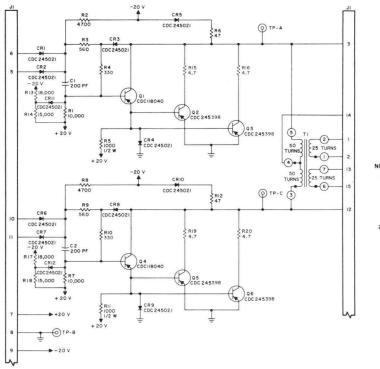

The function control circuits (figure 4-3) regulate data flow between the computer and the terminal equipment. All control signals and sense, status, and select information pass through these circuits for translation.

Figure 4-3. Function Control Circuits

4-7

External function codes from the 1604/1604-A computer are accompanied by a Function Ready or Sense Ready signal. This signal, in conjunction with the proper select digit, sets the control FFs. Outputs from the control FFs enable the circuits which are to perform the requested function. After 8 usec the computer automatically drops the external function code and the Ready signal.

The 12-bit output cable from the 160/160-A computer carries external function codes during an EF instruction and output data during an output instruction. The Function Ready signal differentiates between the two instructions.

The equipment select digits are the upper 6 bits of the external function code. Only the EF codes with the correct select digits (70<sub>8</sub> for the 1604/1604-A and 34<sub>8</sub> for the 160/160-A) will be translated by the terminal equipment.

## 1604/1604-A SENSE CODES

The 1604/1604-A computer determines the status of the terminal equipment through the use of external function sense codes. When accompanied by a Sense Ready signal, the sense code is translated, causing the Sense Ready FFs to be set or cleared to partially enable a specific response. The responses are enabled by outputs from the FFs storing the condition sensed (figure 4-4). The Sense Ready FFs are cleared when the Sense Ready signal from the 1604/1604-A drops.

Figure 4-4. 1604/1604-A Sense Codes

4-8

Either the presence or absence of a specific condition can be determined. A positive response is interpreted by the computer as the presence of the condition sensed for; no response (a negative response) indicates the condition is not present.

A sense code will clear the Select Receive FF. Receive or transmit must be reselected after each operation.

#### 160/160-A STATUS REQUEST

A status request external function code from the 160/160-A sets the Status Request FF in the terminal. When the subsequent input instruction is executed, the Status Enable FF sets to allow the 12-bit status response to be routed to the computer (figure 4-5).

Figure 4-5. 160/160-A Status Response

The response will consist of logical zeros, except in those bit positions which have been enabled by the set state of the Error, Fake Ready or Interrupt FFs. The response must be examined by computer program for any specific condition. Bits 2 through 10 will indicate the contents of the optional  $512_{10}$  counter.

The status request clears the Receive or Transmit FF and the operation must be reselected.

#### INTERRUPT

An interrupt code word is manually preset by the Selector switches mounted on the printed circuit card chassis (figure 4-6). If interrupt is selected and the inter-block null is detected, the Beginning of Block FF is set. If the upper 6 bits in the first word of the succeeding block agree with the predesignated interrupt word and no error is found after the redundant word is compared, the Interrupt FF will set, activating the interrupt line. If any of these conditions are not met, the Beginning of Block FF is cleared and the first word of the next block will be examined for the interrupt code word. Any other word which is the same as the interrupt code word but is not the first word of a block cannot set the Interrupt FF.

The interrupt condition, but not the selection, is cleared after either a sense code or status request.

Figure 4-6. Interrupt Logic

#### OUTPUT RESUME

When the terminal equipment has been selected to transmit, a subsequent Output Ready signal (1604/1604-A) or Information Ready (160/160-A) indicates that a word is available on the output lines. A short delay permits the output word to stabilize before sampling. This enables an  $A \rightarrow X$  transfer if the preceding word has been completely serialized, and triggers the Word Space Control, which at expiration sets the Timing Enable FF. The Sync FF then enables clock pulses to the frequency divider. Outputs from the frequency divider permit the Sample and Enable FFs to set in sequence. When the Drive Enable FF is set, the drive lines to the driver are enabled. An Output Resume is sent to the computer when the word has been serialized. The Output Resume causes the computer to drop the Output Ready, which in turn causes the terminal equipment to drop the Output Resume (figure 4-7).

The word space control delay (S18) determines the space between words and is variable at each installation. When a 160/160-A computer is at the receiving end, this delay must be switched in to prevent overrunning the computer.

Figure 4-7. Output Resume

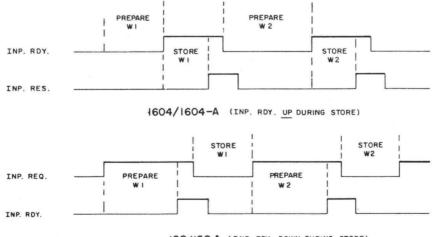

## INPUT READY/RESUME (1604/1604-A)

When the terminal equipment is selected to receive, an Input Ready signal is sent to the computer as the last bit of the redundant word is received and made available to the computer. The computer recognizes the signal, accepts the word, and responds with an Input Resume signal. The Input Resume signal clears the Input Ready FF, causing the Input Resume to drop (figure 4-8).

Figure 4-8. 1604/1604-A Input Ready/Resume

Procedural messages, when present, are always at the beginning of a block of data or in blocks preceding a block of data. Therefore, it is imperative that the computer not begin receiving elsewhere in a block. To prevent this, the Receive Selected Before Beginning of Block (RSBBB) FF is set only if there is no incoming data when receive is selected. An Input Ready signal can be sent to the computer only if this FF is set. If receive is selected while the terminal equipment is receiving, RSBBB FF will not be set until an inter-block null is recognized.

### INPUT REQUEST/READY (160/160-A)

After transfer of the first word, the Input Request signal from the 160/160-A computer and the Input Resume from the 1604/1604-A serve the same purpose (figure 4-9). As with the 1604/1604-A, the RSBBB FF prevents an Input Ready signal from being sent to the 160/160-A until the beginning of the first block received after receive is selected.

The Input Active signal permits the 160 computer to accept data faster than is possible with normal repetitive Input Request signals. The Input Active signal is not used with the 160-A. If an Input Active signal is present, words can be transferred to the computer at a maximum rate of one every 14 usec.

Figure 4-9. Input Request Ready

The 160/160-A Input Ready FF is set when the Input Request or Input Active signal is present and after bit 11 of the data word has been accepted by the A register. If the Input Active signal is up, the Input Ready FF is cleared when the null between words is recognized (figure 4-10).

If a 1604/1604-A is transmitting, the terminal equipment must be slowed down to prevent data from overrunning the 160/160-A.

160/160-A (INP. RDY. DOWN DURING STORE)

Figure 4-10. Ready/Resume Timing

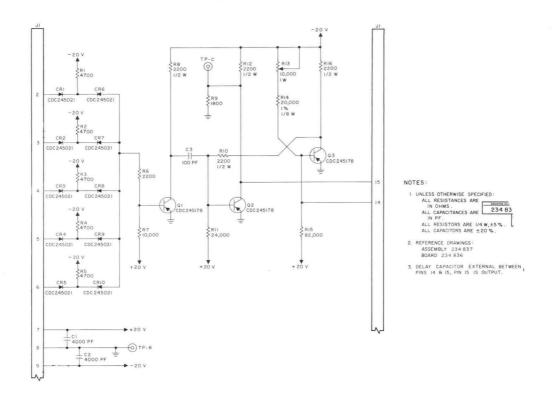

## FAKE READY TIME DELAY

The fake ready logic provides a timed wait for data after receive (input instruction) is selected. If data is not received before the timed wait period ends, the input instruction will be terminated by (1) a Disconnect signal if Disconnect on Fake (DOF) is used, or (2) repeatedly generating Fake Ready signals. The input instruction will also be terminated if the number of words received is less than the number of words requested by the computer.\*

The fake ready logic sequence is initiated when receive is selected; the sequence stops when a sense or status request is made. The status request or sense code must be executed as soon as the input is terminated. Otherwise, the Fake Ready FF may set since receive will still be selected when all words have been received.

Delay Z207 determines the time between receipt of the last word in a block of data and the setting of the Fake Ready FF. This delay is adjustable from a minimum of 100 usec. It is set after the block is terminated.

If the [block length] x [receiving word rate] is greater than the delay of V200, the delay time will elapse before the block is terminated. This will cause a fake ready even though words are still being received. The interaction of B220 and Z207 prevents this condition from arising during normal operations if Z207 is set within minimum limits. The minimum limit must allow for program execution of a status request or sense code after input termination, and for the longest possible inter-word null to be received.

The delay time of V200 is determined by doubling the inherent delay in the transmission line and adding the time required for the other computer to evaluate and acknowledge receipt of the block. The setting of the 10-position rotary switch determines the delay time of V200; a fine adjustment can be made by varying the potentiometer on the CM12 card.

<sup>\*</sup> In this instance the fake ready will cause the computer to store the contents of X (which contains the last word received) in all remaining storage addresses assigned to the block.

## MAIN TIMING

The timing circuits sequence digital information out of the X register at a constant rate during transmission. During reception they are used to assemble serial data in the A register and time the comparison of the redundant word.

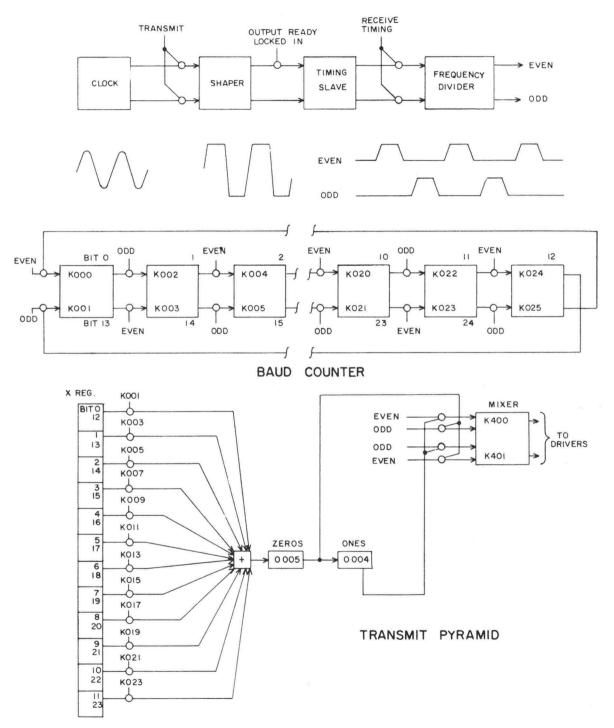

#### Transmission

Transmit timing is provided by a free running clock of a predetermined frequency. Clock output is shaped and divided by a 1:2 frequence divider. Both phases of the divider (arbitrarily called odd and even phases) are used (figure 4-11).

The baud counter is a chain of 13 FFs. The counter is started by the first even output of the frequency divider after an Output Ready signal enables the Timing Slave FF. Successive stages of the counter are set by alternating odd and even divider outputs and an enable is provided from a stage of the X register into the transmit pyramid. The 12-bit redundancy is gated out of X as each counter stage is cleared.

## Reception

The master clock is disabled during reception and timing pulses are provided by the incoming serial information. Each complete cycle received toggles the Timing Slave FF, providing an input to the frequency divider. The counter, triggered by the frequency divider, enables each of the first 12 bits received into successive stages of the A register. The counter clears by stages, enabling comparison of each bit of the redundant word with the corresponding stage of the X register. The incoming redundancy and the X register are gated to the error detector for comparison.

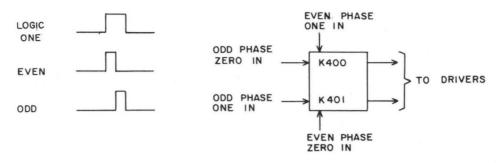

## TRANSMIT PYRAMID AND MIXER FF

The transmit pyramid is enabled by outputs from the baud counter and the X register. Each bit is made available to the pyramid for one complete clock cycle. To generate the characteristic serial waveform, the Mixer FF (figure 4-12) is forced to change state twice for each bit transmitted. This is accomplished by gating each bit with odd and even clock phases to opposite sides of the FF.

Figure 4-11. Transmission Circuits

4-16

Figure 4-12. Mixer Input

To transmit a "1", the Mixer FF will be set during the first half cell cycle and be cleared during the second half cell cycle. To transmit a "0", the FF will be cleared during the first half cell cycle and set during the second half cell cycle, as shown below.

The entire transmit function is diagrammed in figure 4-13.

## BIT AND TIMING DETECTOR

The bit and timing detector (figure 4-14) changes the incoming serial waveform to standard logic voltage levels and provides timing for word assembly and error detection.

Operation of the circuit is dependent on the first half cell cycle of every cycle. If the first half cell cycle is positive, a logical "1" is detected; if it is negative, a logical "0" is detected. In either case, the Sample-Advance FF sets (to Sample). The output of this FF triggers the Timing Slave FF and partially enables the baud counter. When the bit cycle changes direction, the Sample-Advance FF clears, advancing the baud counter. The counter enables the output of the detecting FF (set during the first half cell cycle) to the correct stage of A.

# SERIAL OUTPUT FROM MIXER

Figure 4-13. Transmit Pyramid and Output

Figure 4-14. Bit and Timing Detector

At the end of each cycle, the output of B211 clears the detecting FF. Inverter B211 has a "1" output at the end of every cycle and acts as a driven clock with speed determined by the incoming data.

An absence of data at the threshold amplifiers for a period longer than delay Z207 signals the end of a block of data or a break in communication. The latter is detected as an incomplete transmission by the computer. The delay must be set to be longer than the null between words.

## ERROR DETECTOR

Error detection is done dynamically at the receiving terminal equipment. The baud counter gates each incoming bit of the redundant word and the corresponding bit of the original word into a pyramid. If the two do not compare, the AND gate at the input to E040 or E041 will be broken, setting the Block Error FF and Word Error FF.

If the receiving terminal is connected to a 1604/1604-A computer, a word error will appear as a "1" in bit 23 position of the same storage location as the erroneous word.