21540

LACKSBURG CONTINUING EDUCATION SERIES

The Blacksburg Continuing Education Series<sup>™</sup> of books provide a laboratory — or experiment-oriented approach to electronic topics. Present and forthcoming titles in this series include the following:

- The 8080A Bugbook<sup>®</sup> : Microcomputer Interfacing and Programming

- DBUG: An 8080 Interpretive Debugger

- · Design of Op-Amp Circuits, With Experiments

- 555 Timer Applications Sourcebook, With Experiments

- Design of Active Filters, With Experiments

- 8080/8085 Software Design

- Logic & Memory Experiments Using TTL Integrated Circuits (2 Volumes)

- Design of Phase-Locked Loop Circuits, With Experiments

- Interfacing and Scientific Data Communication Experiments

- NCR Data Processing Concepts Course

- NCR Data Communications Concepts

- NCR Basic Electronics Course, With Experiments

- Introductory Experiments in Digital Electronics and 8080A Microcomputer Programming Interfacing (2 Volumes)

In most cases, these books provide both text material and experiments, which permit one to demonstrate and explore the concepts that are covered in the book. These books remain among the very few that provide step-by-step instructions concerning how to learn basic electronic concepts, wire actual circuits, test microcomputer interfaces, and program computers based upon the popular 8080-type microprocessor chip. We have found that the books are very useful to the electronic novice who desires to join the "electronics revolution," with minimum time and effort.

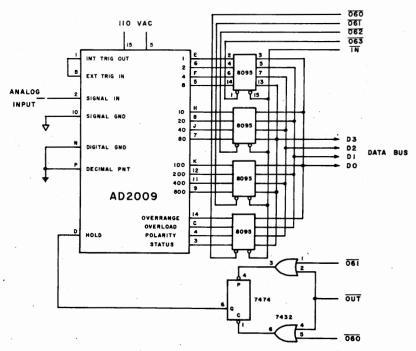

It is our pleasure to introduce this new book which covers interfacing A/D and D/A to microcomputers as well as the software that is required to control them. Complete hardware schematic diagrams and completely assembled program examples have been included. We have not tried to describe all of the analog/digital conversion techniques and how they operate, but rather we have concentrated upon the use of analog/digital converters, in small computer systems. We have chosen commercially available modules and integrated circuits for use in the examples and in the experiments. The topics of data acquisition systems, sample-and-hold devices and multiplexer circuits are also covered. The book is aimed at the microcomputer user: who is interested in interfacing his computer to "real-world" analog signals for data acquisition, control, display, plotting, etc.

Our books have been well accepted in the United States and abroad. Selected books are now being translated into German, Italian, Chinese, and Japanese. If you are interested in further details concerning these translations, contact the series editors. Both domestic and foreign short courses are available in conjunction with the Extension Division at Virginia Polytechnic Institute and State University. Plese write or call Dr. Linda Leffel, Continuing Education Center, VPI & SU, Blacksburg, VA 24061. Phone (703) 951-5241. Short courses on microcomputer interfacing and microcomputer software development are given by Tychon, Inc., Blacksburg, VA 24060. For more information on these courses, write or call Dr. Christopher Titus, at Tychon, phone (703) 951-9030.

We continue to be interested in identifying other authors who could contribute books to this series. If you have an interest in writing or publishing such a text, please contact one of the series editors.

Jonathan A. Titus, Christopher A. Titus, David G. Larsen and Peter R. Rony "The Blacksburg Group"

# Microcomputer—Analog Converter Software And Hardware Interfacing

by

Jonathan A. Titus Peter R. Rony Christopher A. Titus David G. Larsen

Originally Published as Microcomputer—Analog Converter Software and Hardware Interfacing With Experiments for 8080A/Z80/8085 Systems by E&L Instruments, Inc.

#### HOWARD W. Sams & Co., Inc. 4300 WEST 62ND ST. INDIANA POLIS, INDIANA 46268 USA

Copyright © 1978 by Jonathan A. Titus, Christopher A. Titus, Peter R. Rony, and David G. Larsen

#### FIRST EDITION FIRST PRINTING—1978

All rights reserved. Reproduction or use, without express permission, of editorial or pictorial content, in any manner, is prohibited. No patent liability is assumed with respect to the use of the information contained herein. While every precaution has been taken in the preparation of this book, the publisher assumes no responsibility for errors or omissions. Neither is any liability assumed for damages resulting from the use of the information contained herein.

International Standard Book Number: 0-672-21540-1 Library of Congress Catalog Card Number: 78-57201

Printed in the United States of America.

## Preface

Our purpose in writing this book has been to introduce you to the concepts and techniques of interfacing digital computers to analog electronic devices. Actually, the ideas presented in this book can probably be extended to interfaces and programs for many types of computers. We have concentrated upon interfacing analog-to-digital and digital-to-analog converters to an 8080/8085-based microcomputer. The designs and programs are equally applicable to all of the 8080-type microcomputers, the 8080A, 8085, Z80, etc. It has not been our purpose to detail the inner workings of the analog and digital converter modules, but rather, to treat them the way we now treat the integrated-circuit digital electronic devices such as those in the SN7400 transistor-transistor logic (TTL) family or the CD4000 complementary metal-oxide semiconductor (CMOS) family.

You will not learn how to build analog-to-digital or digital-toanalog converters in this book. We have chosen, instead, to show you how to use the modules and devices that are already commercially available. We present many examples of converter interfacing with complete hardware schematic diagrams and program listings. Perhaps one of these designs will answer one of your needs with little additional work on your part. If you require something special, we hope that you will find that the concepts presented are applicable to your work. If so, we have done our job.

We have assumed that you will be able to condition (amplify, filter, etc.) your analog signals so that they are compatible with the A/D converters that we present in the examples, and that you will be able to use the voltages that are output by the D/A converters that we have used. The topics of signal conditioning, filters, noise, ground *loops*, and *amplifiers* are beyond the scope of this book. We are looking forward to presenting these topics in future books.

If you are interested in the internal operation of A/D and D/A converters, there are two good references available which will help you understand how they work. These are:

Analog-Digital Converter Notes, D. H. Sheingold, ed., Analog Devices, Inc., Norwood, MA 02062, 1977. Data Conversion Handbook, Donald B. Bruck, Hybrid Systems Corporation, Burlington, MA 01803, 1974.

In all of the examples, we have tried to use commercially available converter modules or integrated circuits (chips). There are dozens of analog/digital module and device manufacturers, some of whom are mentioned in the following units or in the appendices. Our choices of specific manufacturers, or specific modules, were made at random, but with an eye toward presenting those modules which are easy to use and which provide a number of interfacing schemes.

The choice of specific modules does not imply our endorsement and it should not be taken to mean that these modules may necessarily be the best ones for your specific applications.

We have assumed that you have had some experience programming microcomputers at the assembly language level, and that you are familiar with the 8080's internal registers and I/O operations. Both the memory-mapped and the accumulator I/O techniques will be discussed, although we tend to favor the accumulator I/O technique because of its simplicity. You should be familiar with the use of latches at output ports, the use of three-state buffers at input ports, and the use of various decoder circuits for device address decoding. All of the examples and experiments assume the use of an 8080-based microcomputer with an uninverted, bidirectional data bus.

The program examples in the text and in the experiments are shown in the byte-per-line output that is produced by the Tychon Editor/ Assembler (TEA) that was written by Dr. Christopher A. Titus. We find that it is much easier to read and interpret than the instruction-per-line outputs of other assemblers. Although we favor the octal numbering system, along with the Heath Company and others, the TEA program can also provide a hexadecimal format. Write to Chris if you would like more information about TEA.

We have found wide acceptance of our books in formal classes as well as by individual users, worldwide. Selected books are being translated into German, Japanese, French, Italian, Chinese and Malaysian. If you are interested in further details concerning these translations, or in translating the books into other languages, please contact us. The Blacksburg Continuing Education Series<sup>™</sup> continues to expand with additional titles being added in the past few months. A list of the current series is given inside the front cover of this book. We continue to be interested in identifying and working with authors who think that their book ideas would fit into the Blacksburg Continuing Education Series. If you have an idea that you are interested in working on, please contact us here in Blacksburg.

Many of the concepts that are presented in this book have been incorporated into the material taught at seminars that are presented by Tychon here in Blacksburg. Three courses are currently being taught: Microprocessor Interfacing (628), Introduction to Assembly Language Programming for 8080/8085 Processors (685), and Intermediate Assembly Language Programming for 8080/8085 Processors (687). If you are interested in these courses, write to The Course Director, Tychon, Inc., Box 242, Blacksburg, VA 24060. Courses are also provided through the Center for Continuing Education and the Extension Division at Virginia Polytechnic Institute and State University, Blacksburg, VA. Call Dr. Linda Leffel at (703) 951-6208 for further information.

We have received assistance from a number of companies that have provided information, technical assistance, and permission to reproduce information from their data sheets and books. We would like to acknowledge the assistance of ADAC Corporation, Analog Devices, Inc., Burr-Brown Research Corporation, Data Translation, Inc., Datel Systems, Inc., National Semiconductor Corporation, Signetics Corporation, and Siliconix.

We also greatly appreciate the efforts of Mr. Murray Gallant, president of E&L Instruments, Inc., and his continuing support in this writing.

#### JONATHAN A. TITUS, CHRISTOPHER A. TITUS, PETER R. RONY, AND DAVID G. LARSEN

### Contents

#### UNIT 1

#### INTERFACING DIGITAL-TO-ANALOG CONVERTERS

Introduction to this Unit — Objectives — D/A Converter Outputs — Generating Analog Outputs — Generating a Voltage Ramp — Complex Ramp Outputs — Triangular Wave Outputs — Square Waves and Other Outputs — Data Displays and Outputs — High Speed CRT Displays With D/A Converters — Interfacing a 10-Bit D/A Converter — Memory-Mapped I/O Techniques and D/A Converters — Other Digital-to-Analog Converters

#### UNIT 2

#### INTERFACING ANALOG-TO-DIGITAL CONVERTERS

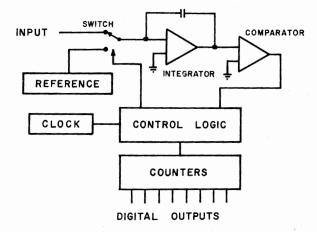

Introduction to This Unit — Objectives — Analog-to-Digital Converters — Software A/D Conversion Techniques — Interfacing A/D Converter Modules — Using A/D Converters for Data Acquisition — Data-Acquisition Timing — Using the Data — Closing the Loop-Control Applications

#### UNIT 3

####

Introduction to this Unit — Dual-Slope Analog-to-Digital Converters — Digital Panel Meters — Binary-Coded-Decimal Numbering — Digital Panel Meter Considerations — Digital Panel Meter Interfacing — Handling BCD Data — Decimal-Point Detection — Message Software — Software Modifications 9

47

#### UNIT 4

####

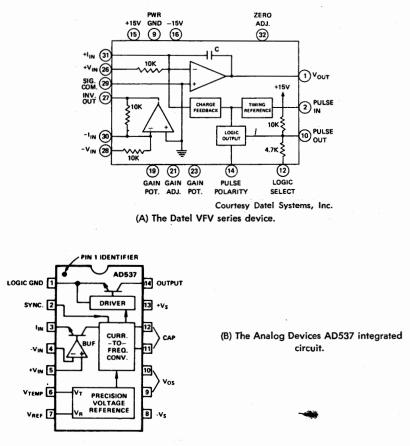

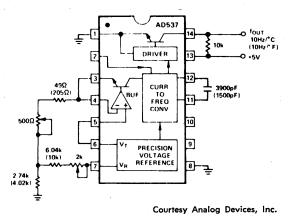

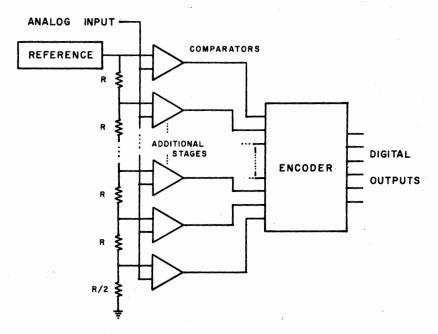

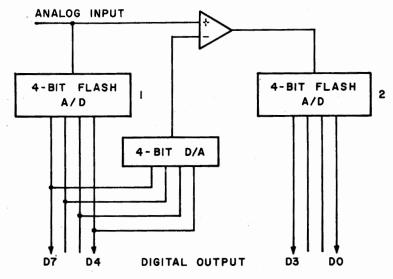

Introduction to This Unit — Voltage-to-Frequency Converters — Flash Converters

#### UNIT 5

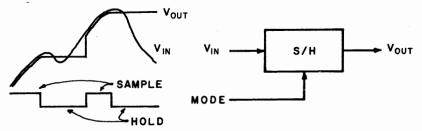

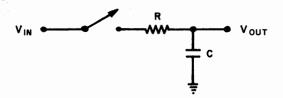

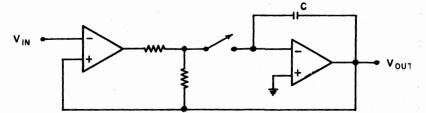

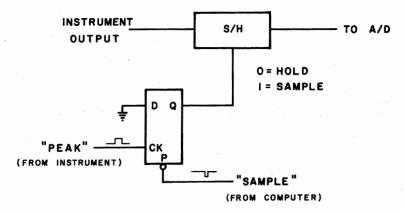

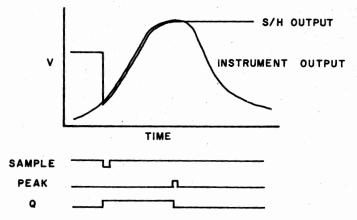

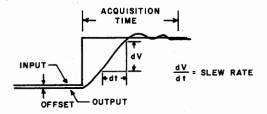

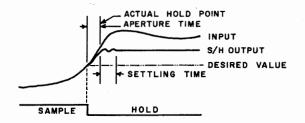

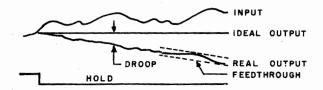

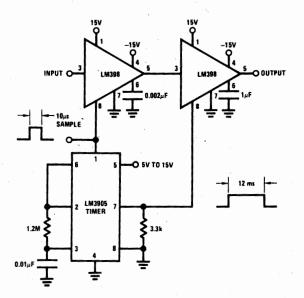

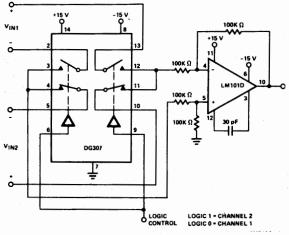

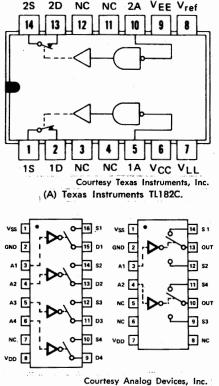

#### SAMPLE-AND-HOLD CIRCUITS AND MULTIPLEXER DEVICES . . . 125

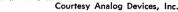

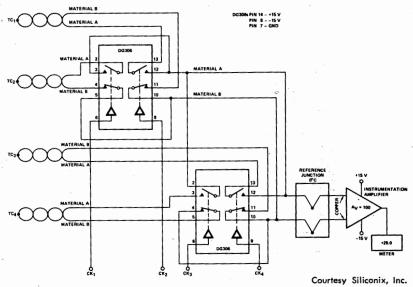

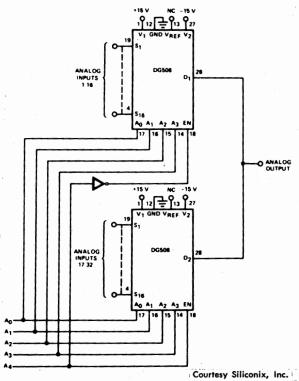

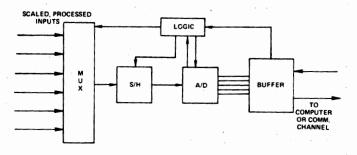

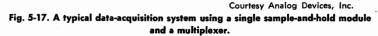

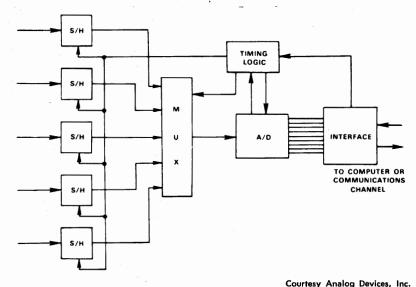

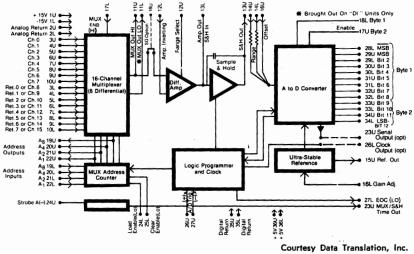

Introduction to This Unit — Sample-and-Hold Circuits — Using Sample-and-Hold Devices — Multiplexers — Semiconductor Analog Multiplexer Considerations — Miltiplexer Signal Inputs — Multiplexer Applications — Multiplexer Interfacing — Multiplexers and Sample-and-Hold Systems — Signal Processing — References

#### UNIT 6

####

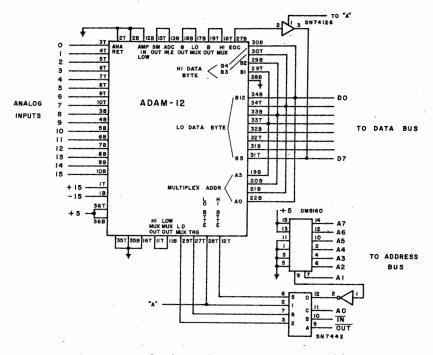

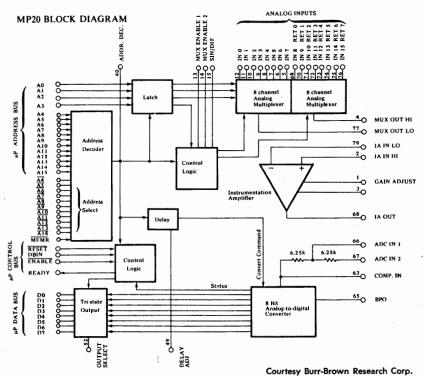

Introduction to this Unit — Black Boxes-Data-Acquisition Modules —Data-Acquisition Software — Other Data-Acquisition Modules —Boards: Plug-In Analog-Input and Output — Bits . . . and Things

#### UNIT 7

####

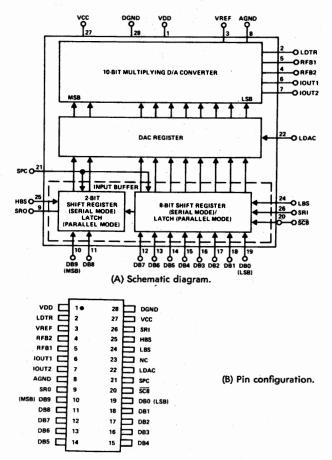

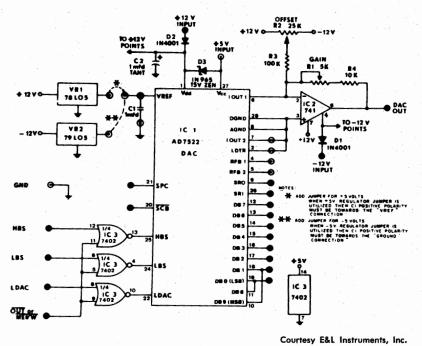

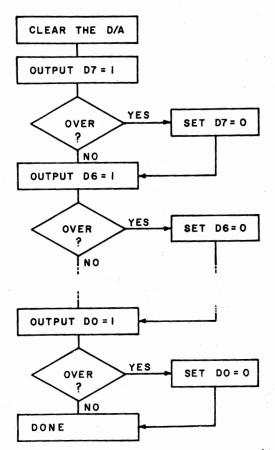

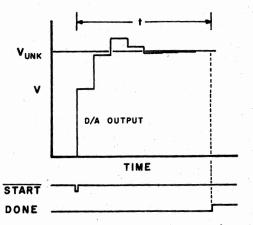

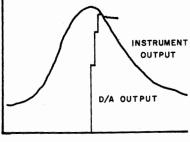

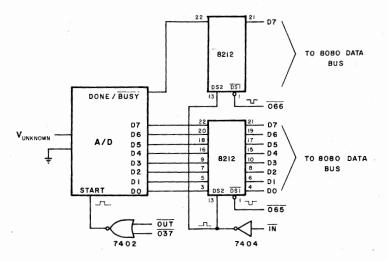

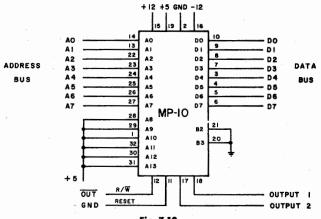

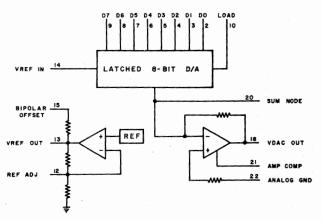

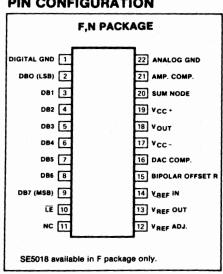

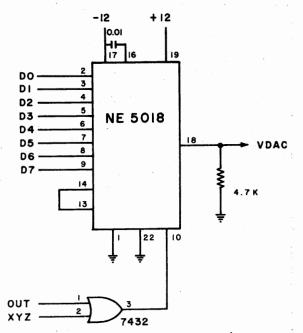

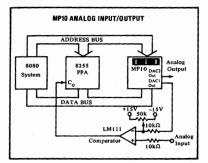

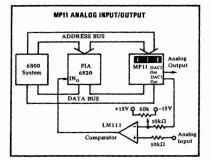

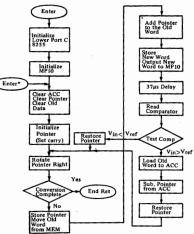

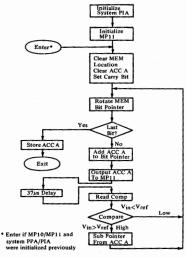

Introduction to the Experiments — Interfacing a 10-Bit Digital-to-Analog Converter — Complex Digital-to-Analog Converter Outputs — Software-Controlled Ramp A/D Converter — A Software-Controlled Successive-Approximation A/D Converter — A Small Data-Acquisition System — Gate Threshold Measurements Using a D/A Converter — Using Two 8-Bit D/A Converters; the Burr-Brown MP-10 Module — Using Two D/A Converters for a Y vs. T Display — Using Two D/A Converters for an X vs. Y Display — Part Requirements for the Experiments

APPENDIX A.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

<td

## Interfacing Digital-to-Analog Converters

#### INTRODUCTION TO THIS UNIT

Most digital-to-analog converters (DACs or D/A converters) may be considered to be voltage or current output devices. The output is in direct proportion to the value of the digital input, generally in binary form. In this unit you will see how digital-to-analog converters are interfaced to microcomputers and some of the uses to which the analog outputs may be put. The D/A converters are treated as modules and we will consider ourselves to be ignorant of their internal operation. Understanding how the converters actually work may be important, but we do not believe that it will greatly increase your interfacing and software development skills.

#### OBJECTIVES

At the end of this unit you will be able to do the following:

- Calculate the step-voltage for any *n*-bit D/A converter having an output range of x volts.

- Describe the operation of a simple 8-bit D/A converter interface.

- Describe how D/A converters may be used to generate the following types of output:

Q

Positive and negative ramps (sawtooths)

#### Triangular waves Square waves Complex waveforms

- Design an interface for a double-buffered, 10-bit D/A converter.

- Write software to control two D/A converters for an X vs. Y display of a data file.

Most digital-to-analog converters (DACs or D/A converters) provide an analog output that is proportional to some type of digital input. Typical digital inputs are in binary code and each individual input may have only one of two values, a logic 1 or a logic 0. If we consider a 4-bit D/A converter with input bits A, B, C and D, which have binary weights of 1, 2, 4 and 8, respectively, we find that there are 16 possible states from  $0000_2$  to  $1111_2$ , inclusive. Let us assume that each binary input will contribute a voltage to the total which is proportional to its binary weight. The easiest voltages to use in this example are A = 1 volt, B = 2 volts, C = 4 volts and D = 8 volts. If a binary 0 is present in a particular column, the corresponding voltage is not added to the total. If a binary 1 is present, then the voltage is added to the total.

In this 4-bit D/A converter the voltage range will be from zero volts to 15 volts, as shown in Table 1-1.

|       | Binary Co | ode Input |       | Output Voltage |

|-------|-----------|-----------|-------|----------------|

| D = 8 | C = 4     | B = 2     | A = 1 | (Volts)        |

| 0     | 0         | 0         | · 0 · | 0              |

| 0     | 0         | 0         | 1     | 1              |

| 0     | 0         | 1         | 0     | 2              |

| 0     | 0         | 1         | 1 -   | 3              |

| 0     | 1         | 0         | 0     | 4              |

| 0     | 1         | 0         | 1     | 5              |

| 0     | · 1       | 1         | 0     | 6              |

| 0     | 1         | 1         | 1 .   | 7              |

| 1     | 0         | 0         | 0     | 8              |

| ו     | · 0       | 0         | 1     | 9              |

| 1     | 0         | 1         | 0     | 10             |

| 1     | 0         | T         | 1     | 11             |

| 1     | 1         | 0         | 0     | 12             |

| 1     | 1         | 0         | 1     | 13             |

| 1     | 1         | 1         | 0     | 14             |

| · · 1 | 1         | 1 1       | 1     | 15             |

Table 1-1. Four-Bit D/A Converter With Voltage Range From 0 Volts to 15 Volts

Most real D/A converters use a series of resistors in an R, 2R, 4R, 8R, etc., binary weighted combination or in an R-2R ladder-type

network. The ladder network of R and 2R values is preferred because of the ease of manufacture and improved electrical characteristics. The voltages are switches electronically, but a discussion of how this is done is beyond our scope. Current-output D/A converters are also available, their general advantage being fast settling time, generally a few hundred nanoseconds. For a further discussion of D/A converters and factors such as *linearity*, offset, and resolution we recommend the references mentioned in the introduction. These and other technical terms are defined in Appendix 1.

Digital-to-analog converters usually have transistor-transistor logic (TTL) compatible inputs which make them very easy to interface to the standard 7400-series logic and most microprocessor or microcomputer intergrated circuits. Some of the newer D/A converters are available with complementary metal-oxide-semiconductor (CMOS) or emitter-coupled-logic (ECL) compatible inputs. Although straightbinary coded D/A converters will be used in all of our examples and in the experiments, converters do come with other types of coded inputs. The types generally available are:

- Two's Complement

- Complementary Binary

- Complementary Offset Binary

- Offset Binary

- Binary Coded Decimal (BCD)

These codes may be useful in some applications but we have found that the binary-coded converters are the ones most widely used in microcomputer interfacing. Voltage outputs of 0–10 volts, 0–5 volts,  $\pm 2.5$  volts,  $\pm 5$  volts and  $\pm 10$  volts are common. In short, the variety of D/A converters is so great that you can probably find one that will answer your specific needs. For nonstandard ranges, an operational amplifier with the necessary gain may be used to "customize" the output voltage to your needs. Few people design and build their own D/A converters because of the wide variety available. Converters with digital inputs of 8, 10, 12 and 14 binary bits are common with prices ranging from about \$15 to several hundred dollars.

#### **D/A CONVERTER OUTPUTS**

When a parallel digital input is presented to a D/A converter, the converter will respond by outputting a corresponding voltage that is proportional to the value of the digital input. How can we determine what the output voltage will be for a given *n*-bit D/A converter with a range of x volts?

We will start by using a D/A converter with eight inputs coded in straight binary and with an output voltage range of 0 to 1 volt. The

Table 1-2. Output Voltages for Various Binary Inputs on a 0- to 1-Volt Scale D/A Converter

| Binary Input                          | Output Voltage (Volts) |

|---------------------------------------|------------------------|

| . 00000000                            | 0.00390625             |

| 00000001                              | 0.00781250             |

| 00000010                              | 0.01171875             |

| 00000011                              | 0.01562500             |

| 00000100                              | 0.01953125             |

|                                       |                        |

| · · · · · · · · · · · · · · · · · · · |                        |

| 11111011                              | 0.98046875             |

| 11111100                              | 0.98437500             |

| 11111101                              | 0.98828125             |

| 1111110                               | 0.99218750             |

| 1111111                               | 0.99609375             |

eight bits, n, provide 256 values from 0 to 255. The output can be divided into 256 individual steps of 0.00390 volt, or 3.9 millivolts per step. We can now determine the voltage output by the D/A converter for any input value, X:

$V_{out} = Output Voltage = (1-volt full scale) \cdot (X/256)$ or the following formula may be used:

$V_{out} = Output Voltage = (X steps) \cdot (0.00390 volt/step)$

Some of the output voltages by the 0- to 1-volt full scale D/A converter are shown in Table 1-2.

It is important to note that while the D/A converter used in this example has a specified range from 0 to 1 volt, the analog output does not actually reach one volt. The reason for this becomes apparent if we examine the "weights" or voltages assigned to each of the eight bits. Since we are using the binary numbering system, each bit is an integral power of two. Thus when we go from the most significant bit (MSB), or the left-most bit, to the least significant bit (LSB), or the right-most bit, each bit position will have a weight that is one-half that of its left neighbor and twice that of its right neighbor.

Let us now consider the actual voltage weights assigned to the bits:

| Full-Scale Voltage = $1$ Volt |                              |      |  |  |  |

|-------------------------------|------------------------------|------|--|--|--|

| Least Significant Bit         | $0.00390625 = \frac{1}{256}$ | volt |  |  |  |

| -                             | $0.00781250 = \frac{1}{128}$ | volt |  |  |  |

|                               | $0.01562500 = \frac{1}{64}$  | volt |  |  |  |

|                               | $0.03125000 = \frac{1}{32}$  | volt |  |  |  |

|                               | $0.06250000 = \frac{1}{16}$  | volt |  |  |  |

|                               | $0.12500000 = \frac{1}{8}$   | volt |  |  |  |

| ,                             | $0.25000000 = \frac{1}{4}$   | volt |  |  |  |

| Most Significant Bit          | $0.5000000 = \frac{1}{2}$    | volt |  |  |  |

#### GENERATING ANALOG OUTPUTS

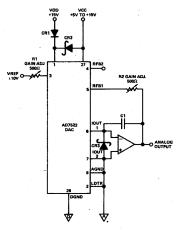

The D/A converter modules will quickly convert the binary value applied at the inputs to a voltage, but these inputs must be maintained for as long as the output voltage is required. If we attempt to interface a D/A converter to a microcomputer system simply by connecting the 8-bit data bus to the eight D/A converter inputs, we would observe a constantly changing voltage output by the D/A converter. The various output voltages would be caused by the many different 8-bit values presented to the D/A converter's inputs as the microcomputer uses the bus to transfer data and instructions. It is not only necessary to present the data to the D/A converter's inputs, but it must also be held or captured for as long as it is needed. A simple latch circuit may be used to capture the data from the data source, usually the microcomputer's data bus. Digital-to-analog converters generally require little more than latches and device decoding circuitry, plus the converter itself, for a complete interface.

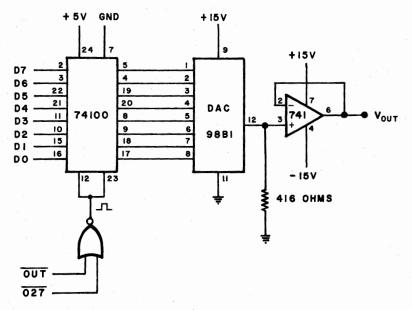

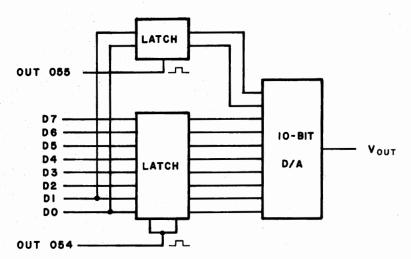

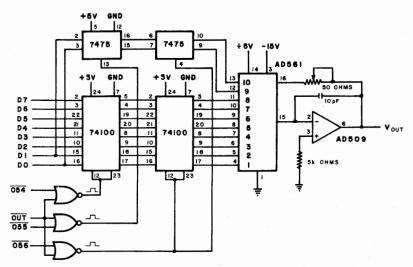

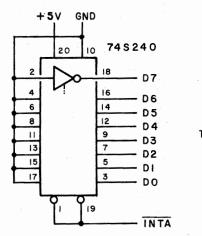

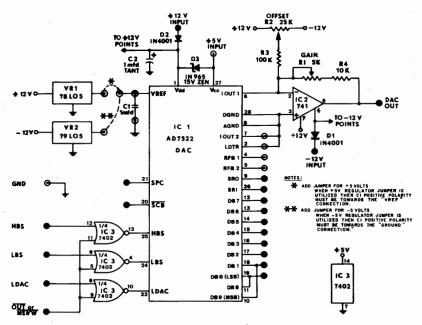

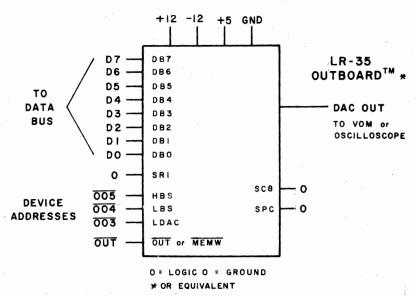

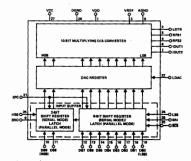

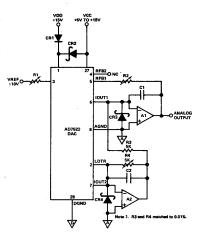

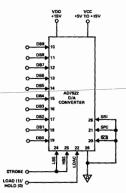

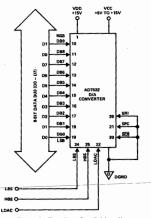

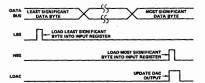

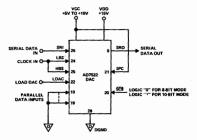

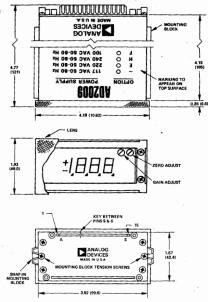

Fig. 1-1. Interfacing a Datel DAC-98BI D/A converter to an 8080-based microcomputer using a latch circuit.

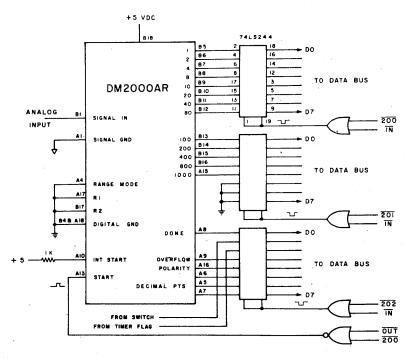

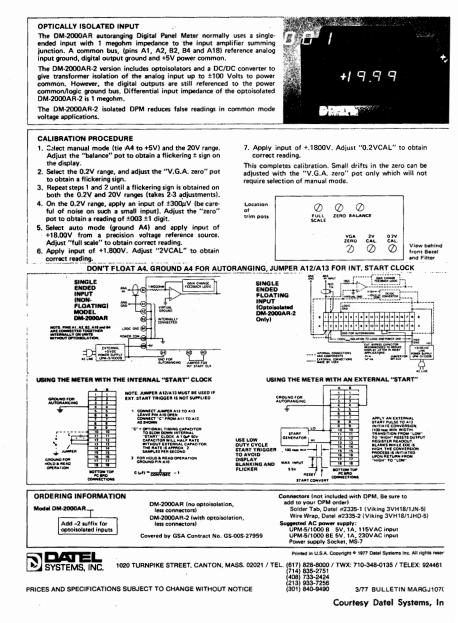

A typical D/A converter interface is shown in Fig. 1-1. A Datel Systems, Incorporated DAC-98BI module is used as the 8-bit D/A converter. The DAC-89BI has a current output, so circuitry has been added to provide a 0- to 1-volt output range.

For more information about device decoding and device addressing such as that used in Fig. 1-1 to activate the latch, we refer you to Introductory Experiments in Digital Electronics and 8080A Microcomputer Programming and Interfacing, Book 2, Unit No. 17.

There are many uses for the analog outputs generated by computers using circuits similar to the one shown in Fig. 1-1. Some of these are listed below:

- Drive a servo motor

- Drive a strip-chart recorder

- · Control a voltage-to-frequency converter

- Control a programmable power supply

- Drive an analog meter

In some applications, it is necessary to produce a linearly increasing voltage ramp to be used to control a test process, move a recorder pen, or move an oscilloscope beam. In the following example we will use the D/A converter to generate a linear ramp.

#### GENERATING A VOLTAGE RAMP

The voltage ramp output by a D/A converter is probably the simplest output that may be generated using fairly simple software. Even with a limited number of 8080 instructions in your software vocabulary, you can probably suggest a method of generating the linearly increasing binary values which are to be output to the D/A converter. In this example we will use the D/A converter which has been interfaced to the 8080-based computer, as shown in Fig. 1-1. An OUT 027 instruction transfers the contents of the 8080's A register to the D/A converter's latch circuit.

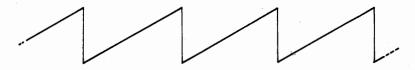

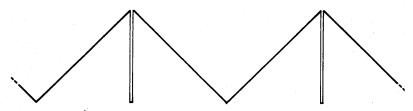

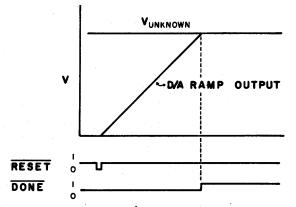

One of the easiest techniques that we can use to generate a ramp output uses one of the register increment instructions. A typical ramp is shown in Fig. 1-2.

Fig. 1-2. Typical ramp waveform.

By incrementing the value in one of the 8080's registers and then latching it in the D/A converter's latch circuit, the 256 steps may be generated in about 3.2 milliseconds (this assumes an 8080 clock rate of 500 nanoseconds). The time period of each ramp and thus the slope may be slowed down by introducing a time delay subrou-

tine into the ramp generation software. The software in Example 1-1 shows the steps necessary to generate the ramp, while the software in Example 1-2 shows how a time delay may be introduced by using a call to a time delay subroutine. The time delay subroutine may be a series of no-operation instructions (NOPs) or it may be a more complex, programmable time delay, which may answer many needs. In this second example, a general-purpose time delay subroutine has been written and assembled.

| 003         000         074           003         001         323           003         002         027           003         003         303           003         004         000           003         005         003                                                                                                                                                                                               |                | *003 000<br>INRA<br>OUT<br>027                            | 1-1<br>SOFTWARE FOR A POSITIVE RAMP OUTPUT<br>/INCREMENT THE CONTENTS OF A<br>/OUTPUT IT TO THE DAC<br>/DAC'S DEVICE CODE<br>/KEEP DOING IT AGAIN AND AGAIN |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                         |                | /EXAMPLE<br>/POSITIVE                                     | 1-2<br>RAMP OUTPUT SOFTWARE WITH TIME DELAY                                                                                                                 |

| 003         000         061           003         001         377           003         002         003           003         003         074           003         004         323           003         005         027           003         006         315           003         007         014           003         011         303           003         012         003           003         013         003 |                | *003 000<br>LXISP<br>377<br>003                           | LOAD A STACK ADDRESS SO THAT SUBROUTINES<br>/MAY BE USED<br>/INCREMENT A<br>/OUTPUT IT TO DAC<br>/CALL THE TIME DELAY SUBROUTINE<br>/DO IT AGAIN            |

|                                                                                                                                                                                                                                                                                                                                                                                                                         |                | /THIS IS T                                                | HE DELAY SUBROUTINE                                                                                                                                         |

| 003014365003015325003016021003017065003020001003021033                                                                                                                                                                                                                                                                                                                                                                  | DELAY,<br>DEC, | PUSHD<br>LXID<br>065                                      | /SAVE REG A & FLAGS<br>/SAVE D&E<br>/LOAD THE TIMING BYTES<br>/065 TO REGISTER E<br>/001 TO REGISTER D<br>/DECREMENT REG PAIR D                             |

| 003         022         172           003         023         263           003         024         302           003         025         021           003         026         003           003         027         321           003         030         361           003         031         311                                                                                                                   |                | MOVAD<br>ORAE<br>JNZ<br>DEC<br>0<br>POPD<br>POPPSW<br>RET | /IF D OR E IS NON-ZERO, WE<br>/DECREMENT THE PAIR AGAIN<br>/ GET REG VALUES BACK<br>/RESTORE A & FLAGS, TOO<br>/RETURN                                      |

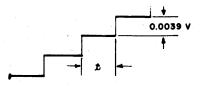

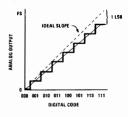

Fig. 1-3. Expanded linear output of D/A voltage converter.

It is important to remember that the D/A converter is still generating discreet voltage step outputs of 0.0039 volt, so that when the linear output is expanded it appears as shown in Fig. 1-3.

The time period, t, depends upon how fast we want to have the computer output the analog information. The time delay subroutine shown in Example 1-2 could be used to increase the time period, t, to several seconds. Filtering or integrating the voltage may be useful if the step function is not acceptable and a more linear output is necessary. In most applications, the output is left unfiltered, although amplification may be used to increase the range to 0 to 10 volts or perhaps to a range of 0 to 2.35 volts for a specific application.

In some applications, a negative ramp may be needed that decreases from a high potential to a low potential. This may be accomplished by adding an inverting, unity-gain amplifier and some additional components to the D/A converter interface, thus providing a hardware solution. In our case, it is more reasonable, however, to change the software to decrement the register, thus causing the output to the D/A converter to decrease in value. This is the software solution. The software for the negative ramp is shown in Example 1-3.

|             |        | /EXAMPLE<br>/TYPICAL | 1-3<br>SOFTWARE FOR A NEGATIVE RAMP OUTPUT |

|-------------|--------|----------------------|--------------------------------------------|

|             |        | *003 000             |                                            |

| 003 000 075 | START, | DCRA                 | DECREMENT THE CONTENTS OF A                |

| 003 001 323 |        | OUT                  | OUTPUT IT TO THE DAC                       |

| 003 002 027 |        | 027                  |                                            |

| 003 003 303 |        | JMP                  | KEEP GOING                                 |

| 003 004 000 |        | START                |                                            |

| 003 005 003 |        | 0                    |                                            |

Of course, the additional call to the time delay subroutine could have been added, but we have not shown it in this example.

You should note that when one of the 8080's 8-bit, internal registers contains 377, or  $1111111_2$ , and is incremented, it becomes 000, or  $0000000_2$ . Thus, the largest value becomes the smallest value in one step to start the ramp at the "bottom" again. Likewise, when 000, or  $00000000_2$ , is decremented it becomes 377, or 11111111, the smallest value becoming the largest value, again in a single step. No additional software is necessary to reinitialize the register to these starting values.

#### COMPLEX RAMP OUTPUTS

There may be applications in which a complete sweep, *i.e.*, from minimum to maximum value, of the ramp's output is not needed. For example, suppose that we have interfaced a D/A converter to our computer and that the converter's output ranges from 0 to 10 volts full scale. Our application requires that the output sweep between a specific low voltage limit and a specific high voltage limit. In this example, we will set the lower limit at 2.0 volts and the higher limit at 8.0 volts. Using the full 0- to 10-volt range, we could use operational amplifiers to attenuate the output range and to offset it, too. We will use software instead.

This is a typical "hardware/software tradeoff." If an operational amplifier scheme is used, more hardware is added to the system and it becomes more difficult to change the high and low limits than if software is used. The hardware solution still has merit, though, since it will compress the 256 voltage points into smaller increments when output through the added operational amplifiers. This means that the 2.0- to 8.0-volt range will be divided into 256 points or steps. The software solution will result in the usual 0.0039 volt steps for a 0- to 1-volt D/A converter or 0.039 volt steps for a 0- to 10-volt D/A converter.

The first task in solving this problem is to determine the binary values of the limiting voltages. This may be done empirically by breadboarding a D/A converter and slowly increasing the binary inputs and noting their values when the D/A converter's output reaches 2.0 and 8.0 volts. The limits may also be calculated as follows:

# $\frac{10 \text{ Volts Full Scale Output}}{256 \text{ Steps}} = 0.0390 \text{ volt/step}$

and

# $\frac{2.0 \text{ Volts}}{0.0390 \text{ volt/step}} = 51.3 \text{ steps}$

It is, of course, impossible to have fractional steps. The only steps that are allowed are those with integral values between 0 and 255. We must decide if we want the lower limit to be 51 steps (1.989 volts) or 52 steps (2.028 volts). In this case the 1.989-volt value is acceptable as the lower limit. In a similar way we determine that the upper voltage limit is represented by 205 steps.

The software shown in Example 1-4 will start at the lower limit and increase the voltage output by the D/A converter to the upper limit of 8.0 volts in discrete 39-millivolt steps.

| Table 1-3.         | Upper and   | d Lower Vo | Itage Limits | and   |

|--------------------|-------------|------------|--------------|-------|

| <b>Their Binar</b> | y, Octal, a | nd Hexade  | cimal Equiva | lents |

|     | Ve      | oltage  | S                               | teps   | Binary           | Octal       | Hex     |

|-----|---------|---------|---------------------------------|--------|------------------|-------------|---------|

|     | 2.0     | (1.989) |                                 | 51     | 00110011         | 063         | 33      |

|     | 8.0     | (7.995) | 1                               | 205    | 11001101         | 315         | CD      |

|     |         |         | /EXAMPLE<br>/RAMP O<br>*003 000 |        | VITH UPPER & LC  | WER LIMITS  |         |

| 003 | 000 076 | START,  | MVIA                            | /LOAD  | REG A WITH ST    | ARTING VALU | E       |

|     | 001 063 |         | 063                             |        | = 051 DECIMAL    |             | -       |

| 003 | 002 323 | LOOP,   | OUT                             | /OUTP  | UT IT TO THE DA  | C           |         |

| 003 | 003 027 | ,       | 027                             |        |                  |             |         |

| 003 | 004 074 | l .     | INRA                            | /INCRE | MENT THE VALU    | E           |         |

| 003 | 005 000 | )       | NOP                             | /THREE | NOP'S LEFT FOR   | ADDITION O  | F       |

| 003 | 006 000 |         | NOP                             | /A CA  | LL TO A TIME DE  | LAY         |         |

| 003 | 007 000 | )       | NOP                             |        |                  |             |         |

|     | 010 376 |         | CPI                             |        | ARE THE VALUE    |             | R LIMIT |

|     | 011 315 |         | 315                             |        | = 205 DECIMAL :  |             |         |

|     | 012 302 |         | JNZ                             | /IF NC | T EQUAL, DO TH   | IE LOOP AGA | IN I    |

|     | 013 002 |         | LOOP                            |        |                  |             |         |

|     | 014 003 |         | 0                               |        |                  |             |         |

|     | 015 303 |         | JMP                             | •      | UAL, REINITIALIZ | E AND DO IT |         |

|     | 016 000 |         | START                           | /AGAII | N                |             |         |

| 003 | 017 003 |         | 0                               |        |                  |             |         |

The software shown in Example 1-4 will cause the D/A converter to output a maximum voltage which is within 39 millivolts of the upper limit. This occurs since the comparison between the limit value and the actual register value is performed after the register is incremented, but before the value is output to the D/A converter. If the D/A converter's output is to actually reach the upper limit, the comparison value must be changed from 315 to 316.

This simple program may be used to cycle a ramp between any two voltages that are within the range of the D/A converter's output voltage. The ramp may also be a negative-going one by using the decrement instruction, comparing the register value to the lower limit and when it is reached, resetting the register to the upper limit.

The slope of the output is determined by the time required for the computer to execute all of the instructions. Three no-operation instructions (NOP=000) are provided in Example 1-4 so that a call to a time delay subroutine may be inserted. For optimum speed, the NOPs should be removed and the program condensed.

The time delay subroutine could be a more complex program than a simple time delay loop. A flag, interrupt, or other stimulus could govern whether or not the computer proceeds to the next step. Software could also be added to wait for an external event to take place before starting another ramp cycle.

#### TRIANGULAR WAVE OUTPUT

The previous software examples for ramp generation could serve as the basis for additional software which permits the D/A converter to generate a triangular wave output. In this example, a complete 0- to 10-volt full scale triangular wave output will be assumed. The first attempt at a program that will output this type of a waveform is shown in Example 1-5.

|      |     | 257<br>074 |       | /EXAMPLE<br>/TRIANGUI<br>*003 000<br>XRAA<br>INRA | LAR WAVE OUTPUT PROGRAM #1<br>/CLEAR REG A |

|------|-----|------------|-------|---------------------------------------------------|--------------------------------------------|

| 003  | 002 | 323        |       | OUT                                               | OUTPUT IT TO THE DAC                       |

| 003  | 003 | 027        |       | 027                                               |                                            |

| ·003 | 004 | 302        |       | JNZ                                               | /IF STILL NON-ZERO, KEEP GOING             |

| 003  | 005 | 001        |       | UP                                                |                                            |

| 003  | 006 | 003        |       | 0                                                 |                                            |

| 003  | 007 | 075        | DOWN, | DCRA                                              | DECREMENT REG A                            |

| 003  | 010 | 323        |       | OUT                                               | OUTPUT IT TO THE DAC                       |

| 003  | 011 | 027        |       | 027                                               |                                            |

| 003  | 012 | 302        |       | JNZ                                               | /IS IT = 0?                                |

| 003  | 013 | 007        |       | DOWN                                              | NO, GO DOWN ONE MORE                       |

| 003  | 014 | 003        |       | 0                                                 |                                            |

| 003  | 015 | 303        |       | JWb                                               | YES, START UP AGAIN                        |

| 003  | 016 | 001        |       | UP                                                |                                            |

| 003  | 017 | 003        |       | 0                                                 |                                            |

If we attempt to run this program, a "glitch" is observed at the apex of the triangle. The glitch is caused by the program. After incrementing the count register to its maximum value of 377, the software must again increment it to 000 and output it to the D/A converter before the JNZ instruction is used to test the value.

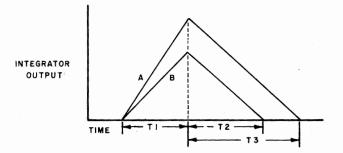

When the value 000 is reached, the JNZ instruction is "ignored" and the DOWN section starts its execution. The illustration in Fig. 1-4 shows what the D/A converter's output would look like when executing the software from Example 1-5. These examples assume an ideal output from the D/A converter.

The glitch may be removed by simply reversing the position of the INRA and the OUT 027 instructions. The modified software, shown in Example 1-6, will produce a reasonable triangular wave output. This new program, Triangular Wave Output Program #2, now checks the incremented value prior to the output instruction, pre-

Fig. 1-4. D/A converter output when software from Example 1-5 is executed.

venting the output of the sequence of values 377, 000, 377 generated in the first program, Example 1-5.

|                    | /EXAMPLE 1-0<br>/TRIANGULAR | 5<br>R WAVE OUTPUT PROGRAM #2 |

|--------------------|-----------------------------|-------------------------------|

|                    | *003 000                    |                               |

| 003 000 257        | XRAA                        | CLEAR REG A                   |

| 003 001 323        | UP, OUT                     | OUTPUT VALUE IN REG A TO DAC  |

| 003 002 027        | 027                         |                               |

| 003 003 074        | INRA                        | /INCREMENT REG A              |

| 003 004 302        | JNZ                         | /IF NOT ZERO, GO UP AGAIN     |

| 003 005 001        | UP                          |                               |

| 003 006 003        | 0                           |                               |

| 003 007 075        | DOWN, DCRA                  | DECREMENT REG A               |

| 003 010 323        | OUT                         | OUTPUT IT TO THE DAC          |

| 003 011 027        | 027                         |                               |

| 003 012 302        | JNZ                         | /IF NOT ZERO, GO DOWN AGAIN   |

| <b>DO3 013 007</b> | DOWN                        |                               |

| 003 014 003        | 0                           |                               |

| 003 015 303        | JWb                         | /IF ZERO, GO UP               |

| 003 016 001        | UP                          |                               |

| 003 017 003        | 0                           |                               |

|                    |                             |                               |

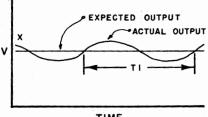

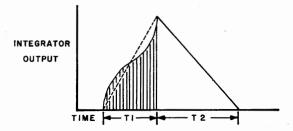

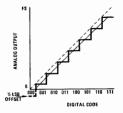

There is, however, another problem with this second program. The high value of 377 and the low value of 000 are both output to the D/A converter twice in succession, giving the triangular output a plateau at the high and low points. These plateaus, illustrated in Fig. 1-5, are twice as long as the other voltage steps generated by the software.

This problem, too, is caused by the software. After the value 377 is output to the D/A converter by the OUT 027 instruction in the UP software loop, the accumulator, or A register, is incremented to 000, checked by the JNZ instruction and then decremented back to 377. This value is then output in the DOWN section of the program. Thus, the value 377 has been output to the D/A converter twice. Clearly some modification must be made in the software to correct this.

The software shown in Example 1-7 has some additional increment and decrement instructions to eliminate the "double output" of the values 377 and 000. This program provides "glitchless" output

Fig. 1-5. Triangular output with high and low plateaus.

of a triangular wave. It should be noted that there are probably a number of other software solutions to this problem.

|             |       | /EXAMPLE<br>/TRIANGU | 1-7<br>LAR WAVE OUTPUT PROGRAM #3 |

|-------------|-------|----------------------|-----------------------------------|

|             |       | *003 000             |                                   |

| 003 000 323 | UP,   | OUT                  | OUTPUT REG A TO DAC               |

| 003 001 027 |       | 027                  |                                   |

| 003 002 074 |       | INRA                 | INCREMENT REG A                   |

| 003 003 302 |       | JNZ                  | /IF NOT ZERO, GO UP AGAIN         |

| 003 004 000 |       | UP                   |                                   |

| 003 005 003 |       | 0                    |                                   |

| 003 006 075 |       | DCRA                 | /IF ZERO, DECREMENT IT TO 377     |

| 003 007 075 | DOWN, | DCRA                 | DECREMENT IT AGAIN                |

| 003 010 323 |       | OUT                  | OUTPUT IT TO DAC                  |

| 003 011 027 |       | 027                  |                                   |

| 003 012 302 |       | JNZ                  | /IF NOT ZERO, GO DOWN AGAIN       |

| 003 013 007 |       | DOWN                 |                                   |

| 003 014 003 |       | 0                    |                                   |

| 003 015 074 |       | INRA                 | /IF ZERO, INCREMENT IT TO 001     |

| 003 016 303 |       | JWb                  | GO BACK UP AGAIN                  |

| 003 017 000 |       | UP                   |                                   |

| 003 020 003 |       | 0                    |                                   |

The triangular wave output by the software shown in Example 1-7 has equal positive and negative ramp periods since the two software loops, UP and DOWN, contain the same number of instructions with equal execution times. For nonsymmetrical outputs where slopes are to be different, NOP instructions or calls to time delay subroutines could be easily added to the program. For example, if 11 NOP instructions are added to the DOWN loop between the OUT 027 and the JNZ instruction, the ratio of positive ramp period to negative ramp period is approximately 3 to 7.

#### SQUARE WAVES AND OTHER OUTPUTS

Square waves are generated easily by using a D/A converter and software to alternate between a low and a high voltage. The periods and frequencies may be determined in the software with either NOP

instructions or calls to time delay subroutines. A typical example of a square wave output program is shown in Example 1-8.

|             |        | /EXAMPLE<br>/TYPICAL | 1-8<br>SQUARE WAVE OUTPUT PROGRAM |

|-------------|--------|----------------------|-----------------------------------|

|             |        | *003 000             |                                   |

| 003 000 076 | START, | MVIA                 | LOAD REG A WITH LOWER LIMIT       |

| 003 001 023 |        | 023                  |                                   |

| 003 002 323 |        | OUT                  | OUTPUT IT TO THE DAC              |

| 003 003 027 |        | 027                  |                                   |

| 003 004 315 |        | CALL                 | DO A TIME DELAY ROUTINE           |

| 003 005 021 |        | DELAY                |                                   |

| 003 006 003 |        | 0                    |                                   |

| 003 007 076 |        | MVIA                 | LOAD REG A WITH UPPER LIMIT       |

| 003 010 307 |        | 307                  |                                   |

| 003 011 323 |        | OUT                  | OUTPUT IT TO THE DAC              |

| 003 012 027 |        | 027                  |                                   |

| 003 013 315 |        | CALL                 | DO ANOTHER DELAY LIKE THE ONE     |

| 003 014 021 |        | DELAY                | SHOWN IN EXAMPLE 1-2              |

| 003 015 003 |        | 0                    |                                   |

| 003 016 303 |        | JMP                  | DO IT AGAIN                       |

| 003 017 000 |        | START                |                                   |

| 003 020 003 |        | 0                    |                                   |

| 003 021 000 | DELAY, | 0                    | /DELAY SUBROUTINE IS LOCATED HERE |

By changing the software to use two different time delay sub routines, rectangular wave outputs may be generated. Pulses may also be generated by using a very short time delay program for the pulse and a much longer time delay program for the interval between pulses Depending upon the frequency of the 8080 microprocessor chip's crystal clock, very short pulses may be generated. Example 1-9 shows the software which may be used to generate a 20-microsecond-long 10-volt pulse with a repetition rate of about 10 milliseconds.

|     |     |     |       | /EXAMPLE<br>/TYPICAL | 1-9<br>PULSE OUTPUT PROGRAM USING A DAC |

|-----|-----|-----|-------|----------------------|-----------------------------------------|

|     |     |     |       | *003 000             |                                         |

| 003 | 000 | 076 | LOOP, | MVIA                 | LOAD REG A WITH HIGHEST VALUE           |

| 003 | 001 | 377 |       | 377                  |                                         |

| 003 | 002 | 323 |       | OUT                  | OUTPUT IT TO THE DAC                    |

| 003 | 003 | 027 |       | 027                  |                                         |

| 003 | 004 | 076 |       | MVIA                 | LOAD REG A WITH LOWEST VALUE            |

| 003 | 005 | 000 |       | 000                  |                                         |

| 003 | 006 | 323 |       | OUT                  | OUTPUT IT TO THE DAC                    |

| 003 | 007 | 027 |       | 027                  |                                         |

| 003 | 010 | 315 |       | CALL                 | CALL A DELAY ROUTINE                    |

| 003 | 011 | 016 |       | DELAY                |                                         |

| 003 | 012 | 003 |       | 0                    |                                         |

| 003 | 013 | 303 |       | JMP                  | GO BACK AND DO IT AGAIN                 |

|     |     |     |       |                      |                                         |

003

014

000

LOOP

003

015

003

0

003

016

000

DELAY, 0

/10 MILLISECOND DELAY MAY BE PLACED

003

017

000

0

/HERE, SEE EXAMPLE 1-2.

Complex waveforms may be generated by treating the square wave, the triangular wave and the ramp output software as subroutines. Linking these subroutines together with a series of call instructions and perhaps calls to time delay subroutines will produce complex outputs. These outputs are generally difficult to generate with standard test equipment and they may be useful for testing or cycling power supplies, electromechanical devices, etc. While the output may be slow, since it is limited by the execution speed of the 8080's instructions, it would be difficult to generate these complex outputs in other ways.

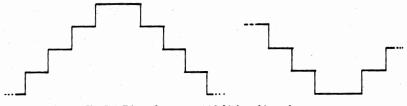

#### DATA DISPLAYS AND OUTPUTS

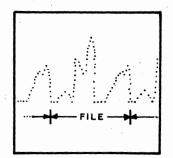

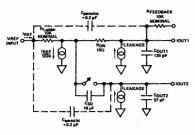

Many applications require that the computer be used to output a file of data for later evaluation. The data can take two forms: a list or numeric printout of the data or a graphic representation presented on a chart, drawing, etc. In many cases it will be much easier to distinguish trends and changes in the values that have been stored in the computer if the graphical output is chosen. The graph may be output to an oscilloscope, an X-Y plotter, or a strip-chart recorder. The example in Fig. 1-6 illustrates the difference between the numeric output and the graphic output.

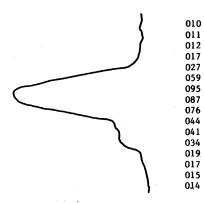

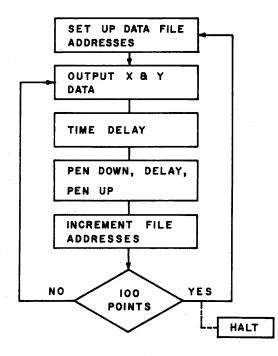

Our next task will be to develop a program to output some data in graphic form. A file of 8-bit binary words or bytes will be set up in the computer's memory between addresses 007 000 and 007 143, inclusive. This will provide us with  $100_{10}$  points to display in some way. A strip-chart recorder is available which is compatible with the voltage output of the 8-bit D/A converter previously interfaced to our 8080 microcomputer. The data points are to be output once and since the computer will be able to output all 100 data points much faster than the strip-chart's servo motor can respond, a delay of 100 milliseconds will be inserted into the software between the output of each point. The output of all 100 points will take 10 seconds.

To use a file of data stored in the 8080's memory, address pointers must be set up in the H and L registers (register pair H) to provide the 16-bit address necessary to point to locations 007 000 through 007 143. We will also need to have access to a subroutine that provides the 100 millisecond delay. Although important in some applications, we will ignore the time necessary to actually get the data from the memory and output it to the D/A converter. This will cause the

Fig. 1-6. Difference between numeric output and graphic output.

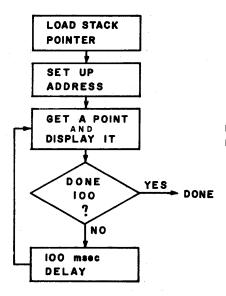

*real time* between points to be somewhat longer than 100 milliseconds, but by a negligible amount. A counter register is also needed to keep track of the number of points that have been output so that the program will stop when all 100 of the points have been plotted. Since subroutines are to be used, a stack area must be set up in read/write memory. It is a good idea to locate the stack in an area of read/write memory distant from that used for program and data storage. A flow-chart of the 100-point output software is provided in Fig. 1-7.

The software for the 100-point plot program is provided in Example 1-10 in its fully assembled form:

Fig. 1-7. Flowchart for a 100-point data display program or plotting program that uses an 8-bit D/A converter.

|     |     |     |         | ,        | 1-10<br>IDRED POINT DISPLAY SOFTWARE  |

|-----|-----|-----|---------|----------|---------------------------------------|

| 003 | 000 | 061 |         | *003 000 | LOAD A STACK POINTER                  |

|     | 001 |     |         | 377      | ,                                     |

| 003 | 002 | 003 |         | 003      |                                       |

| 003 | 003 | 041 | DISPLA, | LXIH     | LOAD A POINT COUNT                    |

| 003 | 004 | 000 |         | DATA1    | OF THE DATA STORAGE AREA              |

| 003 | 005 | 007 |         | 0        |                                       |

| 003 | 006 | 006 |         | MVIB     | LOAD A POINT COUNT                    |

| 003 | 007 | 144 |         | 144      | /144 = 100  DECIMAL                   |

| 003 | 010 | 176 | LOOP,   | MOVAM    |                                       |

| 003 | 011 | 323 |         | OUT      | OUTPUT IT                             |

| 003 | 012 | 027 |         | 027      |                                       |

| 003 | 013 | 043 |         | INXH     | /INCR THE ADDR                        |

| 003 | 014 | 005 |         | DCRB     | DECREMENT POINT COUNT                 |

|     | 015 |     |         | JZ       | /IF DONE, GET OUT OF THE LOOP         |

|     | 016 |     |         | DONE     |                                       |

|     | 017 |     |         | 0        |                                       |

|     | 020 |     |         | CALL     | /IF NOT DONE, DO A 100-MILLI-         |

|     | 021 |     |         | HUNMIL   | SECOND DELAY                          |

|     | 022 |     |         | 0        |                                       |

|     | 023 |     |         | JMP      | DO THE NEXT POINT                     |

|     | 024 |     |         | LOOP     |                                       |

| 003 | 025 | 003 |         | 0        |                                       |

| 003 | 026 | 166 | DONE,   | HLT      | WHEN FINISHED DISPLAYING, HALT        |

| 003 | 027 | 000 | HUNMIL, | 0        | /100 MSEC DELAY SOFTWARE MAY BE ADDED |

| 003 | 030 | 000 |         | 0        | HERE. SEE EXAMPLE 1-2 FOR A TYPICAL   |

| 003 | 031 | 000 |         | 0        | TIME DELAY SUBROUTINE                 |

|     |     |     |         | *007 000 |                                       |

| 007 | 000 | 000 | DATA1,  | 0        | DATA STARTS HERE FOR 100 ADDRESSES    |

|     |     |     |         |          |                                       |

This program will output the 100-point data file in approximately 10 seconds, or 0.1 seconds per point. The 8080's B register or any other unused register may be used to count the 100 points, but is this really necessary? We certainly need a counter, but the L register is already being used as a counter since it is incremented in each loop through the software. It will increase from 000 to 143 during the course of the program.

The L register may be used to perform two tasks: (1) to provide the low address of the data points and (2) to provide an increasing point count. By comparing the value contained in the L register to  $144_8$  we can determine when the file output has been completed. Remember that the 8080's comparison instructions do not alter either of the two data bytes being compared.

In this example, the contents of the L register will be transferred to the A register and then compared to a data byte in a compareimmediate (CPI) instruction. There is no need to transfer the value in the A register back to the L register since the data is *copied* during register-register transfers.

In the software in Example 1-11, the L register is used as the counter and as the low address value, thus permitting us to save the **B** register for future use.

|             |     |     |         |        | 1-11<br>D 100-POINT DISPLAY SOFTWARE<br>ONLY THE MAIN PROGRAM |

|-------------|-----|-----|---------|--------|---------------------------------------------------------------|

| 003         | 000 | 061 |         | LXISP  |                                                               |

| 003         | 001 | 377 |         | 377    |                                                               |

| 003         | 002 | 003 |         | 003    |                                                               |

| 003         | 003 | 041 | DISPLA, | LXIH   |                                                               |

| <b>0</b> 03 | 004 | 000 |         | DATA1  |                                                               |

| 003         | 005 | 007 |         | 0      |                                                               |

| 003         | 006 | 176 | LOOP,   | MOVAM  |                                                               |

| 003         | 007 | 323 |         | OUT    |                                                               |

| 003         | 010 | 027 |         | 027    |                                                               |

| 003         | 011 | 043 |         | INXH   | INCREMENT MEMORY ADDRESS                                      |

| 003         | 012 | 175 |         | MOVAL  | /MOVE CONTENTS OF REG L TO REG A                              |

| 003         | 013 | 376 |         | CPI    | COMPARE IT TO                                                 |

| 003         | 014 | 144 |         | 144    | /144 = 100  DECIMAL                                           |

| 003         | 015 | 312 |         | JZ     | /IF ALL POINTS DISPLAYED                                      |

| 003         | 016 | 026 |         | DONE   | /WE'RE DONE                                                   |

| 003         | 017 | 003 |         | 0      |                                                               |

| 003         | 020 | 315 |         | CALL   |                                                               |

| 003         | 021 | 027 |         | HUNMIL |                                                               |

| 003         | 022 | 003 |         | 0      |                                                               |

| 003         | 023 | 303 |         | JWb    |                                                               |

| 003         | 024 | 006 |         | LOOP   |                                                               |

| 003         | 025 | 003 |         | 0      |                                                               |

#### HIGH SPEED CRT DISPLAYS WITH D/A CONVERTERS

In the previous example, the data stored in the 100-point, 8-bit data file was output only once, at low speed. There are many applications where we may wish to output the data very quickly and often more than a single time. This is the case when a cathode ray tube or oscilloscope is to be used to display the data.

By removing the three-byte call to the 100-millisecond time delay subroutine in the strip-chart output program, Example 1-11, the 100point data file could be output once, very quickly, perhaps to a storage oscilloscope. If, however, a normal oscilloscope is the only type available, the computer will have to be set up to output the data points again and again so that the display will be maintained.

Instead of jumping to the address labeled DONE in the strip-chart software, Examples 1-10 and 1-11, the computer must be reprogrammed to repeatedly display the complete 100-point data file. This

may be done by having the computer jump back to that point in the program at which the address of the data file is loaded into register pair H. This is shown in Example 1-12 in which the time delay subroutine call has been removed.

|                     |          | 1-12<br>IDRED POINT DISPLAY SOFTWARE FOR HIGH<br>SPLAY DEVICES |

|---------------------|----------|----------------------------------------------------------------|

|                     | *003 000 |                                                                |

| 003 000 061         | LXISP    | LOAD A STACK POINTER                                           |

| 003 001 377         | 377      |                                                                |

| 003 002 003         | 003      |                                                                |

| 003 003 041 DISPLA, | LXIH     | LOAD THE DATA ADDRESS                                          |

| 003 004 000         | DATAI    |                                                                |

| 003 005 007         | 0        |                                                                |

| 003 006 176 LOOP,   | MOVAM    | GET AN 8-BIT DATA POINT                                        |

| 003 007 323         | OUT      | OUTPUT IT TO THE DAC                                           |

| 003 010 027         | 027      |                                                                |

| 003 011 043         | INXH     | /INCR MEMORY ADDRESS                                           |

| 003 012 175         | MOVAL    | /MOVE L TO A                                                   |

| 003 013 376         | CPI      | COMPARE IT TO 100 DECIMAL                                      |

| 003 014 144         | 144      |                                                                |

| 003 015 302         | JNZ      | / IF NOT EQUAL, DO IT AGAIN                                    |

| 003 016 006         | LOOP     |                                                                |

| 003 017 003         | 0        |                                                                |

| 003 020 303         | JMP      | /IF DONE, REINITIALIZE AND                                     |

| 003 021 003         | DISPLA   | START IT AGAIN                                                 |

| 003 022 003         | 0        |                                                                |

This program will display the 100 points in the data file again and again to provide a display which might look like this:

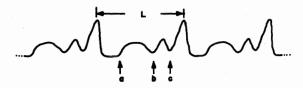

When the data file is being displayed it is difficult to determine where the 100-point data file starts and where it ends. We can probably assume that the file's length is L, since this is the distance between repetitive features being displayed. The length might be more properly called the period, T, or  $\Delta T$ , since it is a time period which is being measured on the oscilloscope. The top of the peak is probably not the start of the data file; the file might start at points a, b or c.

Most data files will be discontinuous enough at their beginning and end so that the displayed file will not run together, but this possibility exists and it must be considered. Some method of defining the start of the data file is required. The first point in the file could be preset to a known value, say, 377, but this wastes one of the points and it may be "lost" in among the other data values in the file. An easy way to overcome this problem is to have the computer generate an output which may be used to trigger the oscilloscope. It could also be used on a second trace, if one is available on the oscilloscope, to identify the file's starting point. The output command could be inserted at the start of the DISPLAY software as shown in Example 1-13.

|     |     |      |         | /EXAMPLE<br>/GENERATI<br>/SOFTWAR | NG A TRIGGER PULSE IN THE DISPLAY |  |

|-----|-----|------|---------|-----------------------------------|-----------------------------------|--|

|     |     |      |         | *003 000                          |                                   |  |

| 003 | 000 | .061 |         | LXISP                             | LOAD A STACK POINTER              |  |

| 003 | 001 | 377  |         | 377                               |                                   |  |

| 003 | 002 | 003  |         | 003                               |                                   |  |

| 003 | 003 | 041  | DISPLA, | LXIH                              | LOAD THE DATA ADDRESS             |  |

| 003 | 004 | 000  |         | DATA1                             |                                   |  |

| 003 | 005 | 007  |         | 0                                 |                                   |  |

| 003 | 006 | 323  |         | OUT                               | GENERATE A TRIGGER PULSE AT THE   |  |

| 003 | 007 | 030  |         | 030                               | START OF THE FILE                 |  |

| 003 | 010 | 176  | LOOP,   | MOVAM                             | GET AN 8-BIT DATA POINT           |  |

|     |     |      |         |                                   |                                   |  |

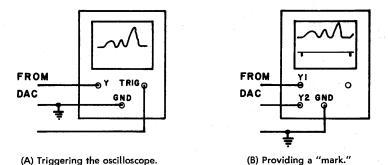

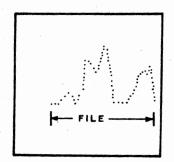

The OUT 030 pulse is used to trigger the oscilloscope or to provide a "mark" at the start of the file (Fig. 1-8).

Fig. 1-8. OUT 030 pulse is used to trigger the oscilloscope or to provide a "mark" at the start of a file.

These techniques for the display of the data in the file rely upon the oscilloscope's time base or the strip-chart's motor to generate the time axis for the data output. This is accomplished by either moving the oscilloscope's electron beam or the strip-chart's paper at a fixed, known rate. A second D/A converter could also be used to provide the time base or X-axis information.

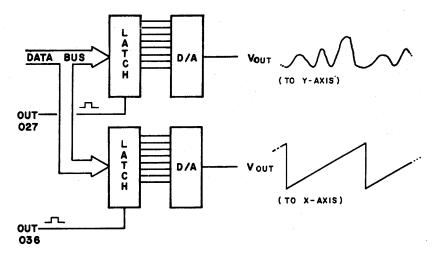

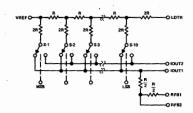

The second D/A converter could be used to generate the ramp potential to move the oscilloscope's electron beam by using the software shown in Example 1-1. Using two D/A converters to provide computer controlled output of both data and time-base information provides what is called an X-Y or X vs. Y display since the computer can control each axis independent of the other (Fig. 1-9).

The software must now include program steps to generate the ramp as well as to output the data. For 100 data points, the X or time-axis D/A converter will only have a range of 100/256th of its full scale range since only the first 100 voltage steps will be output. This limitation is overcome by using the oscilloscope's gain controls to expand the X-axis to fill the screen. The software which controls the X-Y display of data is provided in Example 1-14.

/EXAMPLE 1-14

/SOFTWARE FOR RAMP AND DATA OUTPUT USING A /DUAL D/A CONVERTER INTERFACE

| 000 |

|-----|

| C ( |

|     |         |         | .003 000    |                                       |

|-----|---------|---------|-------------|---------------------------------------|

|     | 000 00  |         | MVIB<br>000 | SET UP A REGISTER FOR THE RAMP VALUES |

|     |         |         |             | ALL THE DATA ADDRESS                  |

|     | 002 04  |         | LXIH        | SET UP THE DATA ADDRESS               |

|     | 003 00  |         | DATAI       |                                       |

|     | 004 00  |         | 0           |                                       |

| 003 | 005 00  | 4 LOOP, | INRB        | /INCREMENT RAMP DATA                  |

| 003 | 006 17  | 0       | MOVAB       | MOVE RAMP DATA TO REG A               |

| 003 | 007 32  | 3       | OUT         | OUTPUT IT TO X-AXIS DAC               |

| 003 | 010 03  | 6       | 036         |                                       |

| 003 | 011 17  | 6       | MOVAM       | GET THE FIRST DATA POINT              |

| 003 | 012 32  | 3       | OUT         | OUTPUT IT TO Y-AXIS DAC               |

| 003 | 013 02  | 7       | 027         |                                       |

| 003 | 014 04  | 3       | INXH        | /INCREMENT MEMORY ADDRESS             |

| 003 | 015 17  | 5       | MOVAL       | MOVE L TO A                           |

|     | 016 37  |         | CPI         | COMPARE IT TO 100 DECIMAL             |

|     | 017 14  |         | 144         |                                       |

|     | 020 30  | -       | JNZ         | /IF NOT ZERO, GET ANOTHER POINT       |

|     | 021 00  |         | LOOP        | AND DISPLAY IT                        |

|     | 022 00  | -       | 0           | AND DISPLAT IT                        |

|     | 023 30  |         | JMP         | ALL 100 DOINTS OUTDUT SO DE           |

|     |         |         |             | ALL 100 POINTS OUTPUT, SO RE-         |

|     | 024 00  |         | DISPLA      | REINITIALIZE AND DO IT AGAIN          |

| 003 | 025 00  | 3       | 0           |                                       |

|     |         |         | *007 000    |                                       |

| 007 | 000 000 | DATAI,  | 0           | DATA STARTS HERE AND GOES FOR 100     |

| 007 | 001 00  | 0       | 0           | POINTS                                |

|     |         |         | -           | ,                                     |

Each time that the computer goes through the software loop, the value in the B register is incremented and output as the time-base or X-axis data. This software may work fairly well, but upon close examination there may be streaks of light on the oscilloscope's screen. These streaks of light are caused by the short time that that each point

Fig. 1-9. Using two 8-bit D/A converters to generate X- and Y-axis voltages for plotting or graphic display.

is displayed in relation to the time that the oscilloscope spends in moving the electron beam to the next point's position. We may need to introduce a short time delay into the software, perhaps between the OUT and the INXH instructions, so that the beam will stop and "intensify" each point. This time delay might be a few NOP instructions or an actual call to a time delay subroutine.

This program is interesting since the value in the B register and the value in the L register will always be equal. In a previous example we saw that the value in the L register could be used as both a counter and as a memory address. In this case the value in the L register may be used as the memory address and as the value for the X-axis D/A converter. This eliminates the use of register B.

Even if the data field is offset or biased to have a starting address of 007 100, the value in the L register may still be used simply by subtracting (or adding) the offset prior to the use of the value as the data to be output to the X-axis D/A converter. This mode of operation is shown in Example 1-15.

|     |     |     |         |          | E FOR | AN X-Y DAC DISPLAY OF DATA WHERE<br>ADDRESS ALSO GENERATES A RAMP |

|-----|-----|-----|---------|----------|-------|-------------------------------------------------------------------|

|     |     |     |         | *003 000 |       |                                                                   |

| 003 | 000 | 061 |         | LXISP    | /SET  | UP A STACK                                                        |

| 003 | 001 | 377 |         | 377      |       |                                                                   |

| 003 | 002 | 003 |         | 003      |       |                                                                   |

| 003 | 003 | 041 | DISPLA, | LXIH     | /SET  | UP NEW ADDRESS POINTERS                                           |

| 003 | 004 | 100 |         | NEWPNT   |       |                                                                   |