# The Minicomputer in On-Line Systems

# WINTHROP COMPUTER SYSTEMS SERIES

Gerald M. Weinberg, editor

# MOSTELLER

Systems Programmer's Problem Solver

# HEALEY AND HEBDITCH

The Minicomputer in On-Line Systems

## CONWAY, GRIES, AND ZIMMERMAN

A Primer on PASCAL, 2nd ed.

# **BASSO AND SCHWARTZ**

Programming with FORTRAN/WATFOR/WATFIV

#### SHNEIDERMAN

Software Psychology: Human Factors in Computer and Information Systems

# **GRAYBEAL AND POOCH**

Simulation: Principles and Methods

# WALKER

Problems for Computer Solutions Using FORTRAN

# WALKER

Problems for Computer Solutions Using BASIC

### CHATTERGY AND POOCH

Top-down, Modular Programming in FORTRAN with WATFIV

## LINES AND BOEING

**Minicomputer** Systems

# GREENFIELD

Architecture of Microcomputers

# NAHIGIAN AND HODGES

Computer Games for Businesses, Schools, and Homes

## MONRO

Basic BASIC

# **CONWAY AND GRIES**

An Introduction to Programming: A Structured Approach Using PL/I and PL/C, 3rd ed.

## CONSTABLE AND O'DONNELL

A Programming Logic

# CRIPPS

An Introduction to Computer Hardware

# COATS AND PARKIN

Computer Models in the Social Sciences

# EASLEY

Primer for Small Systems Management

# CONWAY

A Primer on Disciplined Programming Using PL/I, PL/CS and PL/CT

### **FINKENAUR**

COBOL for Students: A Programming Primer

# WEINBERG, WRIGHT, KAUFFMAN, AND GOETZ

High Level Cobol Programming

# **CONWAY AND GRIES**

Primer on Structured Programming Using PL/I, PL/C, and PL/CT

## **GILB AND WEINBERG**

Humanized Input: Techniques for Reliable Keyed Input

# The Minicomputer in On-Line Systems

Small Computers in Terminal-Based Systems and Distributed Processing Networks

> Martin Healey David Hebditch

Winthrop Publishers, Inc., Cambridge, Massachusetts

# Library of Congress Cataloging in Publication Data

Healey, Martin. The minicomputer in on-line systems.

Includes index. 1. Minicomputers. 2. On-line data processing. 3. Electronic data processing—Distributed processing. I. Hebditch, David Leroy. II. Title. QA76.5.H444 001.64 81-589 IBSN 0-87626-579-4 AACR2

© 1981 by Winthrop Publishers, Inc. 17 Dunster Street Cambridge, Massachusetts 02138

All rights reserved. No part of this book may be reproduced in any form or by any means without permission in writing from the publisher.

Printed in the United States of America.

10 9 8 7 6 5 4 3 2 1

To Jill

# Contents

Foreword xi

Preface xvii

# 1. The Role of the Minicomputer in Data Communication and Distributed Processing Systems

Some Typical Systems 1 Why Use a Mini? 10 Problem Areas 13 References 13

# 2. The Minicomputer: Technology and Architecture

What Is a Minicomputer? 15 Architecture 19 Bus Structures 22 Instruction Sets 25 Memory Addressing 30 Input/Output 32 Memory Management and Protection 38 Hardware Enhancements 44 Microprogramming 52 Microelectronics in the Computer Industry 54 Peripherals and Interfaces 69 15

1

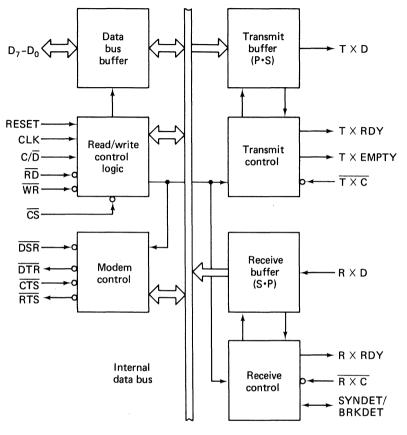

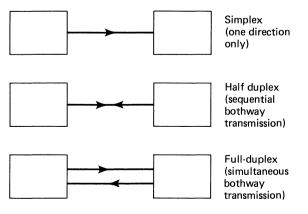

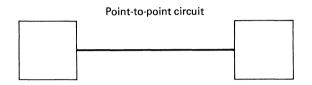

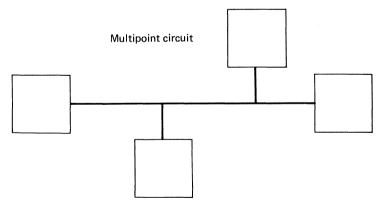

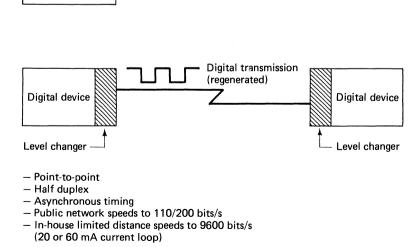

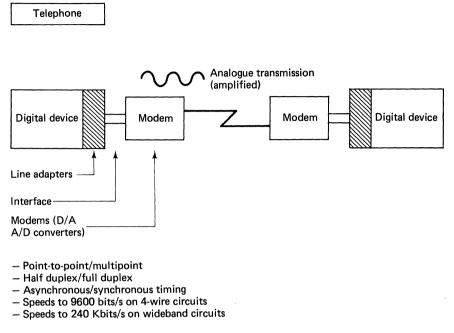

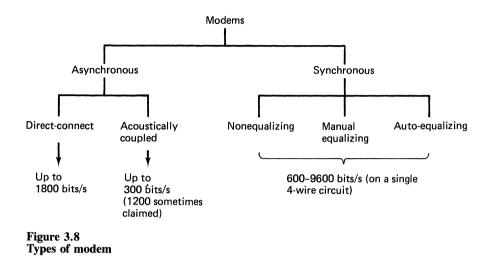

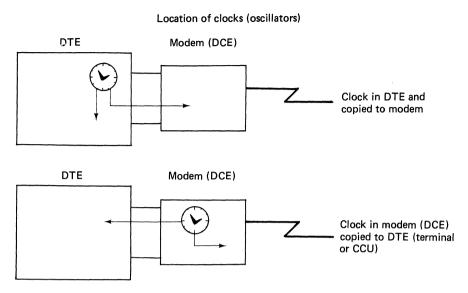

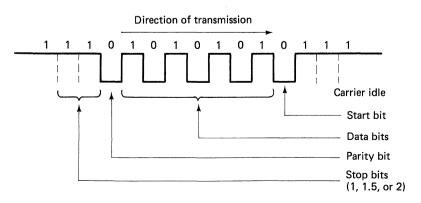

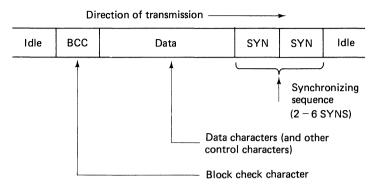

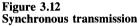

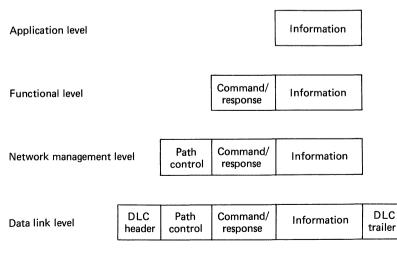

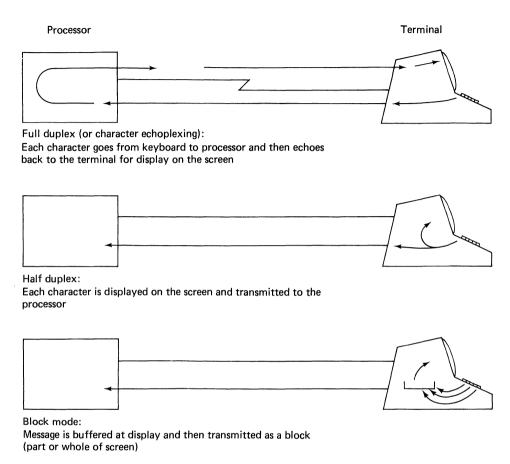

#### **Data Transmission and Terminals** 3.

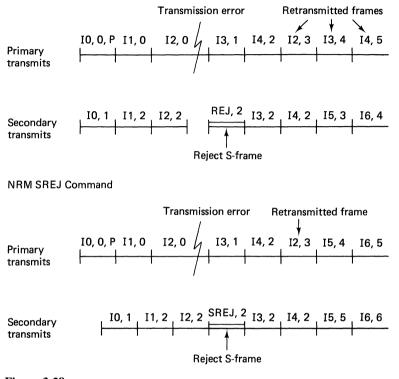

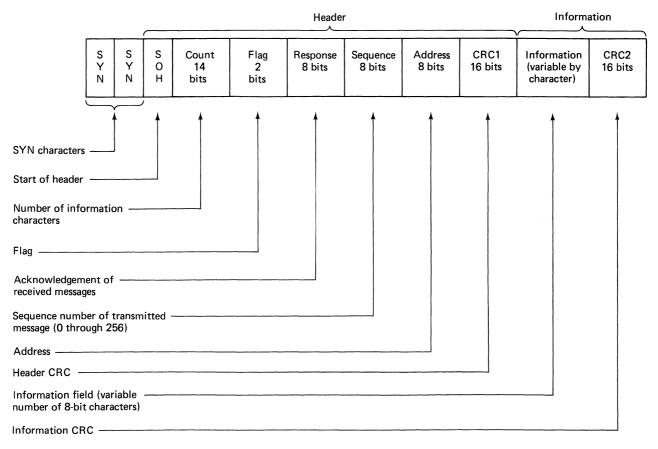

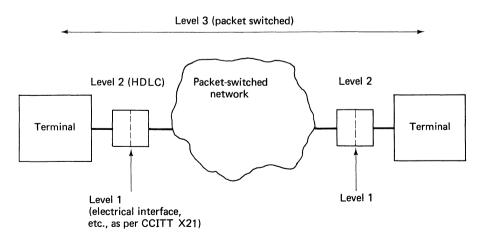

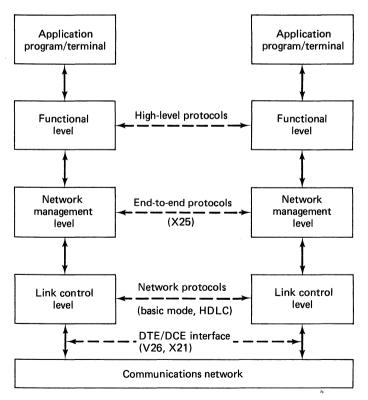

Data Transmission and Distance 71 Telecommunications Services 73 Suppliers of Telecommunications Services 74 Circuit Arrangements 77 Circuit Characteristics 81 Noise, Distortion and Error Rates 87 Transmission Timing and Synchronism 89 Communications Interfaces 93 Data Link Controls 96 High-Level Protocols and Network Architectures 115 Terminals 117

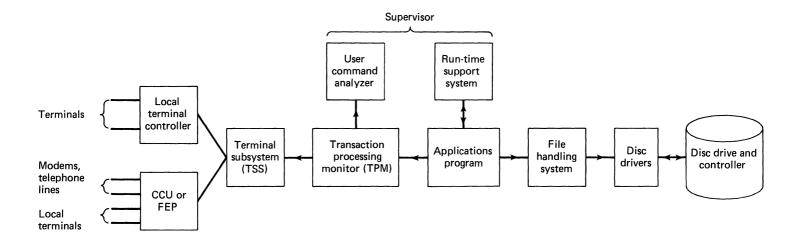

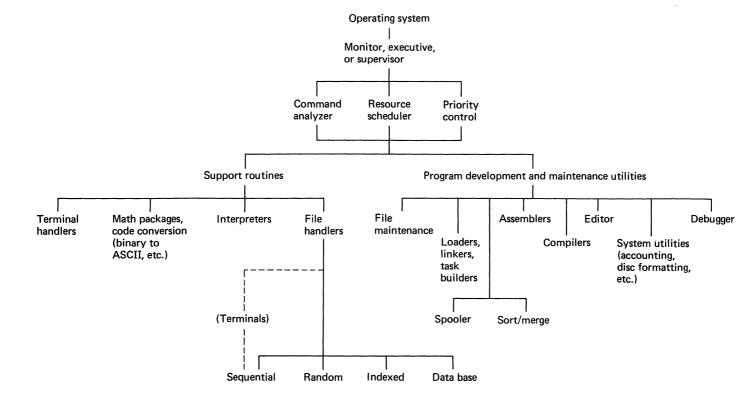

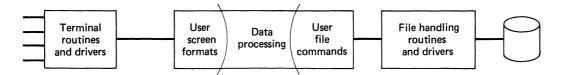

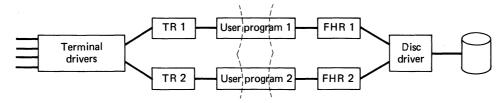

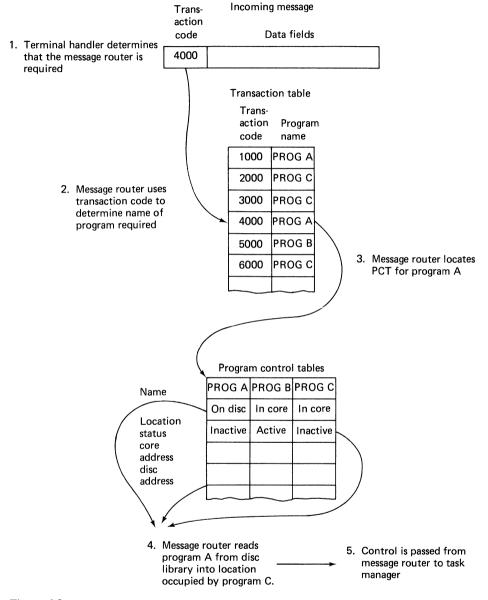

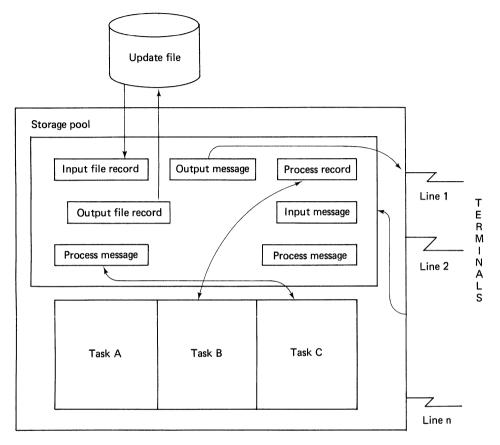

#### 4. **Transaction Processing and a Review of Minicomputer** Software

Modes of Operation 127 Teleprocessing Systems 130 Transaction Processing 131 Transaction Processing and Terminal Handling Functions 136 Overview of System Software 143 Tasks, Programs, and Procedures 149 Operating Systems 150 Assemblers and Loaders 158 High-Level Languages 158 Program Development Aids 164 File Management Systems 164 Communications Software 171

#### **Data Communications Handling on Minicomputers** 173 5.

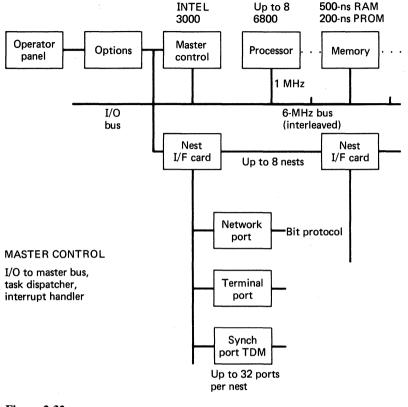

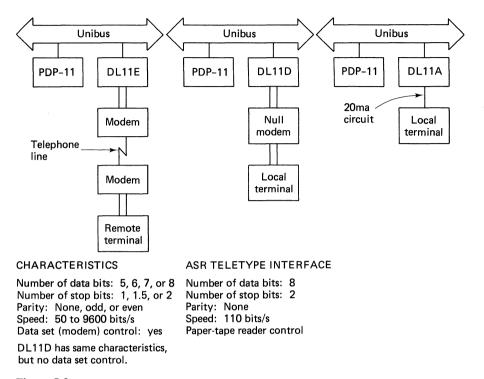

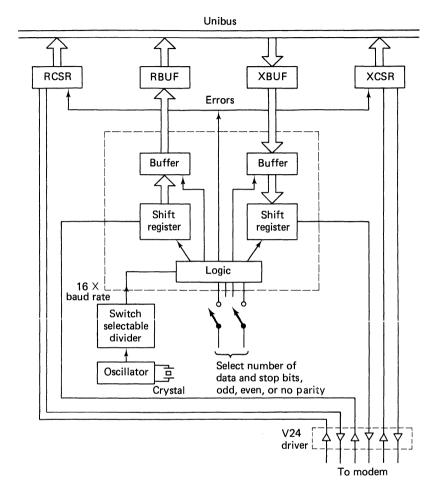

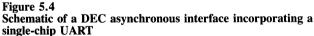

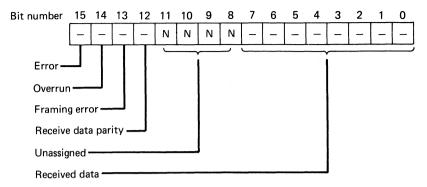

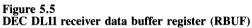

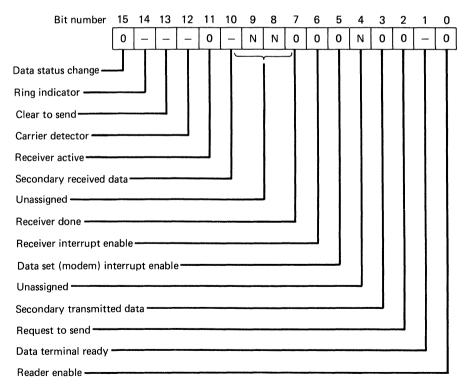

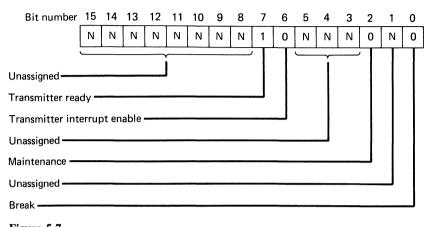

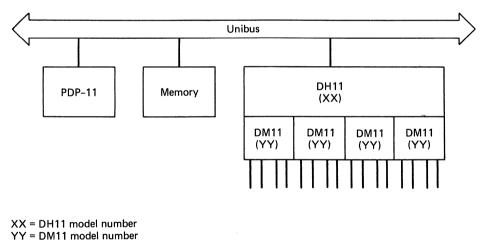

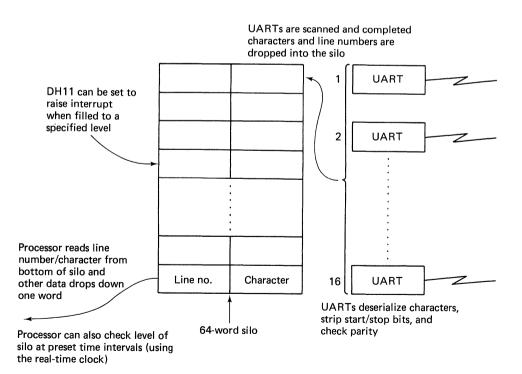

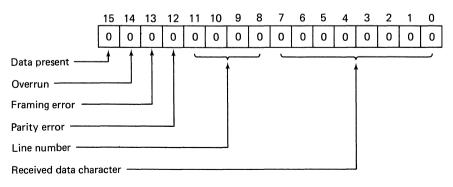

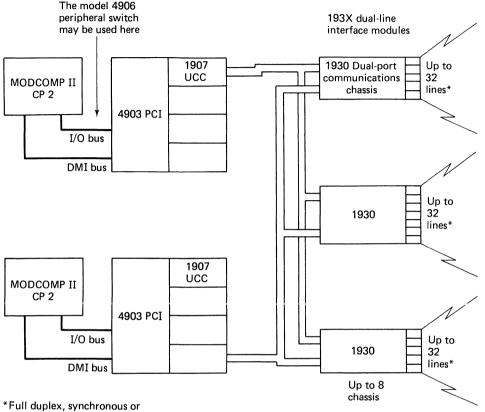

Digital Equipment Corporation PDP-11 Series 173 Modular Computer Systems MODCOMP II CP2 183

#### 6. **Data Communications Software**

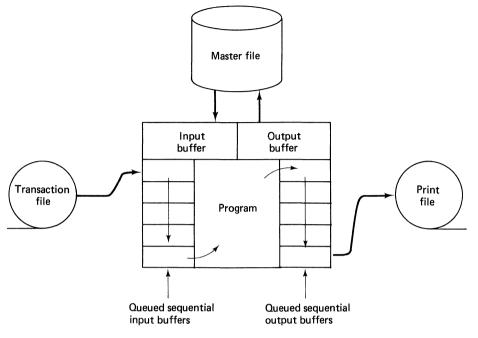

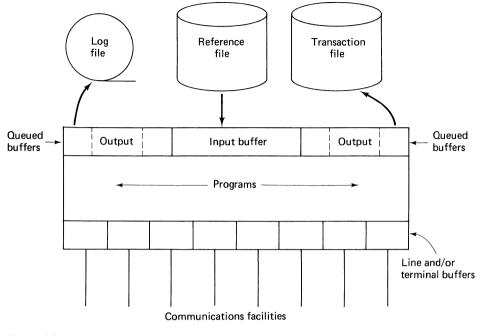

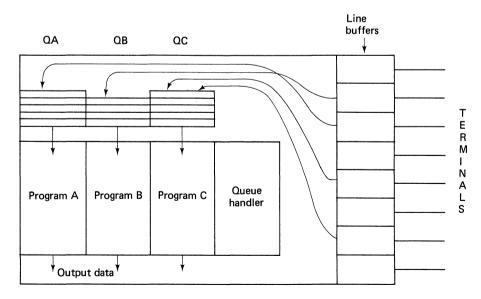

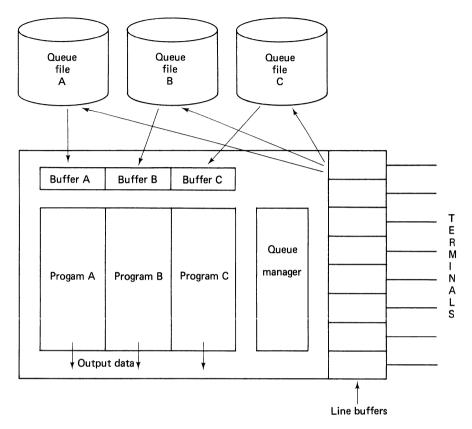

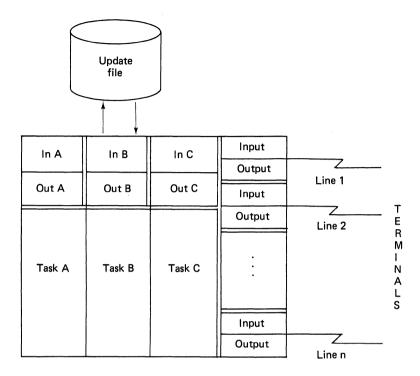

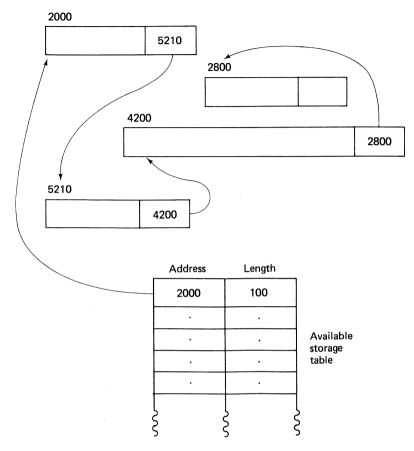

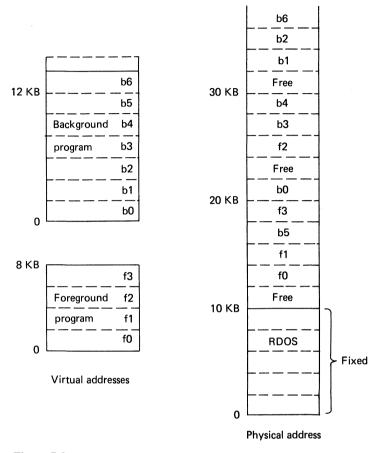

Task Management 193 Program Management 204 Storage and Queue Management 206 Design of Teleprocessing Programs 214 71

127

193

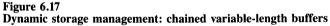

# 7. Minicomputer Operating Systems: Some Examples 217

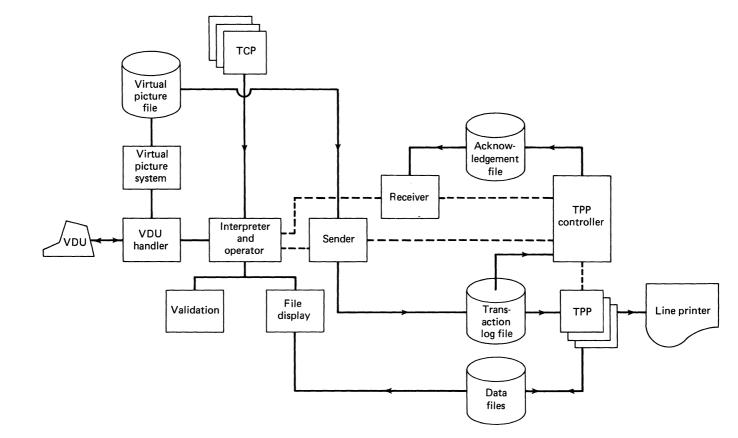

A Review of General Features 217 The Operating Systems Reviewed 220 Data General RDOS 221 Digital Equipment Corporation RSX-11M 227 MODCOMP MAXCOM Communications Executive 237 The Texas Instruments DX10 244 Microcomputer Operating Systems—Digital Research CP/M 252 DECNET 259

# 8. High-Level Packages

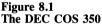

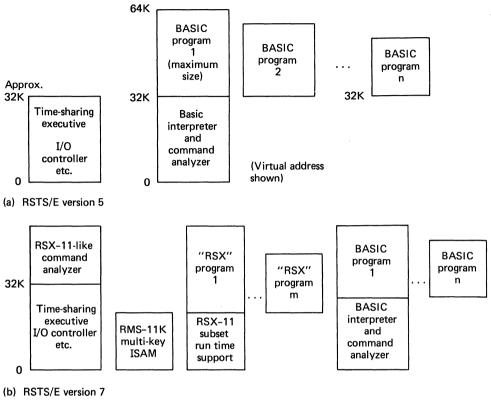

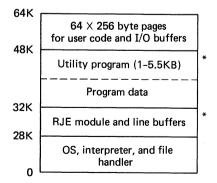

Minicomputer On-Line Terminal Handling Packages 270 Key-to-Disc Systems 270 Digital Equipment Corporation COMTEX 271 Digital Equipment Corporation COS 350 271 Digital Equipment Corporation RSTS/E 272 Data General IDEA 276 Computer Automation SyFA 277 BLIS/COBOL 279 Computer Technology TAD 279 Digital Equipment Corporation TRAX 280

# 9. Acquisition and Implementation

Acquisition 285 Implementation 287

# **10.** Case Studies

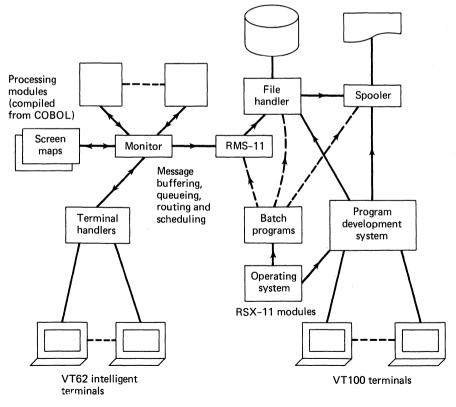

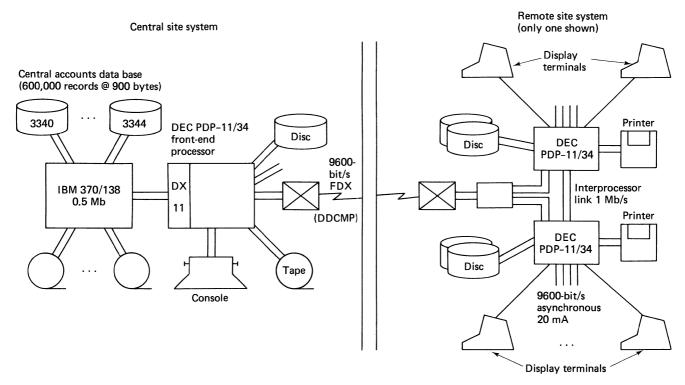

- 1. Digital Equipment RSTS/E System 290

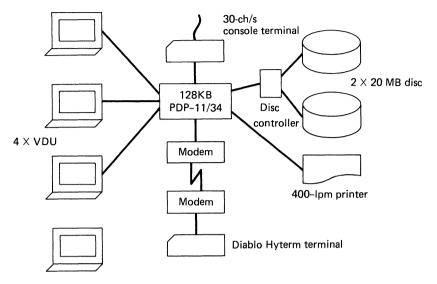

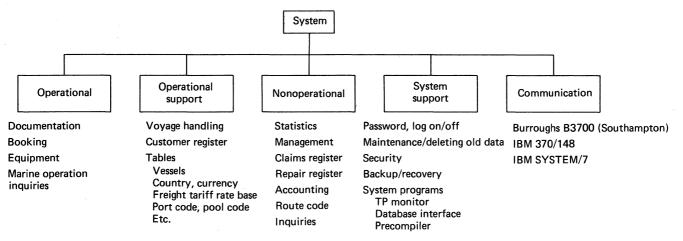

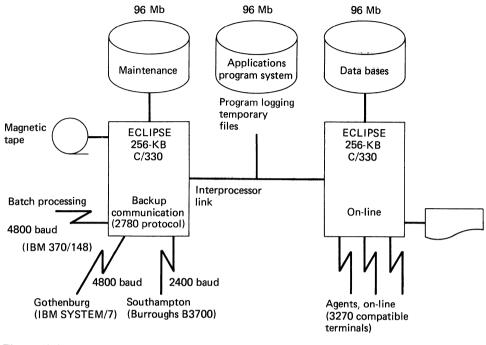

- 2. Data General ECLIPSE System 293

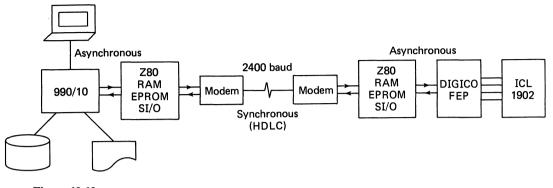

- 3. A Distributed System 304

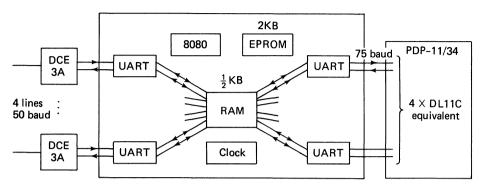

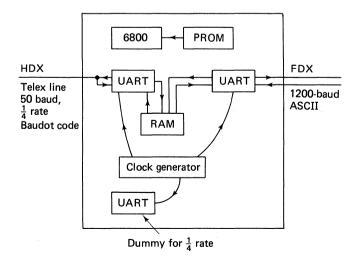

- 4. Use of Microprocessors in Special Purpose Data Communications Devices 315

Index 323

269

285

289

.

# Foreword

Computing, like any high technology business, is burdened with unanswered questions, some serious, others comparatively trivial. A splendid example of the latter category has been the endless debate over who invented the first stored program computer. A more critical inquiry is posed in discussions about just what a minicomputer is, or for that matter what a terminal, a small business system, or a terminal computer is.

Debate questions are always fun. Engaging in deep dialog is a lovely way of spending time. It is at least as good as attending conferences, writing papers, and otherwise avoiding the need for work. Discussing matters whose resolution is largely a semantic issue clearly permits the practitioner the luxury of avoiding technical decisions due last week or last month. Since it is not considered cricket to terminate the conversation of people who debate these lofty and nearimpenetrable matters, the clever gamesman can survive by avoiding decisions, with their consequent risk of error.

It has long been known that certain MIS professionals have very bad attitudes on these matters. They attempt to solve problems by creating workable solutions. This evil practice should be stopped, because it might force the debating societies to stop debating and go to work—the last thing the talkers desire. If one is forced to bet one's reputation on a path or a fork in the road, the chances for error are high. Better to debate than to do!

Books about minicomputers invariably seem to fall into the trap of spending several hundred pages attempting to define minicomputers. The matter used to be very simple for pragmatic types who didn't worry about elegance. The parameters were fairly simple: (1) physical size, and (2) manufacturer's name. Consequently, a computer that could be picked up by an average-size individual, one manufactured by anybody other than a traditional mainframer, was by definition a minicomputer. Unfortunately, some recent developments have destroyed this easy definition. There aren't many people who can get their arms safely wrapped around an H-P 3000 or a DEC PDP-11/44. Anyone who *can* is a candidate for several Olympic awards. The other side of the equation has also come apart: IBM entered the minicomputer business directly, Univac joined by acquisition, and Honeywell reenergized its long dormant minicomputer operation. End of one pass at decision-making criteria!

So what is a minicomputer? Can a machine with a 32-bit-wide data bus, a 300 ns cache memory, and a million bytes of main store be called a mini-anything? Of course it can't. The truth is that yesterday's definitions are now nearly meaningless. There is a tidy, smooth curve of machine power beginning with micro-processors and running exponentially up to a Cray-1. Somewhere along this curve the traditional independent observer can decide that these are micros, these are minis, these are maxis, and everything else is a mainframe. You pays your money and takes your choice; who cares what it is called?

Having thus neatly solved the question of defining the minicomputer, it is necessary to find the separation between one of them, whatever they are, and a terminal. This should be a good deal easier because the parameters are better known.

A terminal is a box. That box is remote from a computer. So far, so good. Does a terminal have: (1) intelligence, to process information, (2) private store, (3) mass storage even in limited quantities, (4) human intervention devices such as keyboards, and/or (5) connections to the computer? These questions define the various classes of terminals. If there are enough yes answers, perhaps the box in question is not a terminal at all but a computer. Can the answer be determined numerically? Does a single yes mean terminal and three or more mean computer?

As with the case of the minicomputer definition, I am now involved in a semantic snarl-up at least partially of my own making. Indeed, does it really matter? Isn't it more than enough to say that a terminal is a remote electronic device that has the power to somehow communicate something to somewhere in one of a variety of forms? Enough!

None of this semantic footwork really matters very much to the dirty-handed workers in the trade. People take a machine, grab some devices that work remotely and go to work building systems that provide intelligence to the end user community residing at the periphery. That is what it is all about. How the goal is reached and what it is called should be relegated to the Oxford Union.

Having placed definitions in the category of a problem that has been solved (a longtime ploy of politicians who believe that if the problem is said to be solved it is), we must turn to the real snags in computing during the next few years.

The data communications explosion begun so promisingly a few years ago continues to run into roadblocks. Most of the obstacles are erected by longtime communications carriers whose general approach is to try to bar all the new freedoms the FCC carefully nursed into life. The common carriers are not stupid. They see major revenue sources flying away as their aging, analog-based plant rapidly falls into disuse before its natural accounting life is ended. There is little quarrel with the notion that a forty year write-off on technological equipment is an invitation to disaster. However, the fiscal policies and practices of the carriers were established and firmly set long before computers were invented. The repeated, public predictions by Howard Anderson of the Yankee Group that the common carriers will be an easy target when the computer people really start after them seem to be coming true. But this is another of those debating-society issues.

The carriers are digging in for a long fight. It isn't merely a matter of matching their services to those the independents are making available. To quote myself from a near-forgotten *Datamation* article, "If MCI and Datran didn't exist, we would have had to invent them to keep AT&T honest." What has happened is that the carriers have reacted savagely enough to make the future bleak for all but the best financed independents. Datran is gone, even though it cost AT&T \$50 million in settlements. By its own admission MCI is only marginally profitable. The regional carriers are gone. Telenet was acquired by GT&E.

The traditional carriers are defending on many levels. First, they take every legal action possible to delay the implementation of new services by independents. Second, they are providing their own competitive services. Third, they are attempting to remove from service functional capabilities already in general use—for example, distance pricing and private line networks. Finally, they are always just a little slow in connecting local loops and repairing outages.

All of this means that the natural, normal, and highly proper convergence of data processing and data communications is a good deal more difficult than it should be. The problems are political and economic, not technical. This book describes systems in being and how they are built. Neither it, nor any other book on the market, can forecast the political climate that may well undercut a sound technical performance.

The clash between a slow-moving, regulated industry and a very rapidly changing, thoroughly unregulated business is of increasing concern to the user community. Knowing how to build a system is of little value if a very large traffic cop keeps saying, "You can do that" at regular intervals. The cop wears many disguises. He may appear as a British labor leader who has instructed his men not to install non-GPO modems, or as a Nigerian minister who refuses to allow any encoded data on public transmission facilities, or as a Canadian telecommunications minister who believes that all necessary transmission can be accomplished on public networks.

Who suffers from these actions? Not the mythical general public whose interests are allegedly being protected. The loser is the end user at whose behest remote, terminal-based systems are being constructed. The solution is political. Corporations don't have the influence when it comes to a clash between the need for more effective business communications and an impact on the plain old telephone service.

A sense of outrage continues to exist in the computer community over the restrictions, real and apparent, arbitrary and legislated, that grow ever more widespread. The game is at a high level because the revenues involved are very large, billions of dollars. Even the most astute technical people are likely to be blind to these affairs; their interest is in getting the job done.

Before 1976, the direction and pace of the data processing and data communications convergence were fairly clear. The technical job to be accomplished was, and still is, becoming ever clearer. Books like this describe what has to be done. But the whole effort will fall apart if the industry's technical experts do not take the time and energy to come to grips with political and legislative forces. Things are happening that may undermine even the best planned efforts. It was previously considered reasonable to assume that telecommunications regulations would be eased. In actuality, matters have gone quite the other way. The French PTT still wants to pull cable in an era when satellite transmission is completely routine. Fiber-optical transmission is regarded with suspicion by those who grew up with twisted pairs of copper wires. Digitally based communications equipment cannot approach peak effectiveness when inhibited by operating parameters in a thirty-year-old analog carrier. Voice, data, and image transmissions are still seen as separate entities when all three have become little more than the movement of digital bit streams.

The technology of communications-based systems is expanding at a rapid pace. Each new development, however, is delayed by the defenders of the past. The excuses vary but the most commonly heard are: "unproven technology," "too great an impact on existing services," and "no tariff has yet been filed."

The common carrier attack on remote systems has been sustained, but at worst their efforts can only slow down implementations. But there is another emerging threat that has the possibility of totally destroying effective remote computing the concept that data should be held within national boundaries as a national resource.

Remote computing systems by their very nature weaken the idea that all data should be maintained locally. In fact, while much of day-to-day operational data should properly and for good technical reasons remain local, there is a valid set of aggregate data that make little sense locally. How is a modern corporation to optimize its use of scarce resources if arbitrary, often capricious, regulations are placed on its ability to move the data to the location where it is needed?

The issue of transborder data flow is rapidly growing in its impact upon remote computing systems. It is beyond the scope of this book to discuss whether it is a real issue or one dreamed up by a tiny minority of social activists as another means for controlling large corporations. However, it is an issue with a major potential for mischief.

Of still more recent generation is the issue of national vulnerability to computer/communication outages. The thesis as evolved by a Swedish governmental committee revolves around the notion that each national society must have all of its own facilities for keeping the computer/communications complex going. Why? Because the big, bad wolf, presumably an American-made wolf, will come along and reduce a nation to third-rate status by failing to provide spare parts or the technical know-how to keep the complex functioning. It is hard to take such scare tactics seriously. Yet it would be foolish to assume that the threat will simply disappear.

The point in both of these cases is the same. It is no longer sufficient for a technician to stay purely technical. The construction of computer-based systems is full of social, cultural, economic, and political questions that can no longer be cheerfully disregarded. Enough good systems have been built for the alarm-raisers to have had their interest awakened. A cynic might suggest that we ought to have failed more often because if that were the case, the politicians would leave us alone. So perhaps some of the energy and effort devoted to trying to decide what a minicomputer is, or what a terminal is, should be applied to the process of maintaining freedom to implement. The definitions are only of importance to lexicographers, but the politics are critical. The deeper people delve into remote computing systems, the more the impact will be if the system proves "culturally unacceptable."

We used to think that technology was hard. It isn't. It's still not easy or offthe-shelf. The multiple forces that pull and tug within a system are not that easy to see, and it is still hard to find all the trade-offs. But Healey and Hebditch have pulled out most of the issues into plain sight and tried to dispel the mystery. It's not a black art, nor does it require implementers capable of leaping tall buildings.

Minicomputer systems can be thoroughly constructive for the corporation in which they are based. They can also be major traps for the unwary. There are rules of the game that must be obeyed even as with large-scale mainframes. Healey and Hebditch detail the structure for minicomputers in the distributed environment. Their game plan is sound. Now it is up to all you implementers to follow their precepts.

Philip H. Dorn

# Preface

This book is the culmination of a discussion that has been going on for some four years between the authors. During the mid-1970s we have seen the steady convergence of computer and telecommunications technologies. In particular, the data processing industry has continued to move away from batch processing to transaction processing, and networks of terminals have improved user access to computer systems.

Conspicuous in these trends has been the emergence of the minicomputer. These compact and powerful processors, which originated in control systems, have found a new role in the commercial field as data concentrators, message switchers, front-end processors, terminal controllers, and special-purpose transaction processors. A common characteristic in these systems is the use of interactive and telecommunications facilities for data transport.

Although the cost/performance ratio and general modularity of minis make them very difficult to ignore for many applications, the problems of system design, development, and implementation can be numerous.

The authors are consultants, one majoring in minicomputers, the other in communications systems, both having a reasonable knowledge of the other's specialization. During many discussions (in just as many watering holes), we managed to convince ourselves that if we had an *average* understanding of these problems, then at least half the data processing profession was really struggling!

Minis are ideally structured for handling data communications and terminals, but that does not mean that they always do it well. This book is intended as a review of minis, communications, and how the two work together. Many products are described by the way of illustration; where a specific device or software package is mentioned, we do not intend to imply that it is any better or worse than comparable components, merely that it is representative of a certain approach.

If this book is for anyone in particular it is for the COBOL programmer whose boss is planning to buy a six-pack of minicomputers on which to base a network of interactive terminals. But we hope that technical managers, designers, systems programmers, and application programmers in user companies, manufacturers, and software houses will find it helpful in the development of effective systems as well as in the development of their personal expertise.

Martin Healey David Hebditch

# 1

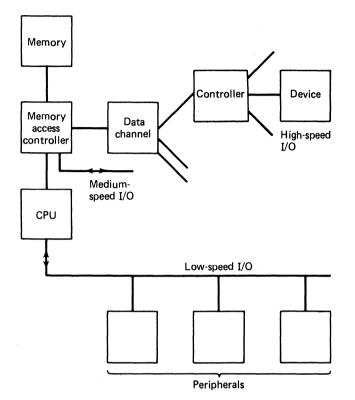

# The Role of the Minicomputer in Data Communications and Distributed Processing Systems

This chapter reviews the various roles minicomputers play in terminal-based data processing and communications systems to provide a background against which we can consider the technical problems involved in implementing minis in such roles. For the time being we shall define the mini as a small-scale, general-purpose computer such as the Digital Equipment Corporation's PDP-11 or Data General's NOVA series. Small business computers (such as the IBM System/3 and ICL 2903) and special-purpose distributed processing products (like the Burroughs B776 and IBM 8100) are excluded. A more complete definition of the minicomputer will be discussed in chapter 2.

# Some Typical Systems

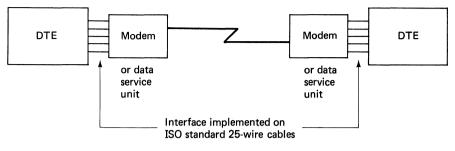

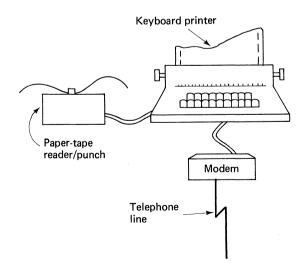

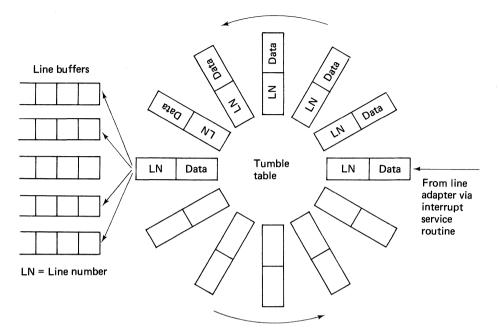

When minicomputers were first developed, they tended to be used in industrial process-control and data-acquisition systems. In the former case, the nature of the application demanded a processor capable of acting in "real time," in the original sense of the expression, a processor that could economically and efficiently interface to a number of local and/or remote telemetry and control devices. Most minicomputers were designed, therefore, to operate in a highly responsive on-line environment. Their development engineers had probably never heard of batch processing (or data processing, for that matter). Universities and research bodies also quickly saw the potential of the mini, which typically is used for one-off jobs generally developed in batch or (more often) interactively, using high-level languages such as FORTRAN or BASIC. One of the earliest uses of minis outside the industrial and research fields was in message switching. Clear-text messages received over telegraph circuits are transmitted to destination teletypewriters/ teleprinters according to routing information held in standard or nonstandard headers. Disc or drum storage may be used to implement a delayed-delivery facility.

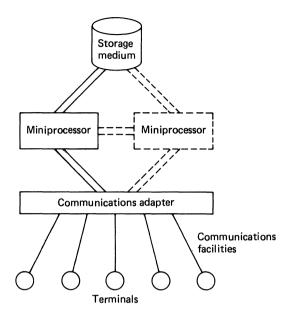

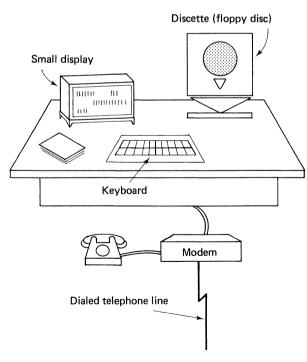

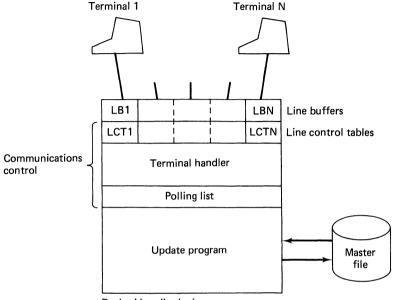

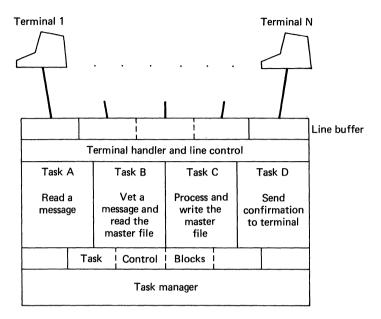

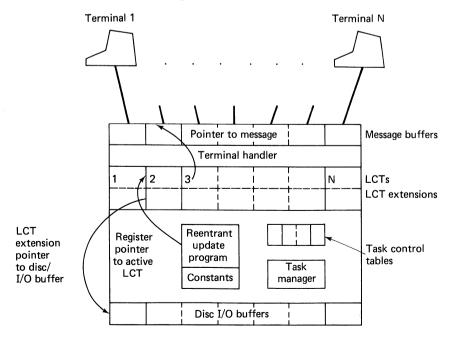

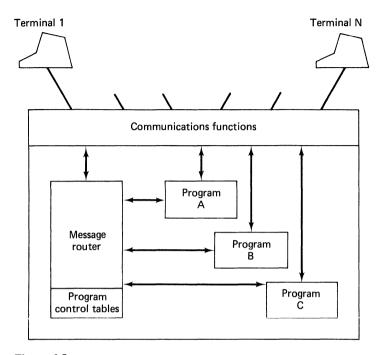

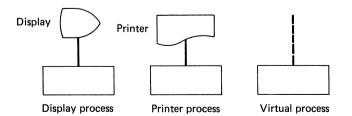

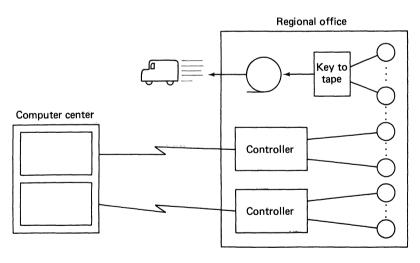

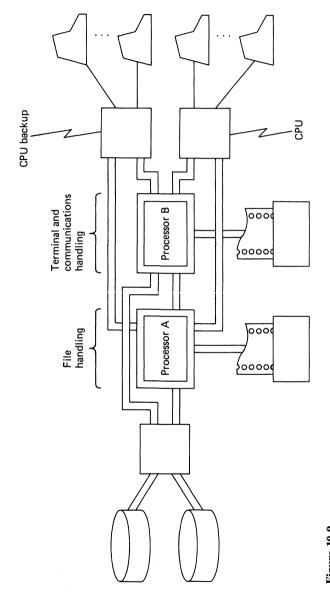

Figure 1.1 The minicomputer as the central site processor (in single or multiple configurations)

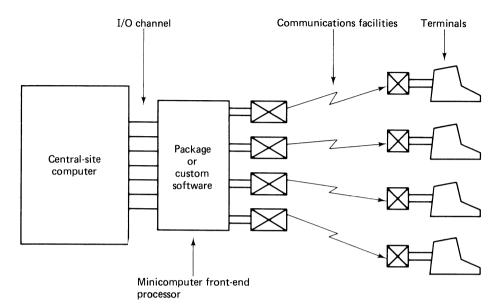

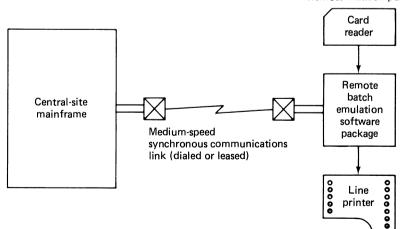

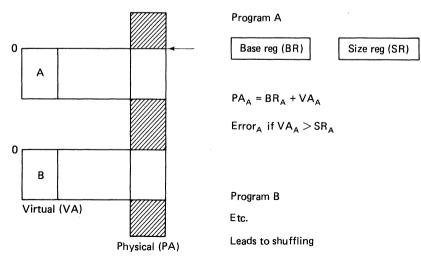

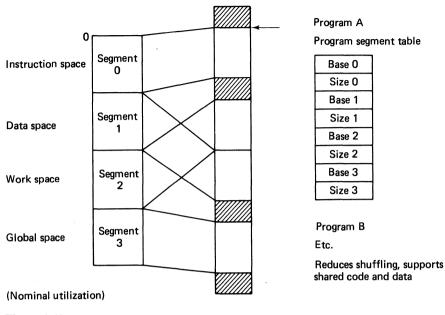

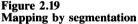

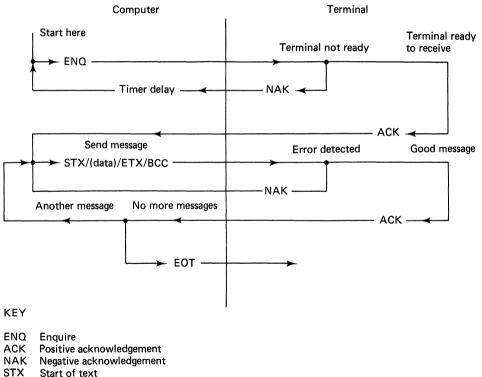

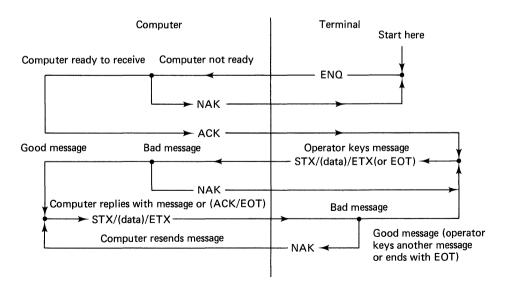

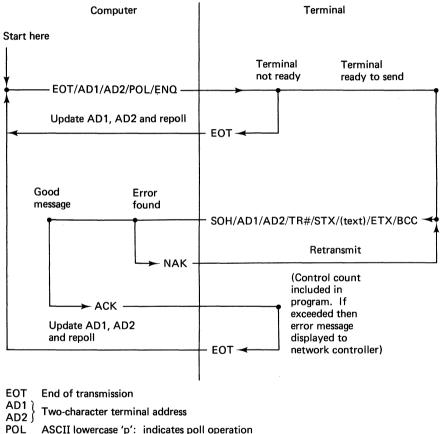

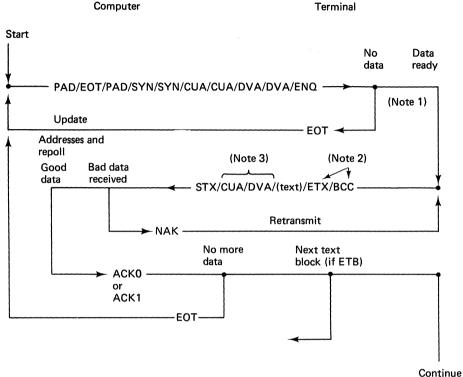

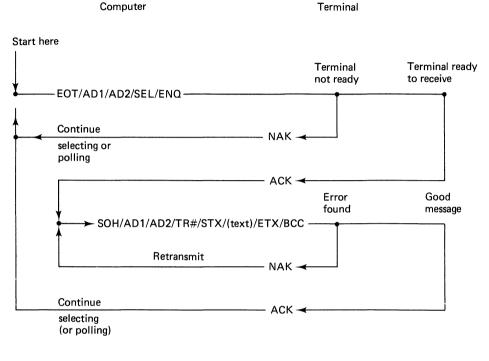

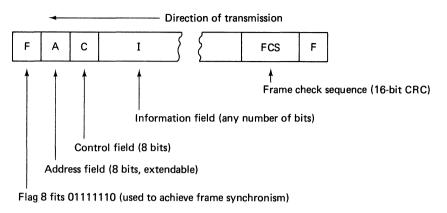

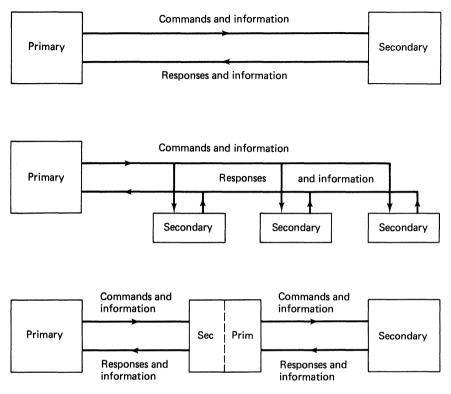

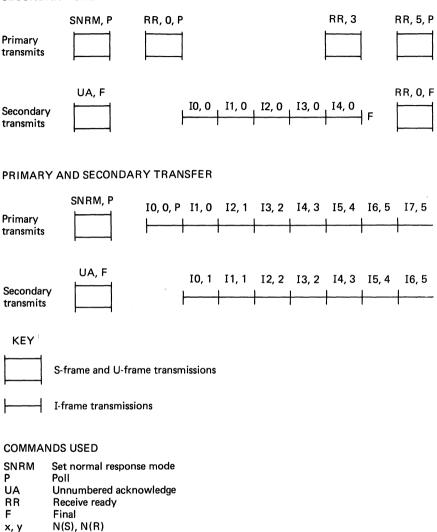

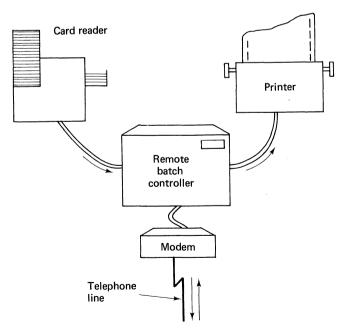

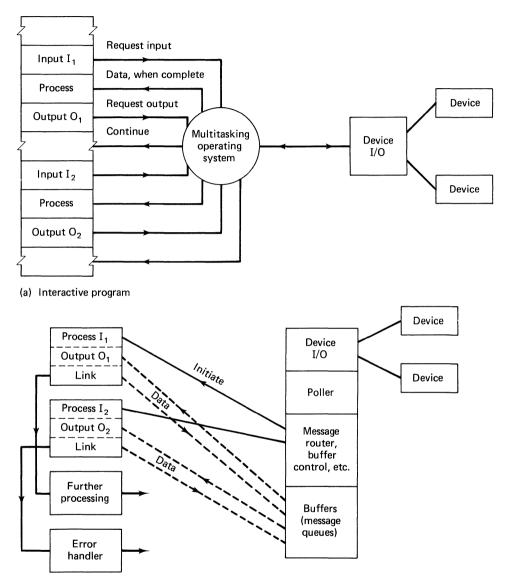

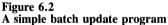

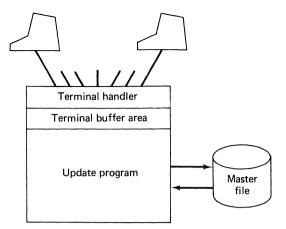

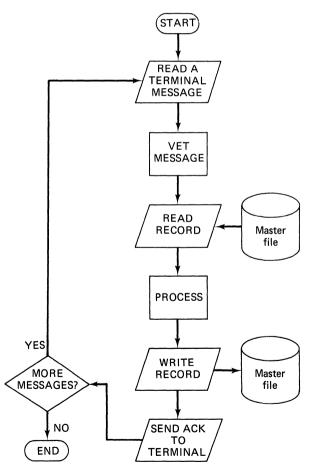

All the above systems are typical of the mini used in a stand-alone situation (as shown in figure 1.1). Until recently, the application of the mini as the main computer in commercial data-processing systems was somewhat limited mainly as a result of the lack of suitable software. Today the problem is no longer a lack of software but the choice of a package/language from the plethora of programs now available for business applications. Most such packages assume application as terminal-based transaction processing systems (the structure and relevance of this approach will be considered in chapters 7 and 8). The two earliest and most widespread uses of minis in commercial teleprocessing were as front-end processors (figure 1.2) and as remote batch terminals (figure 1.3).

The first generation of communications control units (CCUs) typified by the IBM 2701, 2702, and 2703 were hardwired devices, inflexible and expensive. In order to achieve a more adaptable, cost-effective solution that would relieve the mainframe of some of its steadily increasing control-program load, many software houses (and some users) developed their own software to work in one of three ways: to emulate the CCU (for example, the IBM 2703); to emulate another peripheral controller (for example, the IBM 3803 magnetic tape controller); or simply to support the mainframe input/output (I/O) channel.

Because of its market size IBM was inevitably subject to attack by this approach: its response was that because central processors and storage were becoming so cheap, there was no point in shifting control program functions into

Figure 1.2 The minicomputer used in a communications control unit (frontend processor)

Remote minicomputer

Figure 1.3 The minicomputer used to emulate a special-purpose remote batch terminal (potential distributed processing system)

the communications control unit. Soon after that, IBM announced the 3704 and 3705 programmable control units—not necessarily because the company had changed its mind about front-ending, but because it was becoming impossible to fulfill users' increasingly heterogeneous teleprocessing needs in a hardwired controller. In fact, since the 370X was introduced, the control software in the central processing unit (CPU) has become larger, not smaller. In spite of the 370X, companies still find it cost-beneficial to front-end their mainframes with a "foreign" mini. Other suppliers who have been front-ended include Control Data Corporation, Univac, and Burroughs. (Honeywell is front-ending with its own minis.)

The minisuppliers and systems houses have also focused their attention on another communications product: the remote batch (or remote job entry) terminal. Originally the RBT was also a hardwired device, typically providing communication with remote input/output peripherals such as card readers and line printers. Independent suppliers soon found that they could put up an alternative package that included similar peripherals but used a mini-based controller and a program that emulated operations used by the mainframe manufacturers' products. Such emulators have been produced for the IBM 2780/3780, ICL 7020, CDC UT-200, Univac DCT-2000, and others.

One advantage of the mini solution is that merely by changing the emulator program one can work to a Univac data center for part of a day and to an IBM center for the rest. Moreover, once the mini is installed other peripherals (including interactive terminals) can be connected for applications. Even in its remote batch configuration, the system can be used for local vetting of the input. This is the beginning of distributed processing, which will be discussed later.

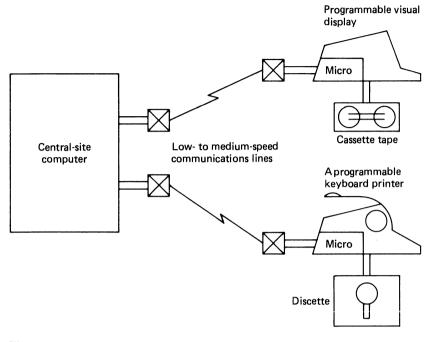

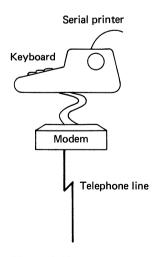

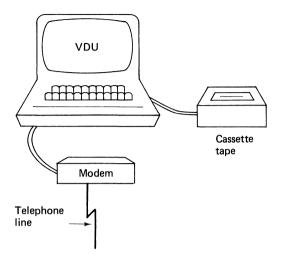

Figure 1.4 illustrates the use of minis in another type of terminal; the interactive visual display unit (VDU) or keyboard printer. In such devices the miniprocessor was closely integrated into the product. In practice many commercially available units (Datapoint, for instance) employ specially made processors, often micro-based. The processor and storage are used to refresh the cathode ray tube (CRT) and to implement various facilities (variable and protected fields, selective transmission) as well as to control the communications function to the CPU. The minis still are relatively low in power because of the limited demands made upon them. As with RBTs, such programmable terminals (especially the VDUs) were provided with emulators so they could be sold in competition with the equivalent units from the mainframe company. Such units included the IBM 2265, IBM 3275, and ICL 7181 stand-alone displays. Peripherals were generally limited to compact media such as cassette tapes and discettes (floppy discs).

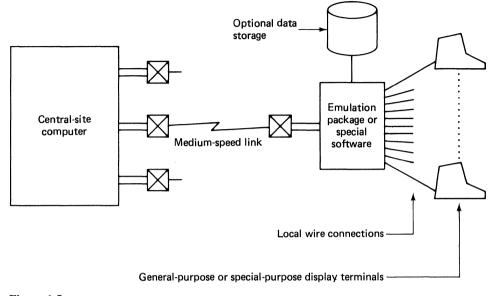

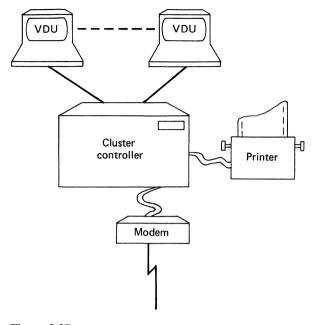

Many remote terminal products use the cluster concept in which a number of terminals located in one office block or plant site can share the logic of a single local controller (see figure 1.5). Rather than using expensive modems, the terminals are connected locally via coaxial or multi-core cable (V24 or current loop). Such cheaper circuits generally give a maximum terminal-to-controller distance of less than 1000 meters without amplification or regeneration. The

Figure 1.4 The minicomputer and small special-purpose computer in programmable (intelligent) terminals (distributed processing system)

cluster approach is often used for general-purpose VDUs but can also be encountered in more special-purpose configurations such as controlling point-ofsale terminals in a department store or shop-floor terminals in a production plant. If the VDUs are attached through video cables, the screen may be refreshed from a buffer that is an area of mini main storage rather than a component of the display itself. This reduces the cost of the terminals but increases the overhead on the controller. If, for example, each CRT needs refreshing 50 (or 60) times per second, then an interrupt needs to be raised once every 20 milliseconds for each terminal so that the data can be "rewritten" to the screen. This usually imposes such an overhead that many such cluster controllers rely on a hardware component for refreshing the screen, a solution that steals memory cycles rather than processor cycles. These problems do not, of course, exist with the special-purpose terminals (unless they have unbuffered CRTs incorporated in them). Hardware implementation of clustered VDUs are typified by the IBM 3270 range. With some terminal systems, the companies developing the mini-based cluster controllers often provide software that enables them to emulate the 3270, thereby making it possible to compete with IBM. Such suppliers include Harris and Raytheon. The use of an emulation package sometimes precludes the development of

Minicomputer-based terminal cluster controller

applications routines for the cluster controller. On the other hand, many suppliers now positively encourage the insertion at least of data vetting routines by providing a high-level programming language (Mohawk Data Science's MPL, for example).

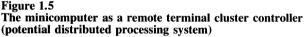

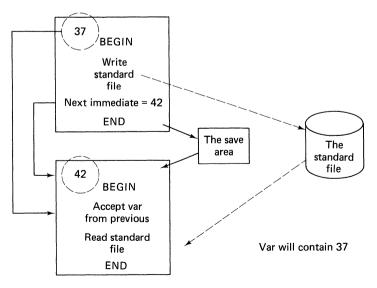

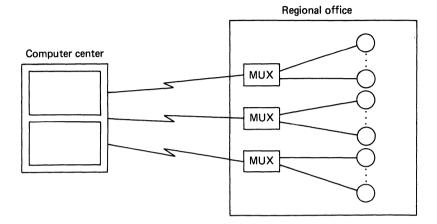

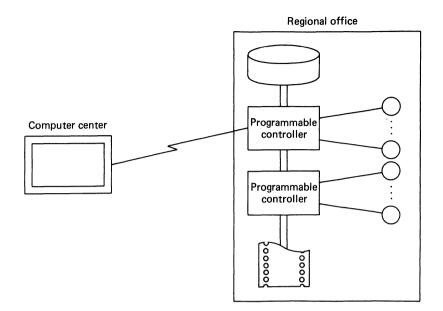

Also falling loosely into the category of cluster controller are the key-to-tape (key-to-disc) systems featuring a medium- to high-speed communications adapter which can be used for the onward transmission of data to a central site. Most such key-to-disc systems are based on minicomputers packaged in by the supplier. These systems are marketed by companies like MDS, CMC, and Entrex (Redifon/ Nixdorf). In addition to providing local power to terminals, programmable cluster controllers also reduce the cost of communications facilities to the central site. Minis are sometimes used to perform this function exclusively, as shown in figure 1.6. In this case two minis are being used as transparent time-division multiplexors (TDMs). This technique avoids the need for separate dialed or leased lines (telephone or telegraph) from each terminal to the CPU. Instead, a terminal (usually a low-speed interactive device such as a Teletype or IBM 2741) is connected to the nearest available remote multiplexor. Each port at the multiplexor is allocated one or more character positions in blocks of data which are exchanged between the remote multiplexor (MUX) and one of almost identical configuration at the CPU. The in-house MUX receives the transmission blocks and distributes

each character to its relevant port (the one through which the CPU expects to communicate with that terminal). Similarly, the ports between the MUX and the CPU are scanned for outgoing characters and these are blocked together for transmission to the remote unit which will similarly distribute them onward to the

terminals. Normally, each terminal has positions in a block permanently allocated to it. The faster the speed of the terminal (or line, if it is buffered) the more positions will be allocated. This approach can be wasteful, because even if a terminal is inactive (albeit momentarily) a null character still needs to be sent in order to maintain the positional identification of the subsequent characters. To overcome this, the software packages written for some mini-based multiplexors avoid positional significance by sending two characters, the line number and the data character itself. Although this would appear to double the occupancy of the medium- to high-speed circuit linking the multiplexors, the net effect is often beneficial, since interactive terminals usually transmit and receive very few characters while they are switched on. This is generally known as "statistical multiplexing." At the central-site computer, the multiplexor may be a separate device interfacing to a communications control unit or it may be a front-end processor in its own right. In the latter case, the connection to the CPU will be via the I/O channel rather than CCITT V-series (EIA RS-232) interfaces.

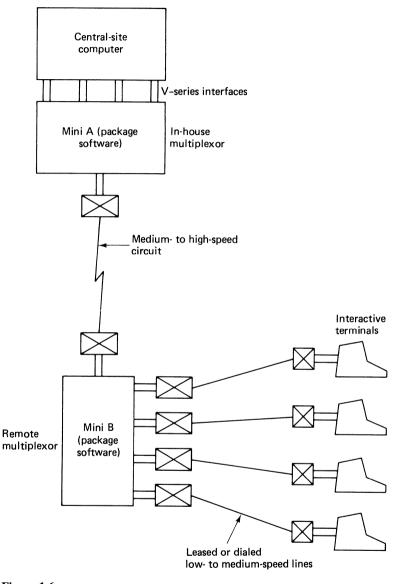

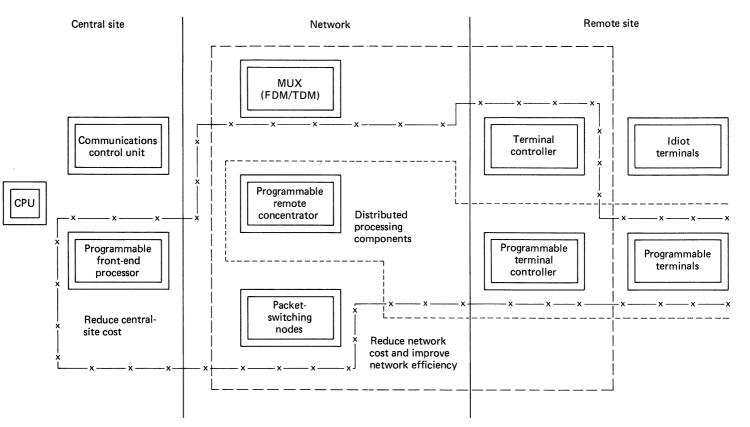

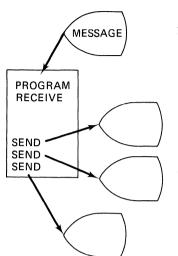

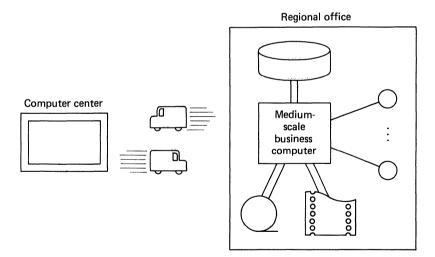

It is most unusual for application functions, even very low-level ones, to be programmed into a TDM. These are essentially transparent devices (neither the terminal nor the CPU needs be aware of their existence in the network) and the timing constraints tend to prohibit the meaningful intervention of processing activity. *Concentrators* are nontransparent devices that also serve to reduce line costs but at the same time enable application processing and control functions (such as those possible in mini-based cluster controllers) to be implemented (see figure 1.7). Unlike terminal controllers, concentrators are used when the terminals are remote from the concentrator and connected over telegraph or telephone lines (which may be dialed, leased point-to-point, or even leased multipoint circuits).

Whereas time-division multiplexors are *character-interleaved* systems, concentrators work on a *message-interleaved* basis. To each incoming message, the concentrator software adds a prefix containing the source-line address and/or terminal address. Messages can then be formed into larger blocks for onward transmission to the central site. The same arrangement in the opposite sense is used for data going from the computer to the terminals. Note in figure 1.7 that the concentrator does not require an equivalent device at the center and is treated by the CPU as though it were a terminal itself. Reducing the number of physical terminals (as against logical terminals) directly connected to the CCU has the effect of reducing processor overheads.

Emulation techniques are sometimes used with concentrators but not nearly as often as with cluster controllers. Whether emulation is a factor or not, the use of minicomputers as concentrators provides substantial opportunities for applications programming. The peripherals available—including disc (especially low-cost cartridge), tape, and line printers—serve even further to facilitate the development of relatively sophisticated application functions. Minis also provide greater flexibility in the type and variety of terminals that can be attached and the method of communicating to the central site. For example, the main link may be duplicated or the concentrators themselves may be interlinked to provide an alternative path to the CPU in case of line failure.

Figure 1.7 The minicomputer as a communications concentrator (potential distributed processing system)

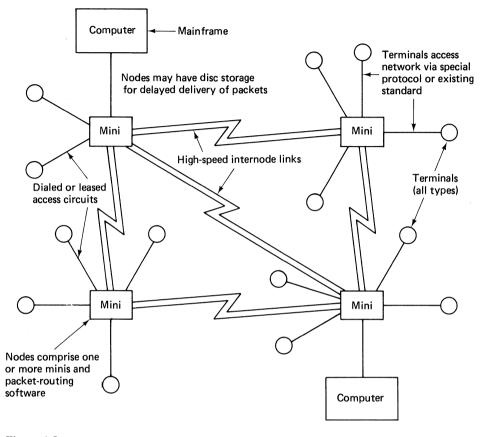

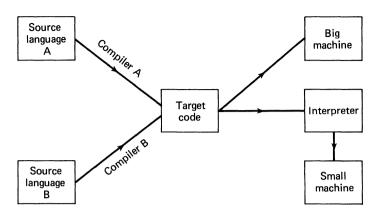

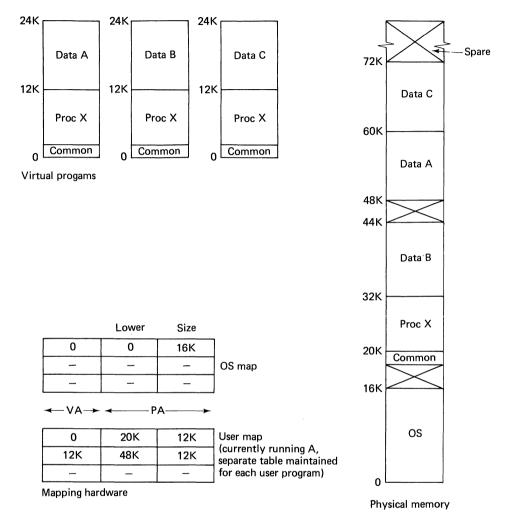

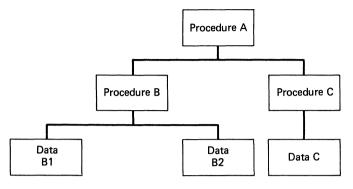

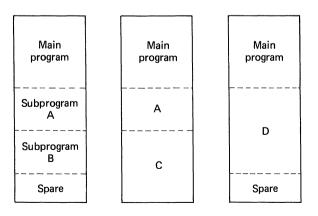

The use of minis in some of the communications networks described (in terminals, cluster controllers, and concentrators) clearly opens up possibilities of developing *distributed processing* systems. Such systems are characterized by the implementation of *application* functions (in addition to *control* functions) in two or more system components that are linked together in some way. These systems are often confused with *distributed switching* networks such as the packet-

switching network shown in figure 1.8. All packet-switching networds do (or should do) is improve the performance and reduce the cost of data transmission. Of course, a distributed processing system may use a packet-switching network for communications between terminals and CPU, but no applications-related code can exist in the switching nodes. In almost all packet networks installed to date, minicomputers have been used for the switching nodes. Packet-switching will be discussed further in chapter 3.

# Why Use a Mini?

When confronted with the problem of selecting the most appropriate hardware for a particular communications function the system designer can choose from four main classes of equipment:

|                                                   | STRONG<br>FEATURES                                                                             | WEAK<br>FEATURES                                                                                |

|---------------------------------------------------|------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| General-<br>purpose<br>mainframes                 | Power*<br>Expandability*<br>Supplier stability<br>Resilience                                   | Price<br>Flexibility*<br>Adaptability*<br>Architecture*<br>Modularity*                          |

| Small<br>business<br>computers                    | Supplier stability*<br>Resilience*                                                             | Price<br>Power*<br>Flexibility<br>Expandability*<br>Adaptability<br>Architecture*<br>Modularity |

| Special-<br>purpose<br>communications<br>products | Adaptability*<br>Supplier stability*<br>Architecture<br>Resilience                             | Price*<br>Power*<br>Flexibility*<br>Expandability*<br>Modularity*                               |

| Minicomputers                                     | Price*<br>Power*<br>Flexibility<br>Expandability<br>Adaptability<br>Architecture<br>Modularity | Supplier stability*<br>Resilience*                                                              |

\*Debatable point

Figure 1.9

Advantages and disadvantages of four main classes of equipment used in communications systems

-general-purpose mainframes such as the IBM 4341 or ICL 2960;

-small business computers such as the IBM System/34 or ICL 2903;

---special-purpose communications products like the IBM 8100, Univac UTS-700, or Burroughs B776; and

-minicomputers such as the DEC PDP-11/34, Prime 100, or DG NOVA.

Figure 1.9 summarizes the major benefits and disadvantages of each approach in general terms. Although this represents the authors' subjective assessment, it is based upon practical experience with all four categories. For specific systems it

may be necessary to give certain criteria much heavier weighting (for instance, need for a single supplier), which may in turn downgrade the importance of some deficiencies.

The general criteria used should be interpreted as follows:

*—Price:* The price the customer has to pay for a typical configuration of the right scale for the job.

*—Power:* The processor power (not just speed), storage capacity, and throughput capability (not the same as processor power) provided for the price.

*—Flexibility:* How rigidly structured the system is in both hardware and software terms. Can alternative supplier terminals be attached easily?

*—Expandability:* How easily the capacity of the system can be increased and how small the increments are.

*—Adaptability:* How easily the system can be adapted to meet precise application needs. Conversely, does the application need to be changed to fit the system component?

*—Supplier-stability:* Whether the supplier (manufacturer or agent) is going to be around to support the system through the whole of the project life.

*—Architecture:* Whether the architecture (particularly the I/O and interrupt structure) is relevant to a data communications environment. How about the software?

*—Resilience:* How proven and stable are the hardware and software being used?

*—Modularity:* How modular is the system? (The modularity of a system contributes to its failsafety as well as its flexibility, expandability, and adaptability.)

General-purpose mainframes are included in figure 1.9 as a reference point (usually only in the largest networks are they considered possible concentrators and so on). Most small business computers (SBCs) are made by the same companies that make the medium to large mainframes. Perhaps for this reason SBCs tend to be structured like scaled-down mainframes. This is not true of minis, which although ostensibly smaller than mainframes often have greater throughput, particularly in communications-related jobs. In other words, the architectural differences can be much more important than those of processor power. Today, "mini" is used to describe the type of computer, not its power or size. Most special-purpose communications products were developed by the mainframe companies in response to the threat of minis in the teleprocessing field. Although these products boast architectures more relevant to communications tasks, they tend to lack both flexibility and adaptability.

# **Problem Areas**

Our aim is not necessarily to promulgate the virtues of minicomputers in data communications. On the contrary, there seems to be something of a bandwagon effect stimulated by the all-too-clear advantages that minis sometimes have over alternative solutions. This enthusiasm ignores many of the pitfalls that can threaten the success of a project, and it is on these problem areas that much of our text will concentrate. This will be done in a positive way; not only will the danger areas be identified, but possible alternative solutions (where they exist) will be expounded.

Problem areas may be summarized as follows:

-processor overheads associated with communications I/O

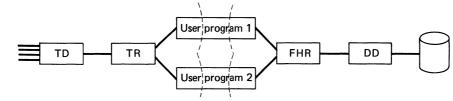

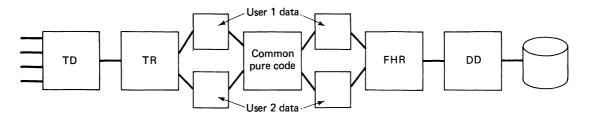

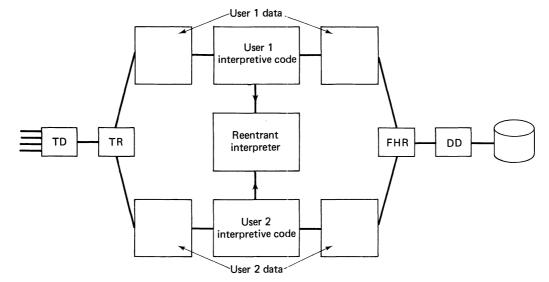

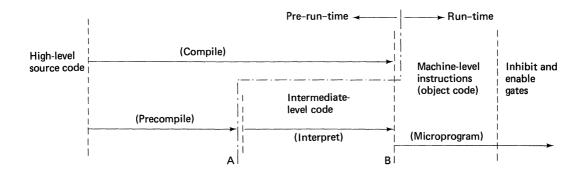

-peripheral switching and sharing

-suitability of instruction sets for commercial applications

-disc storage access times

-file access methods and shared file support

-hardware and software failsafety features

-operating system structures

-multitasking

----storage management

-programming languages

-macrocode or microcode?

---addressing problems and the

-use of specialized packages

Although our review of the way minicomputers are being used in data communication systems has been comprehensive, it is clear that many new roles will be found for minis as the capabilities of these compact but flexible processors increasingly become understood by systems designers.

# References

Davis, D. W. and Barber, D. L. A. Communications Networks for Computers. London: John Wiley, 1973.

Healey, M. Minicomputers & Microprocessors. London: Hodder & Stoughton, 1976.

- Hebditch, D. L. Data Communications: An Introductory Guide. London: Paul Elek, 1975.

- Martin, J. T. *Telecommunications and the Computer*, 2nd ed. Englewood Cliffs, N.J.: Prentice-Hall, 1976.

- United Kingdom Post Office. *Handbook of Data Communications*. Manchester: NCC Publications, 1975.

# 2

# The Minicomputer: Technology and Architecture

# What Is a Minicomputer?

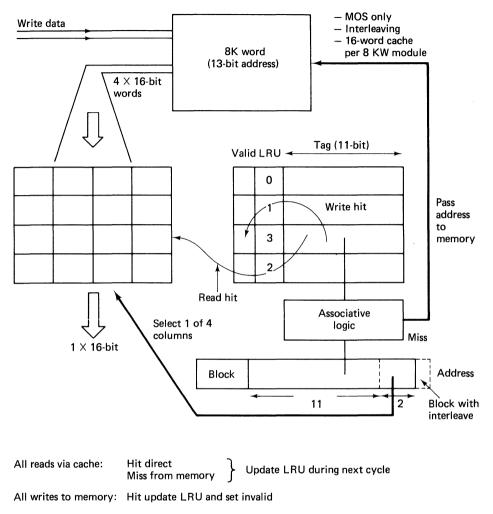

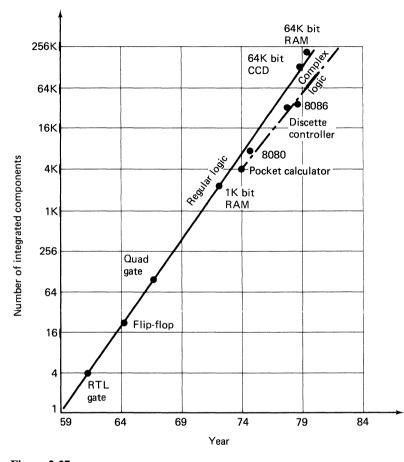

Before 1976 a minicomputer was simply a small computer made by a specialized company (see figure 2.1). These machines were marketed to "other equipment manufacturers" (OEMs) for inclusion in larger products, such as the controllers in petrochemical plants. Essentially they were merely sophisticated components. Technological advances were largely limited to hardware, with software lagging far behind. The cost-effectiveness of the mini also appealed to universities and other research institutes, which helped to widen the range of available software and—more importantly—served to spread the word. Commercial data processing users were still relatively unimpressed: the software was barely adequate for specialist researchers and engineers, let alone the "end-user" oriented DP men who required an easy to use, easy to understand system that would not distract them from the real problems of processing business data. The mini was, however, a most useful component in a data communications system and as such was first brought to the attention of the DP fraternity.

By 1976 the scene had changed. Healthy sales in the OEM area had sponsored continuing development of software systems and rapidly advancing hardware technology was being incorporated into the product. The OEM discount system developed for engineering and instrumentation users was available to companies building small business computer systems and to software houses. With a mainframe computer the end user is serviced by the manufacturer, with the software house doing add-on work. With a mini, the software house can expand its image into a turnkey systems house, dealing directly with the end user, selecting a specific mini on behalf of its client, and getting a discount on the hardware. Suddenly minis were a success in commercial data processing.

While the marketing aspects show a clear differentiation between minis and mainframes, there are also technological differences. An overriding feature is

| 1957      | Digital Equipment Corporation (DEC) manufactures circuit boards/<br>modules for testing and laboratory automation.                                  |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 1959      | DEC PDP-1: first programmed processor-\$120,000. For graphics displays, message switching, instrument control, process control.                     |

| 1960-1962 | Special 'aerospace' small computers (Burroughs D210, Hughes HCH 20L, Univac Add-1000)                                                               |

| 1965      | DEC PDP-8, first true mini-\$20,000.                                                                                                                |

| 1966      | PDP-8S; first 4K word computer under \$10,000. Interdata and Varian enter market.                                                                   |

| 1968-1969 | LSI becomes available. 16-bit minis introduced (PDP-11). Hewlett<br>Packard, General Automation, Computer Automation, Data<br>General enter market. |

| 1970      | 40-50 vendors active.                                                                                                                               |

| 1971      | Memory management extends physical address space.                                                                                                   |

| 1972      | Serious use of minis in data processing; full range of peripherals supported.                                                                       |

| 1973      | Intel 8080 microprocessor introduced. 32-bit Interdata and SEL machines.                                                                            |

| 1975      | Altair introduces \$100 bus microcomputers.                                                                                                         |

| 1976      | Prime virtual operating system introduced.<br>Honeywell back with Level 6.                                                                          |

| 1977      | IBM Series 1. Tandem multi-processor system.                                                                                                        |

| 1978      | DEC VAX 11/780                                                                                                                                      |

| 1979      | 16-bit microprocessors available (8086)                                                                                                             |

# Figure 2.1 Evolution of minicomputers

versatility. The mini is designed to be used in a wide variety of applications—not only commercial data processing—with OEM customers adding their own external equipment. Further, bearing in mind its historical development as a process control computer, the mini is designed for "real-time" applications. In process control external events must be serviced on a priority basis, as they occur, not when the computer can schedule service. Other events must be time initiated, for example, read an analog-to-digital converter every 100 milliseconds. Thus the concept of an interrupt, used in mainframe computers only for major events such as errors or completion of block data transfers, has been refined to accept interrupts from such trivial events as single keystrokes on a terminal keyboard. Interrupt servicing overheads have been brought down to as low as 10 to 30 microseconds. This feature adds a whole new dimension to the techniques of terminal-based data processing systems which we will examine in detail. Five years ago a mainframe computer produced a relatively high level of performance by using sophisticated architectural techniques. Nowadays an equivalent performance can be achieved using a comparatively simple (and cheap) minicomputer architecture, merely by employing the faster electronic components readily available, aided by microprocessor controlled input/output channels. Thus the "small" constraint of the mini has largely disappeared with machines like the PDP-11/70 and MODCOMP IV, matching small mainframes like the 370/125 and yet retaining their superior terminal handling characteristics and cost effectiveness.

The leading mini maker is Digital Equipment Corporation (DEC), which in 1977 became the second largest computer manufacturer (after IBM) in terms of annual revenue, topping Honeywell and the rest. The other major mini specialists are Data General and Hewlett-Packard, with Texas Instruments in a very powerful position as the leading component manufacturer. Figure 2.2(a) is a list of the leading companies in the United States and Europe. Note that with its Series 1 IBM joined the list in 1977 and that Honeywell, long established in the mini field, has renewed flagging interest with its Level 6. Univac has bought in via Varian Data Machines. The other traditional DP computer suppliers, Burroughs and NCR, have simply called their latest small business computers (the B80/90 and 8200) minis, but in no way do these machines possess the general-purpose. versatile I/O and software necessary for the range of interactive applications considered here. They are nevertheless good terminal-oriented small business computers in competition with many other suppliers, some of which are listed in figure 2.2(b). Note that some dedicated SBCs incorporate OEM minis (the older Nixdorf 8870 with a Data General NOVA). The mini manufacturers also package their own machines into small business systems such as Computer Automation Inc.'s SyFA and DEC's COS 300 and 500 range. Some new mini products are aimed directly at the growing commercial systems market. These include the Data General ECLIPSE and Hewlett-Packard 3000.

The bottom end of the business computer systems market has been serviced by glorified accounting machines with data stored on magnetic stripes on a ledger card. These visible record computers (VRCs) are now being superseded by terminal-based systems using floppy discs as random-access bulk data stores. Minis can be used in such systems, but here the microprocessor is the dominant device. The microprocessor is simply a small CPU fabricated on a single silicon chip, which is used to build a dedicated processor. Micros are already being used in intelligent terminals and as I/O channel controllers on bigger computer systems. As micros become more powerful, they will form the heart of the next generation of "minis"; our comments are thus equally relevant to today's minis and tomorrow's micros. Possibly new names will be added to the lists in figures 2.1 and 2.2—such as Zilog and Intel—and many of those listed will be absorbed or amalgamated as the vibrations caused by the drastic cost reductions in computer hardware impinge on the fortunes of computer systems suppliers. Large-scale integration and microprocessors are discussed later in this chapter.

| European                                                                                                                                                             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Digico<br>Ferranti<br>GEC (UK)<br>Nord<br>Philips<br>SEMS (Telemechanique/CII)<br>Siemens                                                                            |

| Kienzle<br>Lockheed<br>Mohawak Data Services (MDS)<br>NCR<br>Nixdorf<br>Olivetti<br>Ontel<br>Philips<br>Raytheon<br>Reality (CMC)<br>Triumph-Adler<br>Univac<br>Wang |

|                                                                                                                                                                      |

Figure 2.2 Leading manufacturers. (a) Minicomputer manufacturers (b) Small commercial data processing systems

To illustrate the size of the minicomputer market it should be noted that by 1978 Digital Equipment had supplied over 40,000 each of its PDP-8 and PDP-11 models. These machines are sold rather than rented, which means that with strong competition, each supplier must continually strive to improve his product, absorbing any new technology as soon as possible. Contrast this with the

constraints imposed on the traditional computer suppliers by the existence of rented systems. If IBM makes significant improvements to the System/34, it will obsolete the System/3 too soon; rented System/3s would then be returned, since the new IBM product is competing with the old IBM product as well as those of other manufacturers. Inside IBM this situation is complicated by the Series 1 minicomputer. It is now possible to buy an IBM 3780 from IBM's Data Processing Division, or a Series 1 with 3780 emulator from its General Products Division!

This chapter is a review of typical minicomputer hardware.

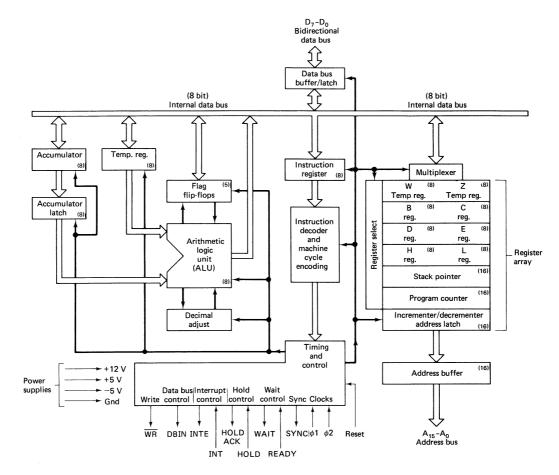

# Architecture

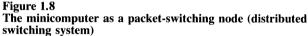

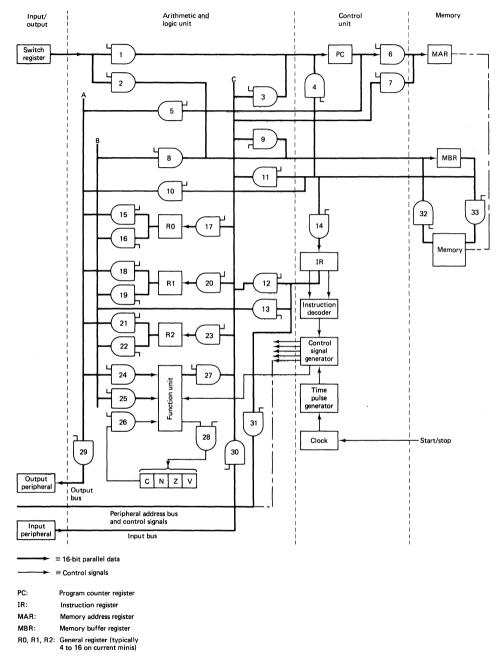

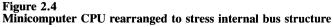

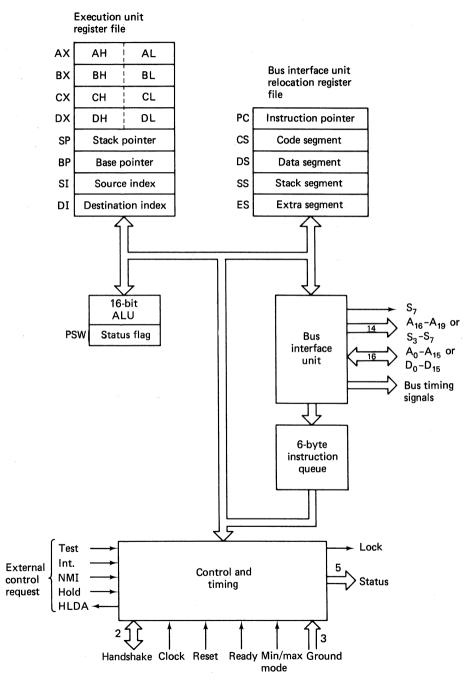

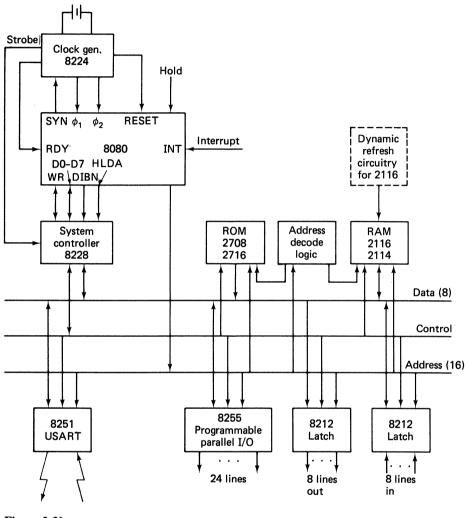

#### The Processor

The processor of a "typical" minicomputer is shown in schematic form in figure 2.3. All operations and data transfers occur in bit-parallel sequence. Figure 2.4 is the same machine rearranged to stress the internal bus structure. The standard word length is 16 bits, although 8, 12, 18, 24, or 32 may be encountered. Typical memory cycle times lie between 500 nanoseconds and 2 microseconds, although it must be stressed that this is only one factor affecting the overall speed of a machine. The number of program-usable registers varies from 1 to 16, excluding the essential program counter, instruction, memory address, and memory buffer registers. Seldom are all registers generally available to the programmer because of constraints placed on the instruction set by the limited word length.

In the simplest machine the single register functions as an accumulator, all other data being retained in memory. Most machines have at least a second register which is used as an index or base in memory addressing. Further registers are used as multiple indexes and extensions of active word length, for instance, two registers to store the 32-bit product of two 16-bit numbers. If registers primarily used as index registers are generally accessible they may be used as scratch-pad registers. The control and status flags (carry, overflow, zero, negative, and so on) are commonly grouped into one effective register which may be stored and restored in multitasking applications. The instruction length is often effectively increased by special flags such as a single- or double-length data indicator.

Byte operations use the same registers, with specific treatment of the other half word dependent upon the operation (sign extended, zeroed, and so forth). All arithmetic and logic operations are performed by the arithmetic and logic unit (ALU), which incorporates shifting operations. The ALU may also be used during an instruction execution to calculate effective memory addresses. The condition flags are set as a result of the last operation performed by the ALU (except address calculations) so that conditional branching is executed by testing the appropriate combination of flags. Thus a compare instruction is a subtract in which the result is ignored, but the condition flags are set.

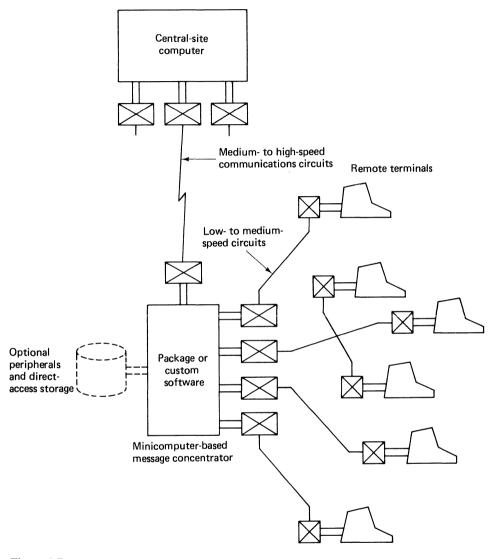

Figure 2.3 A typical minicomputer central processor

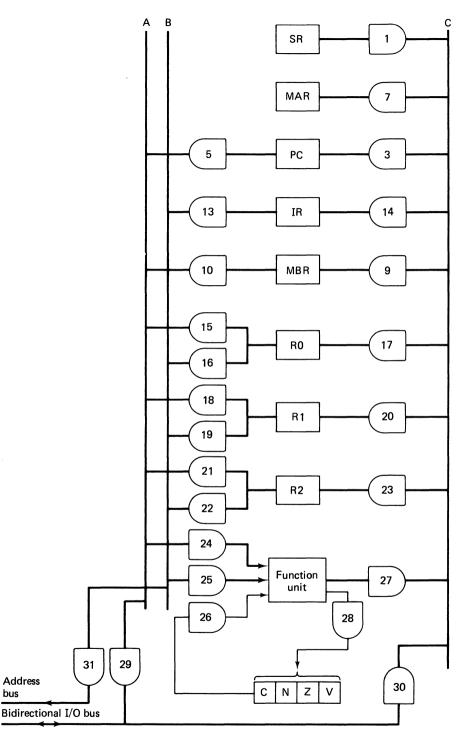

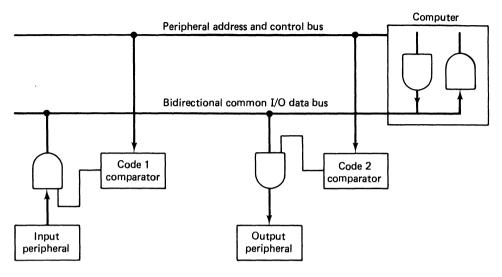

# **Bus Structures**

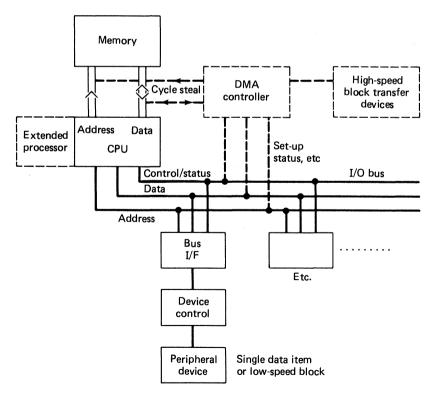

Data is communicated between units of the computer along a bus or data highway. The usual arrangement, shown in figure 2.5, employs a number of buses for specific interconnections. Two buses are normally required to connect CPU with memory and CPU with peripherals. Each bus must comprise sufficient wires to transmit data—addresses, control, and test information—in both directions. Often the logic is organized to use the same wires for sending and receiving data (bidirectional), taking advantage of the fact that both will never be required simultaneously. A typical I/O bus will use up to 64 wires.

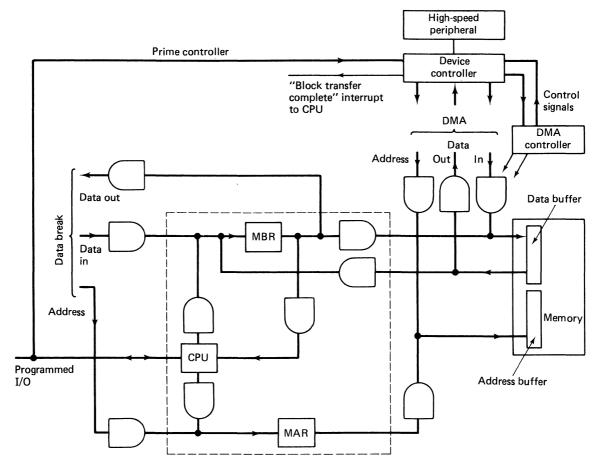

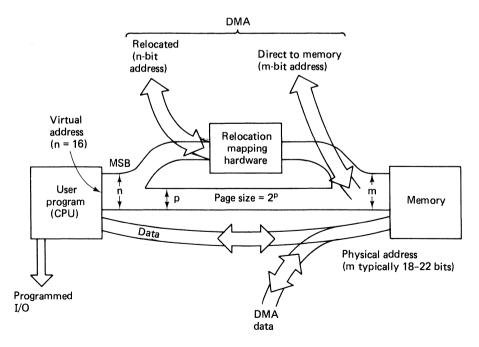

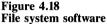

A technique pioneered in the PDP-11 is the single bus shown in figure 2.6. In this case the peripherals are treated as specific "memory" locations (virtual I/O), avoiding specialized I/O operations. Data can be passed direct from one peripheral to another as simply as from one memory location to another. Direct memory access is similarly performed. The apparent simplicity of this technique is offset by the extra logic and time required to give appropriate allocation of the bus. The single data highway is also an obvious bottleneck, setting a top limit on

Figure 2.5 A typical minicomputer with separate memory and I/O buses

Figure 2.6 Single bus system

performance. Many microcomputer systems use a simple version of a common memory and I/O bus, called the S100 (Altair, North Star Horizon, Cromemco).

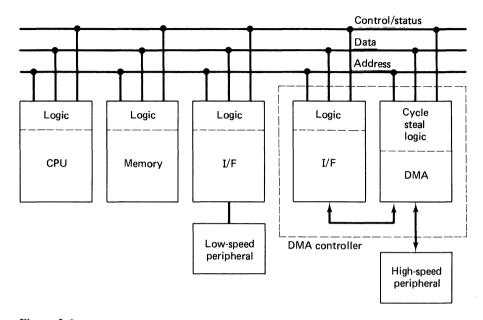

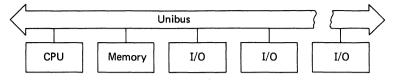

Some machines, such as the GEC 4000, feature as options a more complex architecture involving a number of multiplexors to route data between CPU, memory, and peripherals. The bottleneck in the single bus system is reduced by allowing more than one multiplexor and employing multiport memory (figure 2.7). This it should be noted is a multibus mini when only the basic multiplexor is used, but resembles a mainframe when I/O processors (channels) are configured.

Inside the CPU, instructions may be of differing lengths, for example, for the PDP-11, move register to register is 16 bits, move memory contents to register 32 bits, and move memory contents to memory 48 bits; the latter two instructions incorporate 16-bit addresses. The memory however is addressed by the 16-bit word, with a 16-bit data highway, so that the effective 48-bit instruction requires three memory accesses (to consecutive locations). Some machines feature 8-bit highways, with most instructions requiring multiple memory accesses (8080/Z80/6800/6502 microprocessor based machines), while some of the more recent machines feature 32-bit highways (Interdata 8/32). Thus a machine may feature a double-precision floating point (64-bit) multiply instruction, which will multiply the number stored in four consecutive memory locations by a number stored in a 64-bit internal register (usually four standard internal registers treated as one for this instruction). The 16-bit machine requires four-memory accesses for the one data word.

Figure 2.7 Advanced system with active I/O

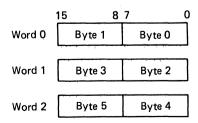

In most minicomputers the memory is organized in 16-bit words numbered evenly. Odd-numbered addresses then refer to the 8-bit byte, as shown in figure 2,8. Without this feature byte manipulation can only be performed by fetching the full word and masking and/or swapping half words inside the processor. Thus most minis have a virtual address space of 64 KB, but a few with word addressing have a 128 KB (64 KW) space.

### Memory

Magnetic core and semiconductor (MOS) memory were both common in minicomputers, although MOS now dominates. Most processors take advantage of the read/write nature of core to execute some instructions, as when incrementing is performed in a read/modify/write mode. Thus mixing core and semiconductor memories raises problems. The solution is to use a different bus interface for the semiconductor memory with additional logic to emulate the read/modify/write mode for the appropriate instructions. Most machines use asynchronous transfers between CPU and memory so that alternative speed memories are offered for the same basic processor.

Memory was traditionally supplied in units of 4K 16-bit words, but 32 and 64KB blocks are now common. Read-only memory (ROM) is available on some machines but is used only in rare cases. The common exceptions are bootstrap loaders and microprograms discussed later. Multiport memory (figure 2.7), sometimes available as an option, allows simultaneous block transfer through one port and normal program access through another. Otherwise cycle stealing is employed, as is discussed below.

# **Instruction Sets**

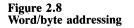

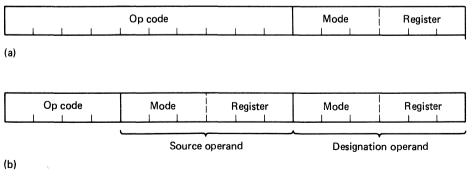

In most machines the instruction set can be broken into three categories: memory reference, nonmemory reference, and input/output. A simple instruction arrangement, using a 4-bit operation code (or order), is shown in figure 2.9. This setup allows 14 memory reference instructions. The logical allocation of the bit significance is seldom so straightforward in practice.

### Memory Reference Instructions

Most machines use single-operand instructions, as in figure 2.9 (a), the second operand (when needed) being a CPU register. Often only the accumulator may be used, but if a choice of register is allowed the operation code must specify which. The combination of the mode bits and the "displacement" D are used to locate the specified memory cell, as discussed below. The location following the instruction is occasionally used to store a 16-bit literal or an indirect address, effectively extending D.

The PDP-11 is a notable exception to the above rule, since it allows some double-operand instructions such as move contents of one memory location to another, as shown in figure 2.10. Three bits are used to specify one of 8 modes, and another 3 bits one of 8 registers, one of which is the program counter (PC). For each operand the selected register is either the actual operand location or a pointer to a memory location, depending on the mode. Offsets and literals are stored in locations following the instruction. Thus MOV R1, R2 occupies one word, MOV R1, A two, and MOV A, B three words. This multiword technique

26

has now been adopted by Texas Instruments and IBM. Interdata and others use multiwords to achieve an effective 32-bit machine. Single-word-instruction machines are simple and ideally suited to earlier minis, but are limiting on newer machines. Thus, for instance, Data General have employed the NOVA instruction

Figure 2.10 Single- and double-operand instructions in a multiword instruction set

set on the ECLIPSE but have used one specific bit pattern to cause the processor to read the next word and treat it as an extended instruction set.

Byte or word data is handled directly. Some machines feature instructions that test or modify specific bits of a word, although this is usually handled with a program employing masking operations. Character-string manipulation instructions are also encountered, for instance, scan a string starting at a pointer set in one register, through a number of characters set in another register, but stop when the data matches the content of a third register. Such instructions have obvious advantages over a programmed loop since only one instruction fetch cycle is required; there are some problems with interrupts, however, since such an instruction may take numerous memory cycles to complete. Other instructions such as byte-string-move and translate do occur but all too infrequently. The IBM Series 1 and Data General ECLIPSE are new machines that support characterstring instructions and this will hasten market-leading Digital Equipment Corporation into producing new versions of the PDP-11 to compete, VAX-11/780 being the first of these machines. In general mini instruction sets are good at binary arithmetic and logic but weak on character handling. Program control operations such as jump and jump-to-subroutine also come under the memory reference category. With a JSR, current PC contents are automatically saved for return; dedicated register or memory locations may be used, or the first word of the subroutine, but stacking offers advantages discussed below.

#### Nonmemory Reference Instructions

This group of instructions contains operations on data stored in the internal registers. Arithmetical and logical operations are grouped with branch and shift instructions. A wide variety of conditional branch instructions are encountered; the branch point may be indicated by a PC-relative displacement in the instruction, but many machines use the skip-type operation. With a skip instruction the PC is incremented by one (two with byte-addressed memory) if the logical condition is met. Otherwise the next instruction in sequence is executed, normally an unconditional Jump. Increment (or decrement)-and-skip-if-zero instructions are used for loop counting. This may also be a memory reference instruction, with the counter stored in memory rather than in a register. Signed integer multiply and divide are always available but often as part of an optional extended instruction set.

Both arithmetic and rotational shift operations are employed, with and without the carry bit. In many machines only a one-place shift can be executed by one instruction; other machines allow shifting by a specified number of places.

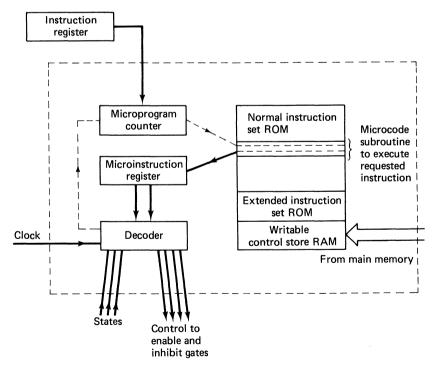

With single-word instruction machines it is usually possible to create some combinations of shift, skip, set, clear, increment, and other operations into one instruction. This assumes that no conflict can arise and the order of execution must be clearly determined to ensure the correct operation of the combined instruction. This technique was referred to as microprogramming in an earlier machine, a word that now has broader connotations, as we will discuss.

#### Input/Output Instructions

All input/output instructions must identify the peripheral device by number. Four types of instructions are needed:

- 1. Read data (peripheral-to-CPU)

- 2. Write data (CPU-to-peripheral)

- 3. Test

- 4. Control

The test and control instructions are required to activate and deactivate devices and to check the current status of a peripheral. The data transfer instruction must also reference a data location in the processor. In the simpler machines a specific register is used, a further register-memory transfer being required to save the data. Alternatively a register can be used as an index to an array in memory.

Single-bus systems do not use special instructions, since peripheral buffers and status/control registers are treated as memory locations and conventional memory reference instructions are used for input/output. This is called virtual I/O.

### Numeric Data

Numeric data can be used in the computer in a number of forms. The basic instructions assume 16-bit integer numbers in 2's complement form. Software routines for double-length (32-bit) integer arithmetic are common, one word forming the most significant half and a second the least significant.

Floating-point representation uses 32 bits, typically a sign, 24-bit unsigned, normalized mantissa (approximately 7 decimal places), and an 8-bit excess 200 exponent. A binary exponent is common ( $x = \pm m.2^{\circ}$ ), so that the normalized *m* always has a 1 in the left-hand bit; hexadecimal ( $x = \pm m.16^{\circ}$ ) is also used when up to three leading zeros are allowed in *m*. Double-precision floating point (64-bit) increases the mantissa to 56 bits, equivalent to about 15 decimal places. Software routines are normally used, but optional floating-point processors are available.

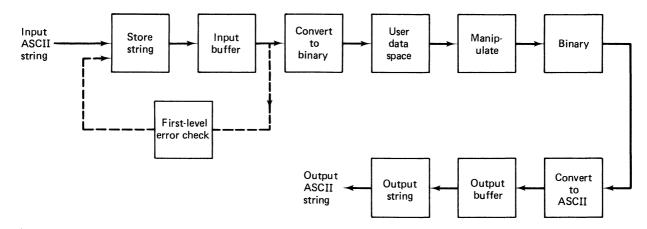

Decimal (BCD) arithmetic is rare in minicomputers although software packages are available for machines used in commercial applications. It is quite common for high-level languages, COBOL for example, to employ ASCII character strings. Most direct arithmetic operations can be used with byte or word data, a flag being set to indicate the specific type. On some machines, bits of the code are used for this purpose while other machines use a separate flag. The latter effectively extends the instruction length and allows more scope, although the flag must be set by a previous instruction. On such machines the same instruction performs differently, depending on the data word-length flag setting. Software routines are always provided to convert ASCII character strings to internal binary representation and vice versa.

Figure 2.11 Human/machine interface to numeric data

Figure 2.11 indicates that all data processing requires human input, for example character strings, conversion to binary, manipulation, and conversion back to character strings. The simpler the internal representation, the simpler the conversion routine. ASCII strings, for instance, only pack the  $\pm$  sign into the least significant character. The simple internal representation is, however, more wasteful of space and takes longer to manipulate. Commercial DP is mostly input and output, while scientific work is nearly all processing. Hence the preference for ASCII (or better, BCD) for the former and floating point for the latter. Double-precision integer with implied decimal point is also suited to commercial work. Simply because of availability, double-precision floating point (8-byte) is commonly used in commercial work on minis; single precision does not have enough significance.

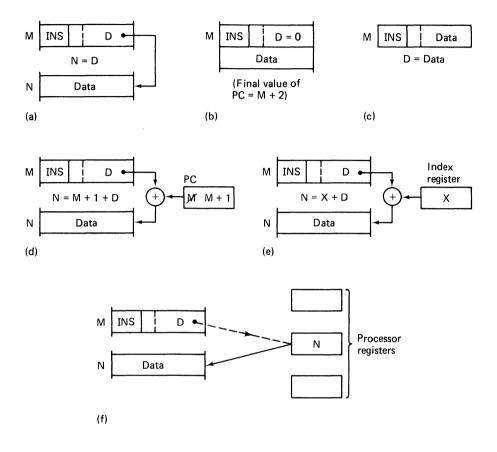

### Memory Addressing

As has been explained, most machines, even though they employ 16-bit data highways, are capable of addressing individual bytes in memory. With a 16-bit word this sets a limit of 64K bytes. Any bit operations must be executed by fetching the appropriate byte and and decoding this under program control in the CPU. The addressing modes encountered are here discussed with reference to figure 2.9(a). One bit of the mode is used as a direct/indirect flag, others for various modes. Not all the following modes will be found in one machine, but they cover the range. They are summarized in figure 2.12.

### Direct/Indirect

For direct addressing the information is stored at the indicated location; for indirect addressing the indicated location contains the address of the location of the required information. An extra memory access is involved for indirect addressing, which is typically used for array processing, the content of the addressed location being incremented each time.

#### Absolute or Page Zero

The displacement, D, is treated as the actual address. Since D is typically about 8 bits long, only 256 locations can be addressed. On most machines this is the first 256 bytes, but on others it is the first 256 data items, particularly in machines with a separate data type flag; thus for byte data D refers to the first 256 bytes, while for double-precision floating point data the first 256  $\times$  8 bytes are referenced.

### Immediate

The actual data is in the location following the instruction.

#### Figure 2.12 Some common addressing modes

#### Literal

D is the actual data. Note that the use of "immediate" and "literal" terminology on minis conflicts with such usage on some mainframe computers.

### Program Counter Relative

D is treated as an offset, and is added to the PC contents to give the memory address. Sometimes D is treated as a positive integer and at other times as a signed integer, allowing back-referencing. This mode is the most common since it creates relocatable code.

### Indexed or Base Relative

D is added to the contents of a specified register to give the memory address. This is used for working with arrays. If D is kept constant and the register contents

incremented, it is termed indexed mode, while if D is varied and the register contents kept constant it is termed base relative mode. There is no difference in general except where indirect access is used, in which case the register points to a memory location, the contents of which are added to D to give the required address, and the register is clearly being used as a base pointer and D as an index. One General Automation machine allows both a base and an index register, so that D is added to the base register contents to find the base pointer to which the contents of the index register are added to give the desired address, a twodimensional array technique.

#### Auto-Increment, Auto-Decrement

With these modes the index register contents are incremented or decremented after each operation. They must be a true pair in the sense that they must increment *after* the address has been used (postincrement) and decrement *before* the address is used (predecrement), or vice versa. These modes are used in creating stacks and for working through lists. All registers in the PDP-11 can be used for auto-increment/auto-decrement but most machines only use a specific register. In all machines certain operations (JSR) use one register by default, often called the *stack pointer*.

Stacking is probably the best way of entering a subroutine. On excuting a JSR instruction, the PC contents and any other critical register contents can be placed on the stack (pushed) by successive auto-increment mode move instructions; on return, the auto-decrement mode move instructions in reverse order reinstate (Pop) the CPU conditions. Subroutine calls can now be nested, since this creates a "last-in, first-out" stack. Stacking can also be used to create reentrant code by ensuring that all data is separated from the code and that pointers to the data are stacked with the JSR routine.

#### Pointer or Register Indirect

The contents of a selected register form the address required. This technique is used extensively with machines like the PDP-11 and TI 990 when D becomes the register pointer. This is combined with such techniques as indirect addressing and indexing to produce a very versatile addressing system. It is very common in microprocessors.

# **Input/Output**

### Programmed I/O

The normal I/O instructions have been mentioned. Each peripheral device requires an interface to communicate between the I/O bus and the device itself. A simple system is shown in figure 2.13. Since a peripheral is essentially slower

Figure 2.13 A simple party-line I/O bus system

than a processor, some means of checking the status of the device must be provided. At the simplest level a busy flag is required, set to 1 while the peripheral is active. The processor repeatedly tests this flag until it clears, when a new data transfer can be initiated.

### Interrupts

The approach described above means that the processor is continually waiting for the peripheral to complete. To overcome this problem it is common to use an interrupt system. The peripheral action is initiated by the processor, which then proceeds with another task. When the peripheral has completed, its busy flag is cleared and a done flag is set; no further action can be initiated until the done flag is cleared, usually automatically by the next data transfer. The setting of the done flag causes a request for an interrupt to the processor. The processor checks the priority of the interrupt and if it is higher than the current task (and any other peripherals which have requested interrupts), the current task is shelved and the device serviced. The task of shelving a program is similar to a JSR, except that it may occur anywhere in a program. Stacking is thus an advantageous technique in handling interrupts.

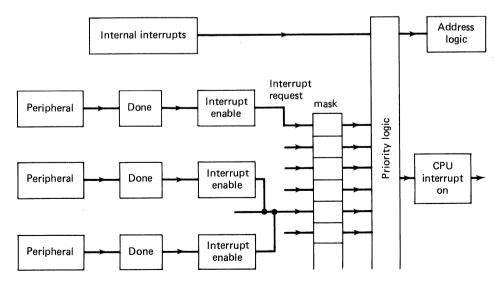

The interrupt system must handle two problems. It must determine which peripheral requested the interrupt, and then establish a priority for the interrupts (for example, a Teletype must not be allowed to interrupt a high-speed analog-to-digital converter).

Two techniques dominate the servicing of interrupts.

*Software Polling*. When an interrupt request is accepted, a routine is entered causing each peripheral in turn to be tested until the one awaiting service is detected. The order in which the devices are polled forms a priority system. When the interrupting device has been identified, the interrupt service routine references a table which it uses to pass control to the appropriate device service routine.

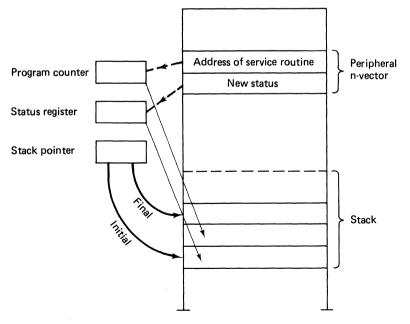

Vectored interrupts. A specific memory location is physically associated with each possible interrupt requesting device as shown in figure 2.14. When an interrupt is requested, if it is of high enough priority (it may wait in a queue), the program currently executing will be interrupted. As with a JSR, the PC and active register contents must be saved for return from the interrupt service, and the service routine entered. If the start address of the routine is previously stored in the memory location dedicated to the peripheral, then this can be copied automatically into the PC. As with subroutine calls, stacking allows simple nesting of interrupts. This technique is much faster than polling. The stack is simply popped back into the PC and status register to complete the return from the service routine. Alternative vectoring techniques relate a vector location to each priority level rather than to each device. Another technique forces the vector location with no overheads (for example, increment a counter; a JSR instruction effectively vectors to a normal service subroutine).

Figure 2.14 Vectored interrupt structure

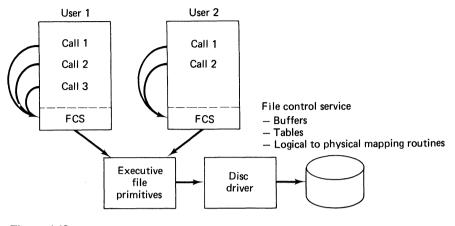

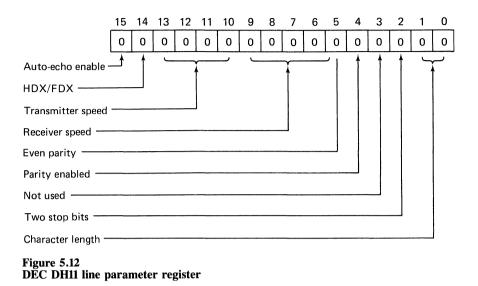

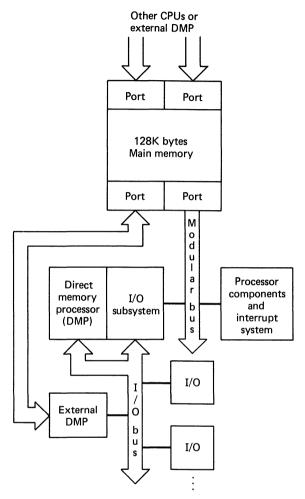

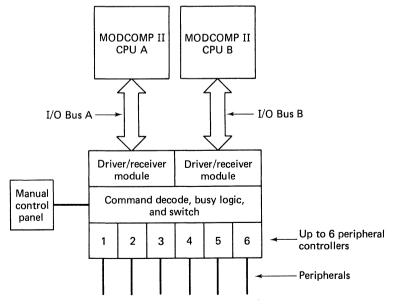

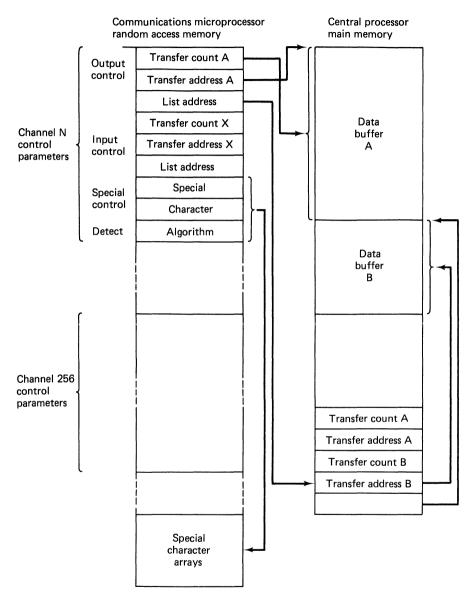

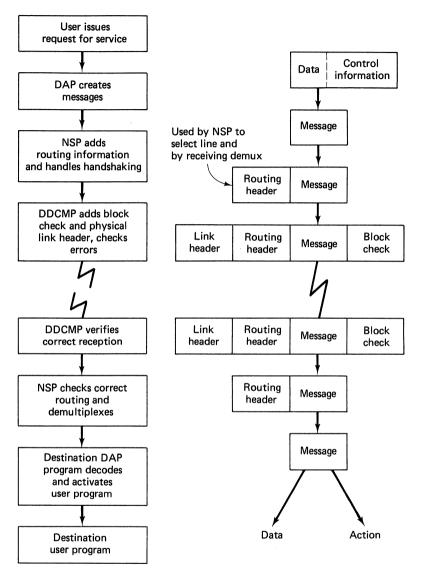

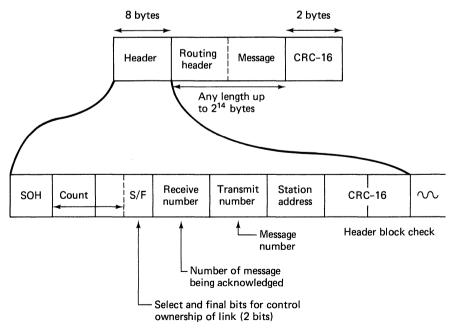

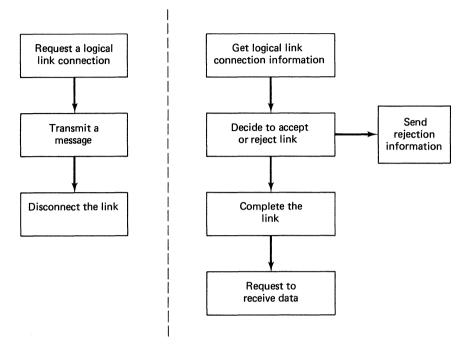

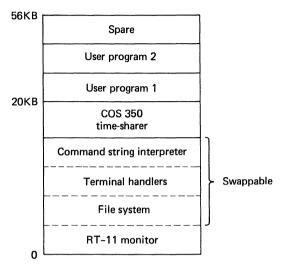

### **Priority**