## ISA System Architecture

## Third Edition

MINDSHARE, INC.

Tom Shanley and Don Anderson

Edited and Revised by John Swindle

#### Addison-Wesley Publishing Company

Reading, Massachusetts • Menlo Park, California • New York Don Mills, Ontario • Wokingham, England • Amsterdam Bonn • Sydney • Singapore • Tokyo • Madrid • San Juan Paris • Seoul • Milan • Mexico City • Taipei Many of the designations used by manufacturers and sellers to distinguish their products are claimed as trademarks. Where those designations appear in this book, and Addison-Wesley was aware of a trademark claim, the designations have been printed in initial capital letters or all capital letters.

The authors and publishers have taken care in preparation of this book, but make no expressed or implied warranty of any kind and assume no responsibility for errors or omissions. No liability is assumed for incidental or consequential damages in connection with or arising out of the use of the information or programs contained herein.

Library of Congress Cataloging-in-Publication Data

ISBN: 0-201-40996-8 Copyright © 1995 by MindShare, Inc.

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of the publisher. Printed in the United States of America. Published simultaneously in Canada.

Sponsoring Editor: Keith Wollman Project Manager: Eleanor McCarthy Production Coordinator: Deborah McKenna Cover design: Barbara T. Atkinson Set in 10 point Palatino by MindShare, Inc.

1 2 3 4 5 6 7 8 9 -MA- 9998979695 First printing, February 1995

Addison-Wesley books are available for bulk purchases by corporations, institutions, and other organizations. For more information please contact the Corporate, Government, and Special Sales Department at (800) 238-9682.

This book is dedicated to the numerous engineers and programmers who contributed to this work unknowingly by asking tough questions during Mind-Share seminars. These questions led us to a far greater understanding of ISA architecture and made this book more complete.

## Contents

| Foreword xxiii                                                    |  |

|-------------------------------------------------------------------|--|

| Acknowledgmentsxxv                                                |  |

| About This Book                                                   |  |

| The MindShare Architecture Series1                                |  |

| Organization of This Book2                                        |  |

| Who This Book Is For2                                             |  |

| Prerequisite Knowledge2                                           |  |

| Documentation Conventions                                         |  |

| Hex Notation3                                                     |  |

| Binary Notation                                                   |  |

| Decimal Notation                                                  |  |

| Signal Name Representation3                                       |  |

| Identification of Bit Fields (logical groups of bits or signals)4 |  |

| We Want Your Feedback4                                            |  |

| Overview                                                          |  |

| System Kernel                                                     |  |

| Memory Subsystems                                                 |  |

| ISA Subsystem7                                                    |  |

| Origins of ISA7                                                   |  |

| The IBM PC7                                                       |  |

| The IBM PC/AT8                                                    |  |

| The ISA Concept                                                   |  |

| Part 1: The System Kernel                                         |  |

## Chapter 1: Intro to Microprocessor Communications

| Chapter 1. millo to millioprocessor communicatio   | 113 |

|----------------------------------------------------|-----|

| Instruction Fetch and Execution                    |     |

| General                                            |     |

| In-Line Code Fetching                              |     |

| Reading and Writing                                |     |

| Type of Information Read from Memory               |     |

| Type of Information Written to Memory              |     |

| The Buses                                          |     |

| The Address Bus                                    |     |

| Control Bus – Transaction Type and Synchronization |     |

| The Data Bus — Data Transfer Path                  |     |

|                                                    |     |

## ISA System Architecture

| Chapter 2: Introduction to the Bus Cycle               |      |

|--------------------------------------------------------|------|

| Introduction                                           | . 21 |

| Automatic Dishwasher – Classic State Machine Example   |      |

| The System Clock – a Metronome                         |      |

| Microprocessor's Bus Cycle State Machine               |      |

| Address Time                                           | 24   |

| Data Time                                              |      |

| The Wait State                                         |      |

| Chapter 3: Addressing I/O and Memory                   |      |

|                                                        | -    |

| Evolution of Memory and I/O Address Space              |      |

| Intel 8080 Microprocessor Address Space                |      |

| 8086 and 8088 Microprocessor Address Space             |      |

| 286 and 386SX Address Space                            |      |

| 386DX, 486 and Pentium Processor Address Space         |      |

| Memory Mapped I/O                                      |      |

| The I/O Device                                         | .36  |

| Chapter 4: The Address Decode Logic                    |      |

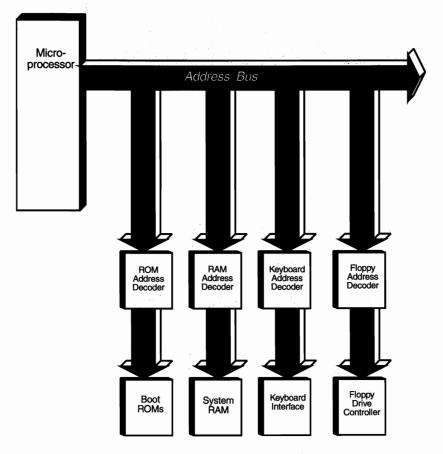

| The Address Decoder Concept                            | . 39 |

| Data Bus Contention (Address Conflicts)                |      |

| How Address Decoders Work                              |      |

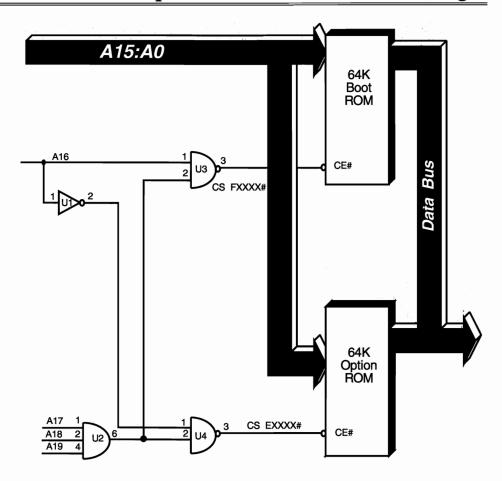

| Example 1– PC and PC/XT ROM Address Decoder            |      |

| Background                                             | .42  |

| The PC/XT ROM Address Decode Logic                     |      |

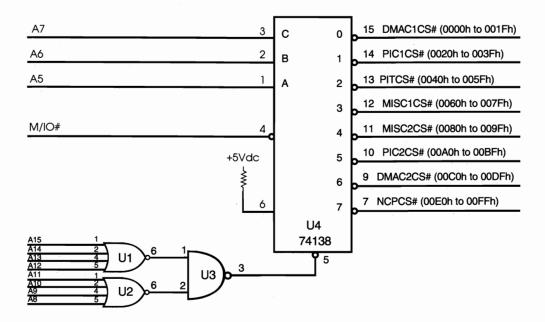

| Example 2 – System Board I/O Address Decoder           |      |

| Chapter 5: The 80286 Microprocessor                    |      |

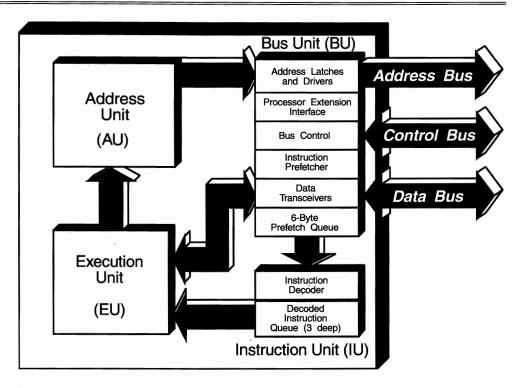

| The 80286 Functional Units                             | 52   |

|                                                        |      |

| The Instruction Unit                                   |      |

| The Execution Unit                                     |      |

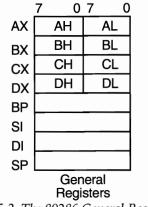

| General Registers                                      |      |

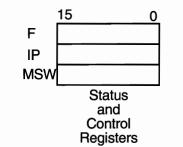

| The Status and Control Registers                       |      |

| The Address Unit                                       |      |

| The Segment Registers                                  |      |

| Segment Register Usage in Real Mode                    |      |

| Code Segment (CS) & Instruction Pointer (IP) Registers |      |

| The Data Segment (DS) Register                         |      |

| The Extra Segment (ES) Register                        | .70  |

| Stack Segment (SS) & Stack Pointer (SP) Registers      | .71  |

| Little-Endian Byte-Ordering Rule                       |      |

| Definition of Extended Memory                          |      |

#### Contents

| Accessing Extended Memory in Real Mode                     | 76  |

|------------------------------------------------------------|-----|

| The Bus Unit                                               |     |

| Address Latches and Drivers                                |     |

| Instruction Prefetcher and 6-byte Prefetch Queue           |     |

| Processor Extension Interface                              |     |

| Bus Control Logic                                          |     |

| Data Transceivers                                          |     |

| 80286 Hardware Interface to External Devices               |     |

| The Address Bus                                            |     |

| How 80286 Addresses External Locations                     |     |

| The Data Bus                                               |     |

| The Cardinal Rules                                         |     |

| Cardinal Rule Number One                                   |     |

| Cardinal Rule Number Two                                   |     |

| Cardinal Rule Number Three                                 |     |

| The Control Bus                                            |     |

| Bus Cycle Definition Lines                                 | 90  |

| Bus Mastering Lines                                        |     |

| Protecting Access To Shared Resource                       |     |

| Ready Line                                                 |     |

| Interrupt Lines                                            |     |

| Processor Extension Interface Lines                        |     |

| The Clock Line                                             |     |

| The Reset Line                                             |     |

| Protected Mode                                             |     |

| Intro to Protected Mode and Multitasking Operating Systems |     |

| Segment Register Usage in Protected Mode                   | 101 |

| Chapter 6: The Reset Logic                                 |     |

| The Power Supply Reset                                     | 107 |

| Reset Button                                               |     |

| Shutdown Detect                                            |     |

| Hot Reset                                                  |     |

| Alternate (Fast) Hot Reset                                 |     |

| Ctrl-Alt-Del Soft Reset                                    |     |

|                                                            |     |

| Chapter 7: The Power-Up Sequence                           |     |

| The Power Supply – Primary Reset Source                    |     |

| How RESET Affects the Microprocessor                       | 115 |

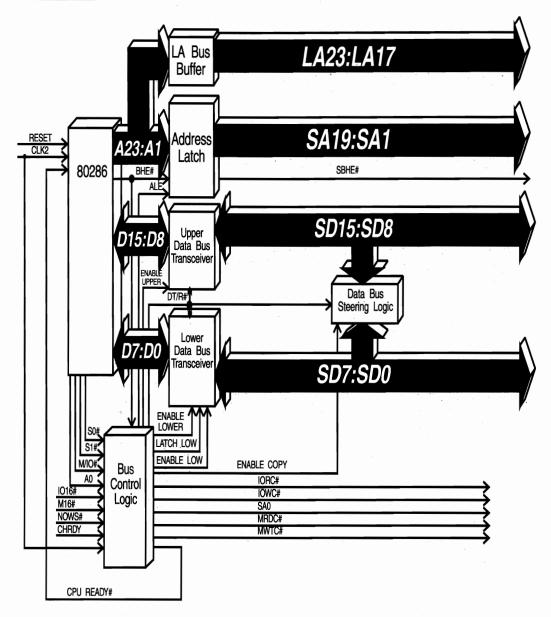

## Chapter 8: The 80286 System Kernel: the Engine

| The Bus Control Logic                                                                                                                                                                                                                                                                                                                                                            |                                                                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| The Address Latch                                                                                                                                                                                                                                                                                                                                                                |                                                                                  |

| Address Pipelining                                                                                                                                                                                                                                                                                                                                                               | 123                                                                              |

| The Data Bus Transceivers                                                                                                                                                                                                                                                                                                                                                        |                                                                                  |

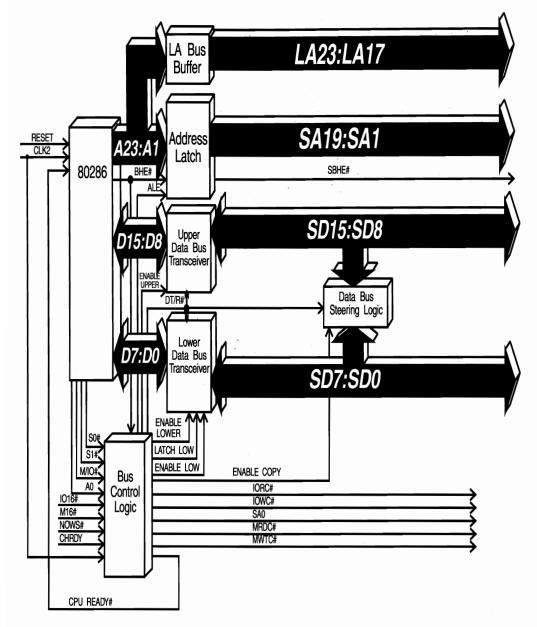

| Data Bus Steering Logic                                                                                                                                                                                                                                                                                                                                                          |                                                                                  |

| Scenario One – Read Even-Addressed Location in 8-Bit Device                                                                                                                                                                                                                                                                                                                      | 128                                                                              |

| Scenario Two – 8-Bit Read from Odd-Addressed Location in 8-Bit Device                                                                                                                                                                                                                                                                                                            |                                                                                  |

| Scenario Three – 8-Bit Write to Odd-Addressed Location in 8-Bit Device .                                                                                                                                                                                                                                                                                                         | 131                                                                              |

| Scenario Four – 16-Bit Write to 8-Bit Device                                                                                                                                                                                                                                                                                                                                     | 132                                                                              |

| Scenario Five – 16-Bit Read from 8-Bit Device                                                                                                                                                                                                                                                                                                                                    |                                                                                  |

| Scenario Six – 8-Bit Read from 16-Bit Device                                                                                                                                                                                                                                                                                                                                     |                                                                                  |

| Scenario Seven – 16-Bit Read from 16-Bit Device                                                                                                                                                                                                                                                                                                                                  |                                                                                  |

| Scenario Eight – 8-Bit Write to 16-Bit Device                                                                                                                                                                                                                                                                                                                                    |                                                                                  |

| Scenario Nine – 16-Bit Write to 16-Bit Device                                                                                                                                                                                                                                                                                                                                    |                                                                                  |

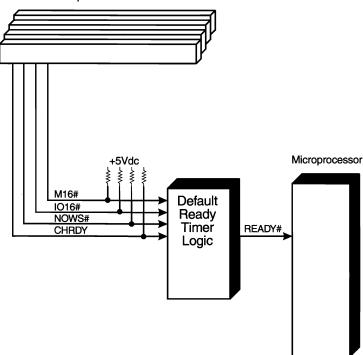

| The Ready Logic                                                                                                                                                                                                                                                                                                                                                                  |                                                                                  |

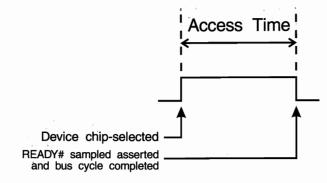

| Access Time                                                                                                                                                                                                                                                                                                                                                                      |                                                                                  |

| Stretching the Transfer Time                                                                                                                                                                                                                                                                                                                                                     | 135                                                                              |

| The Default Ready Timer                                                                                                                                                                                                                                                                                                                                                          | 135                                                                              |

| Custom Ready Timers                                                                                                                                                                                                                                                                                                                                                              |                                                                                  |

| Extending the Default Timing                                                                                                                                                                                                                                                                                                                                                     |                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                  |

| Shortening the Default Timing                                                                                                                                                                                                                                                                                                                                                    |                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                  |

| Chapter 9: Detailed View of the 80286 Bus Cycle                                                                                                                                                                                                                                                                                                                                  |                                                                                  |

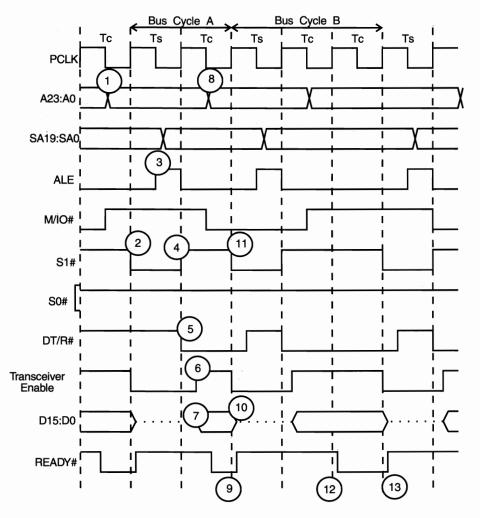

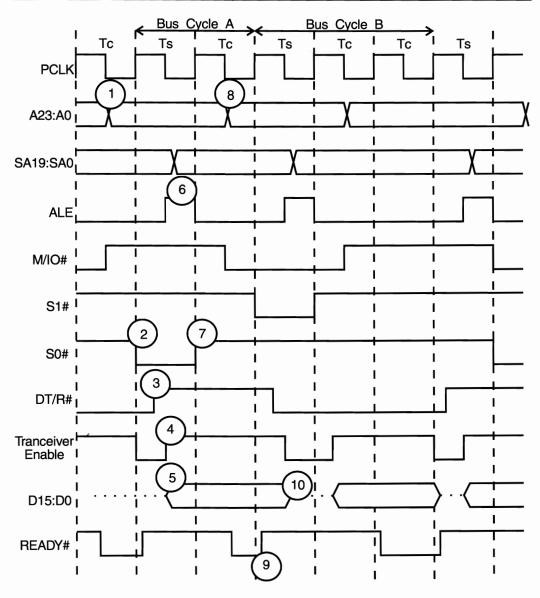

| Chapter 9: Detailed View of the 80286 Bus Cycle<br>Address and Data Time Revisited                                                                                                                                                                                                                                                                                               | 139                                                                              |

| Chapter 9: Detailed View of the 80286 Bus Cycle<br>Address and Data Time Revisited<br>The Read Bus Cycle                                                                                                                                                                                                                                                                         | 139<br>141                                                                       |

| Chapter 9: Detailed View of the 80286 Bus Cycle<br>Address and Data Time Revisited<br>The Read Bus Cycle<br>Bus Cycle A                                                                                                                                                                                                                                                          | 139<br>141<br>144                                                                |

| Chapter 9: Detailed View of the 80286 Bus Cycle<br>Address and Data Time Revisited<br>The Read Bus Cycle<br>Bus Cycle A<br>Bus Cycle B                                                                                                                                                                                                                                           | <b> 139</b><br><b> 141</b><br>144<br>145                                         |

| Chapter 9: Detailed View of the 80286 Bus Cycle<br>Address and Data Time Revisited<br>The Read Bus Cycle<br>Bus Cycle A<br>Bus Cycle B<br>The Write Bus Cycle                                                                                                                                                                                                                    | <b>139</b><br><b>141</b><br>144<br>145<br><b>146</b>                             |

| Chapter 9: Detailed View of the 80286 Bus Cycle<br>Address and Data Time Revisited<br>The Read Bus Cycle<br>Bus Cycle A<br>Bus Cycle B<br>The Write Bus Cycle<br>The Halt or Shutdown Bus Cycle                                                                                                                                                                                  | <b>139</b><br><b>141</b><br>144<br>145<br><b>146</b><br><b>150</b>               |

| Chapter 9: Detailed View of the 80286 Bus Cycle<br>Address and Data Time Revisited<br>The Read Bus Cycle<br>Bus Cycle A<br>Bus Cycle B<br>The Write Bus Cycle<br>The Halt or Shutdown Bus Cycle<br>Halt                                                                                                                                                                          | <b>139</b><br><b>141</b><br>144<br><b>145</b><br><b>146</b><br><b>150</b><br>150 |

| Chapter 9: Detailed View of the 80286 Bus Cycle<br>Address and Data Time Revisited<br>The Read Bus Cycle<br>Bus Cycle A<br>Bus Cycle B<br>The Write Bus Cycle<br>The Halt or Shutdown Bus Cycle<br>Halt<br>Shutdown.                                                                                                                                                             | <b>139</b><br><b>141</b><br>144<br><b>145</b><br><b>146</b><br><b>150</b><br>150 |

| Chapter 9: Detailed View of the 80286 Bus Cycle<br>Address and Data Time Revisited<br>The Read Bus Cycle<br>Bus Cycle A<br>Bus Cycle B<br>The Write Bus Cycle<br>The Halt or Shutdown Bus Cycle<br>Halt                                                                                                                                                                          | <b>139</b><br><b>141</b><br>144<br><b>145</b><br><b>146</b><br><b>150</b><br>150 |

| Chapter 9: Detailed View of the 80286 Bus Cycle<br>Address and Data Time Revisited<br>The Read Bus Cycle<br>Bus Cycle A<br>Bus Cycle B<br>The Write Bus Cycle<br>The Halt or Shutdown Bus Cycle<br>Halt<br>Shutdown.<br>Chapter 10: The 80386 DX and SX Microprocessors<br>Introduction                                                                                          | <b>139</b><br>141<br>144<br>145<br>150<br>150<br>151                             |

| Chapter 9: Detailed View of the 80286 Bus Cycle<br>Address and Data Time Revisited<br>The Read Bus Cycle<br>Bus Cycle A<br>Bus Cycle B<br>The Write Bus Cycle<br>The Halt or Shutdown Bus Cycle<br>Halt<br>Shutdown.<br>Chapter 10: The 80386 DX and SX Microprocessors                                                                                                          | <b>139</b><br>141<br>144<br>145<br>150<br>150<br>151                             |

| Chapter 9: Detailed View of the 80286 Bus Cycle<br>Address and Data Time Revisited<br>The Read Bus Cycle<br>Bus Cycle A<br>Bus Cycle B<br>The Write Bus Cycle<br>The Halt or Shutdown Bus Cycle<br>Halt<br>Shutdown.<br>Chapter 10: The 80386 DX and SX Microprocessors<br>Introduction<br>The 80386 Functional Units<br>General                                                 |                                                                                  |

| Chapter 9: Detailed View of the 80286 Bus Cycle<br>Address and Data Time Revisited<br>The Read Bus Cycle<br>Bus Cycle A<br>Bus Cycle B<br>The Write Bus Cycle<br>The Halt or Shutdown Bus Cycle<br>Halt<br>Shutdown.<br>Chapter 10: The 80386 DX and SX Microprocessors<br>Introduction<br>The 80386 Functional Units<br>General                                                 | 139<br>141<br>145<br>145<br>150<br>150<br>151<br>153<br>154<br>154<br>155        |

| Chapter 9: Detailed View of the 80286 Bus Cycle<br>Address and Data Time Revisited<br>The Read Bus Cycle<br>Bus Cycle A<br>Bus Cycle B<br>The Write Bus Cycle<br>The Halt or Shutdown Bus Cycle<br>Halt<br>Shutdown<br>Chapter 10: The 80386 DX and SX Microprocessors<br>Introduction<br>The 80386 Functional Units<br>General<br>Code Prefetch Unit<br>Instruction Decode Unit | 139<br>141<br>144<br>145<br>150<br>150<br>151<br>153<br>154<br>155<br>155        |

| Chapter 9: Detailed View of the 80286 Bus Cycle<br>Address and Data Time Revisited<br>The Read Bus Cycle<br>Bus Cycle A<br>Bus Cycle B<br>The Write Bus Cycle<br>The Halt or Shutdown Bus Cycle<br>Halt<br>Shutdown.<br>Chapter 10: The 80386 DX and SX Microprocessors<br>Introduction<br>The 80386 Functional Units<br>General                                                 | 139<br>141<br>144<br>145<br>150<br>150<br>151<br>153<br>154<br>155<br>155        |

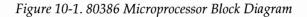

| The Registers156                                |

|-------------------------------------------------|

| General Registers                               |

| Status, MSW and Instruction Registers           |

| Debug Registers                                 |

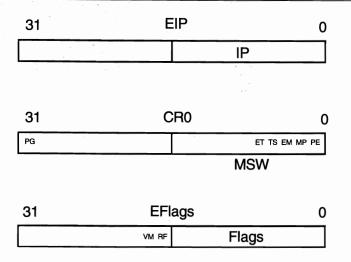

| Test Registers                                  |

| Segmentation Unit                               |

| Paging Unit                                     |

| Bus Unit                                        |

| Protected Mode162                               |

| Page Translation164                             |

| Virtual Paging164                               |

| Translation Lookaside Buffer                    |

| Virtual-8086 Mode                               |

| Automatic Self-Test                             |

| 80386DX External Interface                      |

| The Address Bus                                 |

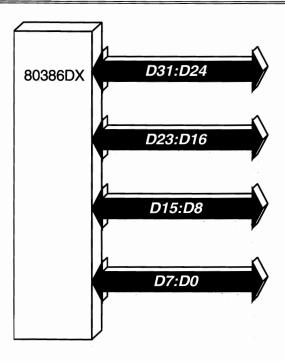

| The Data Bus                                    |

| The Control Bus184                              |

| Bus Cycle Definition Outputs                    |

| Processor Extension Lines                       |

| Address Status Output                           |

| Pipelining Control Input                        |

| Dynamic Bus Sizing (BS16#)                      |

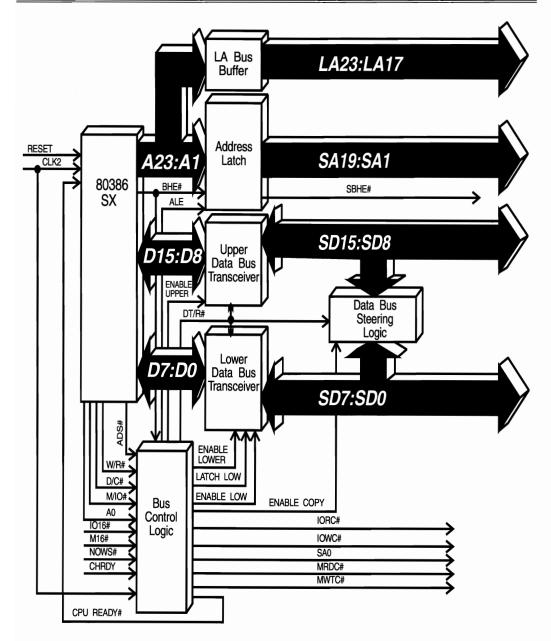

| 80386SX External Interface                      |

| Interface Signal Differences                    |

| A0 or BLE#                                      |

| Addressing Scheme, Data Bus Width Ramifications |

| Throughput and Compatibility Considerations     |

## Chapter 11: The 80386 System Kernel

| Introduction                                  |  |

|-----------------------------------------------|--|

| The 80386SX System Kernel                     |  |

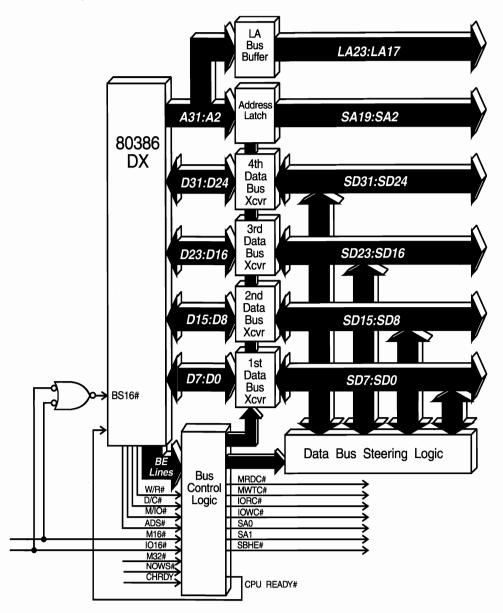

| The 80386DX System Kernel                     |  |

| 80386DX System Kernel with Dynamic Bus Sizing |  |

| Introduction                                  |  |

| Reading from an 8-Bit Device                  |  |

| One-Byte Read from an 8-Bit Device            |  |

| Two-Byte Read from an 8-Bit Device            |  |

| Four-Byte Read from an 8-Bit Device           |  |

| Writing to an 8-Bit Device                    |  |

| One-Byte Write to an 8-Bit Device             |  |

| Two-Byte Write to an 8-Bit Device             |  |

|                                               |  |

| Four-Byte Write to an 8-Bit Device               |     |

|--------------------------------------------------|-----|

| Reading from a 16-Bit Device                     |     |

| Two-Byte Read from a 16-Bit Device               |     |

| Four-Byte Read from a 16-Bit Device              |     |

| Writing to a 16-Bit Device                       |     |

| Two-Byte Write to a 16-Bit Device                |     |

| Four-Byte Write to a 16-Bit Device               |     |

| Reading from a 32-Bit Device                     | 210 |

| Writing to a 32-Bit Device                       | 211 |

| 80386DX System Kernel without Dynamic Bus Sizing |     |

| Introduction                                     |     |

| Reading from a 16-Bit Device                     |     |

| Two-Byte Read from a 16-Bit Device               |     |

| Four-Byte Read from a 16-Bit Device              |     |

| Writing to a 16-Bit Device                       | 216 |

| Two-Byte Write to a 16-Bit Device                |     |

| Four-Byte Write to a 16-Bit Device               | 217 |

|                                                  |     |

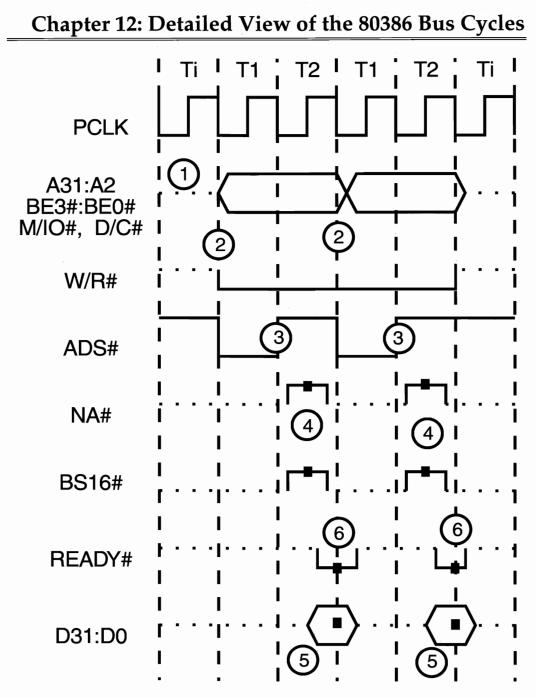

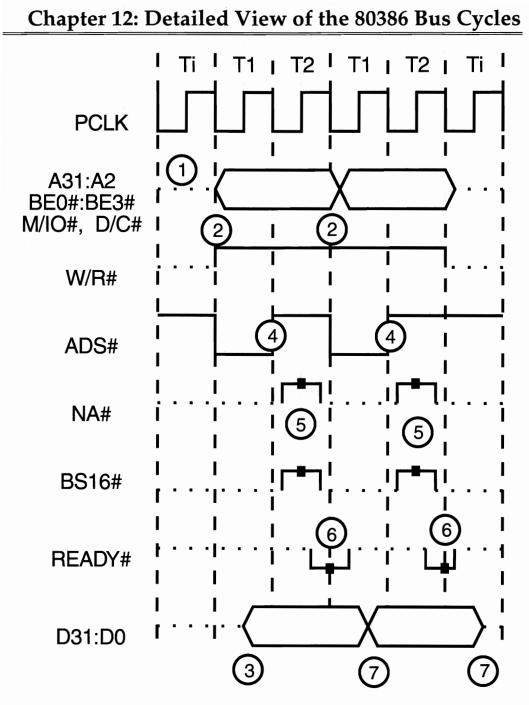

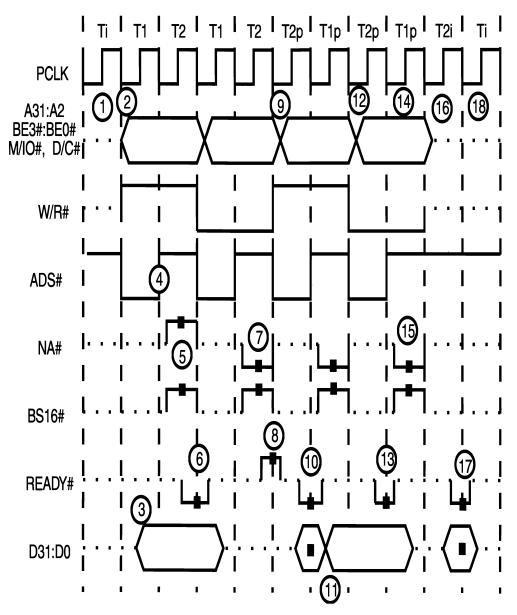

#### Chapter 12: Detailed View of the 80386 Bus Cycles

| The Bus Cycle Types             | 221 |

|---------------------------------|-----|

| Address Pipelining Overview     | 222 |

| Memory or I/O Read Bus Cycle    | 222 |

| Memory or I/O Write Bus Cycle   |     |

| Address Pipelining Example      |     |

| Interrupt Acknowledge Bus Cycle |     |

| Halt or Shutdown Bus Cycle      |     |

### **Part 2: Memory Subsystems**

### **Chapter 13: RAM Memory: Theory of Operation**

| Dynamic RAM (DRAM) Memory                         |  |

|---------------------------------------------------|--|

| DRAM Addressing Sequence                          |  |

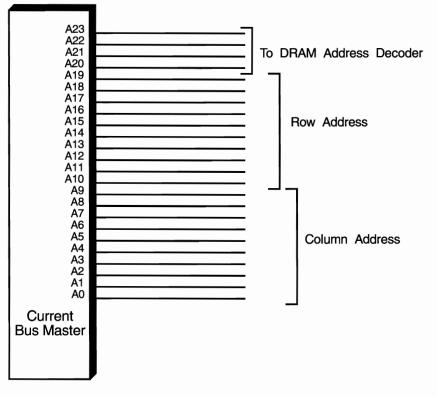

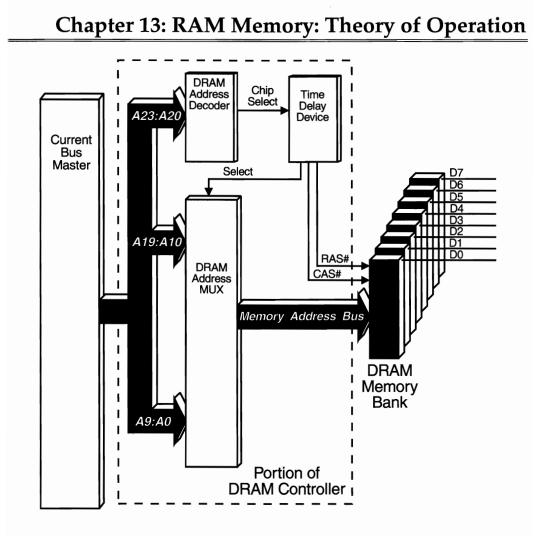

| Row and Column Address Source                     |  |

| DRAM Addressing Logic                             |  |

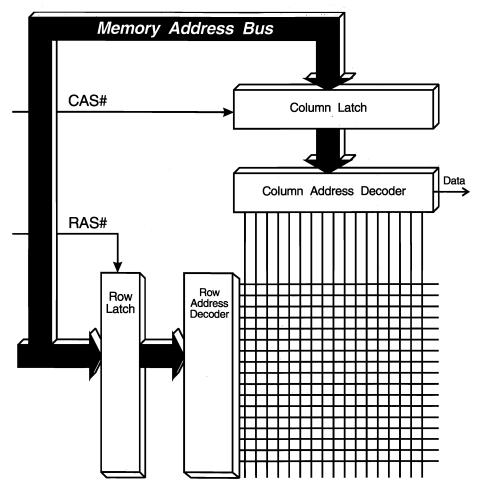

| Detailed Description of DRAM Addressing Sequence  |  |

| How Data is Stored in DRAM                        |  |

| DRAM Refresh                                      |  |

| Refresh Logic and RAS-only Refresh                |  |

| CAS-before-RAS Refresh                            |  |

| Hidden Refresh                                    |  |

| Self-Refresh                                      |  |

| Destructive Read: Pre-Charge Delay and Cycle Time |  |

| 0                                                 |  |

| DRAM Bank                            |  |

|--------------------------------------|--|

| DRAM Bank Width                      |  |

| DRAM Error Detection and Correction  |  |

| DRAM Parity                          |  |

| Error-Checking-and-Correcting Memory |  |

| Page-Mode DRAM and Its Variations    |  |

| Page Mode DRAM                       |  |

| Enhanced Page Mode DRAM              |  |

| Burst and Nibble Mode DRAM           |  |

| Static Column RAM (SCRAM)            |  |

| Synchronous DRAM                     |  |

| Interleaved Memory Architecture      |  |

| Static RAM (SRAM)                    |  |

## Chapter 14: Cache Memory Concepts

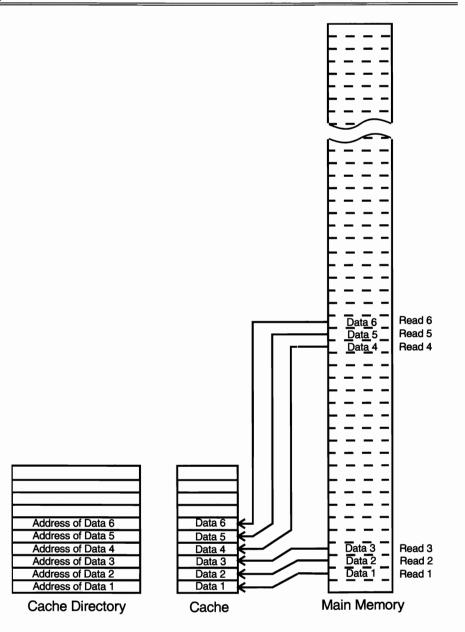

| The Problem                                                             | 273 |

|-------------------------------------------------------------------------|-----|

| The Solution                                                            | 274 |

| Principles of Locality                                                  | 277 |

| Temporal Locality                                                       | 277 |

| Spatial Locality                                                        | 277 |

| Cache Performance                                                       | 278 |

| Overall System Performance                                              | 278 |

| Cache Consistency                                                       | 279 |

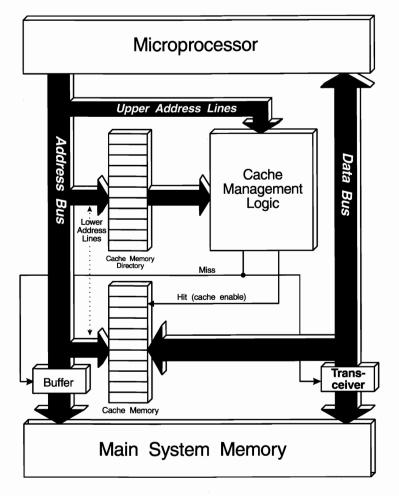

| Components of a Cache Subsystem                                         |     |

| Cache Memory                                                            |     |

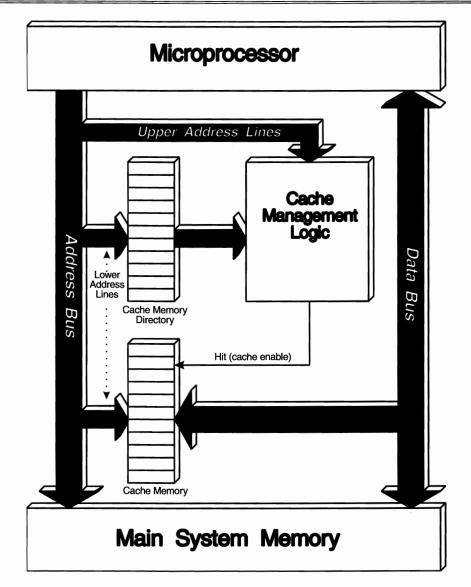

| Cache Management Logic                                                  | 281 |

| Cache Memory Directory                                                  | 281 |

| Intro to Cache Architecture, Coherency, Write Policies and Organization | 282 |

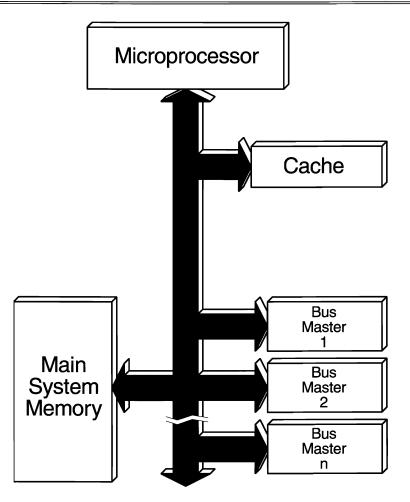

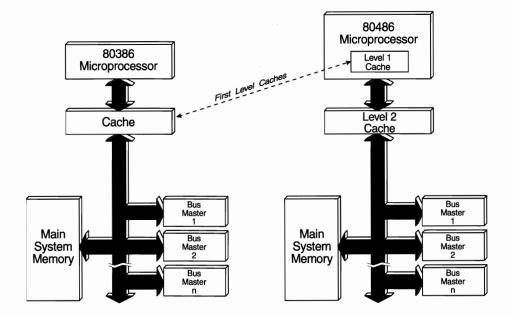

| Cache Architectures                                                     | 283 |

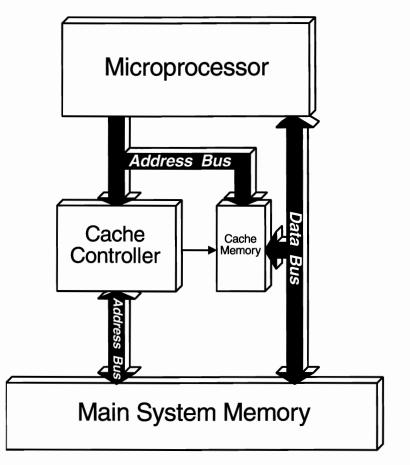

| Look-Through Cache                                                      | 283 |

| Look-Aside Cache                                                        | 287 |

| First- and Second-Level Caches                                          | 289 |

| Combined (Unified) and Split (Dedicated) Caches                         | 290 |

| Cache Consistency (Coherency)                                           | 291 |

| Causes of Cache Consistency Problems                                    | 292 |

| Write Policy                                                            | 292 |

| Write-Through Cache Designs                                             | 293 |

| Buffered Write-Through Designs                                          | 293 |

| Write-Back Cache Designs                                                | 294 |

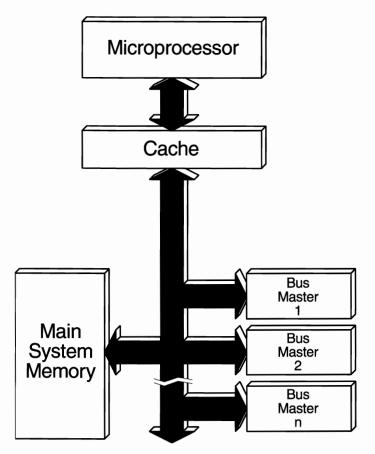

| Bus Master/Cache Interaction                                            | 295 |

| Bus Snooping/Snarfing                                                   | 295 |

| Coherency via Cache Flushing                                            | 297 |

### **ISA System Architecture**

| Software-Enforced Coherency                                   |

|---------------------------------------------------------------|

| Cache Organization and Size                                   |

| Fully-Associative Cache                                       |

| Direct-Mapped Cache (One-Way Set-Associative)                 |

| Two-Way Set-Associative Cache                                 |

| Four-Way Set-Associative Cache                                |

| Least-Recently Used (LRU) Algorithm                           |

| Cache Line Size                                               |

| Cache Size                                                    |

| First-Level Cache Size                                        |

| Second-Level Cache Size                                       |

| Cache Addressing                                              |

| I/O Information Not Cached                                    |

| Non-Cacheable Memory                                          |

| Testing Memory                                                |

| Chapter 15: ROM Memory                                        |

| ROM Memory — Theory of Operation                              |

| Introduction                                                  |

| Fusible-Link PROM                                             |

| Masked ROM (MROM)                                             |

| Eraseable Programmable Read-Only Memory (EPROM)               |

| Electrically Eraseable Programmable Read-Only Memory (EEPROM) |

| Flash EEPROM                                                  |

| ROM's Interface to System                                     |

| System Board ROM Memory                                       |

| Testing                                                       |

| Shadow RAM                                                    |

| Shadow RAM and ROM Occupying Different Address Spaces         |

| Shadow RAM and ROM Occupy Same Address Space                  |

| Double Mapping ROM and Shadow RAM Address Space               |

| Recovering Unused ROM Address Space                           |

| 32KB System Board ROM Configuration                           |

| 64KB System Board ROM Configuration                           |

| ROMs on ISA Cards (Device ROMs)                               |

## Part 3: The Industry Standard Architecture

### Chapter 16: ISA Bus Structure

| Introduction | 335 |

|--------------|-----|

| Address Bus  | 338 |

| Data Bus     | 339 |

| Bus Cycle Definition                                |

|-----------------------------------------------------|

| Bus Cycle Timing                                    |

| Device Size                                         |

| Reset                                               |

| DMA                                                 |

| Interrupts                                          |

| Error Reporting Signal                              |

| Miscellaneous Signals                               |

| Chapter 17: Types of ISA Bus Cycles                 |

| Introduction                                        |

| Transfers with 8-bit Devices                        |

| Transfers with 16-bit Devices                       |

| Standard 16-bit Memory Device ISA Bus Cycle         |

| Standard 16-bit I/O Device ISA Bus Cycle            |

| 0-Wait State Access to 16-bit Memory Device         |

|                                                     |

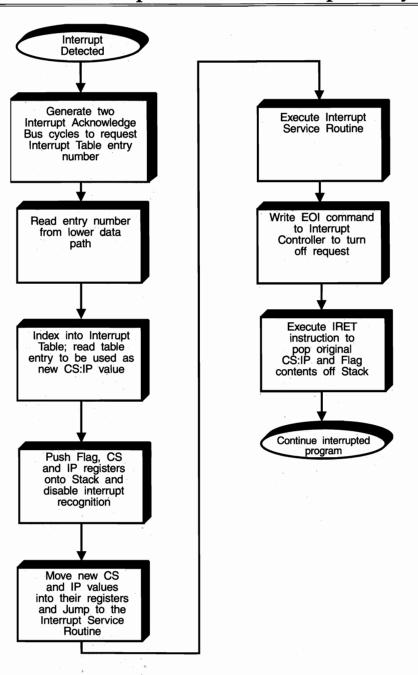

| Chapter 18: The Interrupt Subsystem                 |

| What Is an Interrupt?                               |

| Microprocessor Response to Interrupt Request        |

| Interrupt Acknowledge Bus Cycles                    |

| Saving Pointer to Interrupted Program               |

| Clearing the Interrupt Enable Flag                  |

| Jumping to the ISR                                  |

| Resuming the Interrupted Program                    |

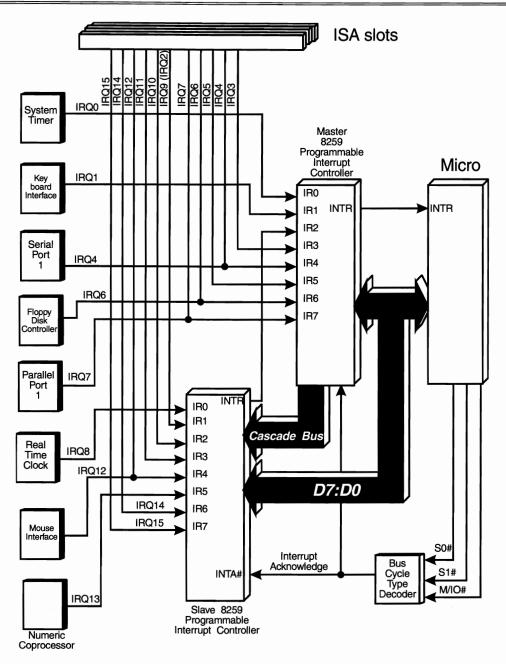

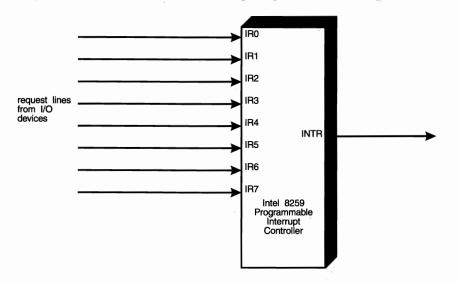

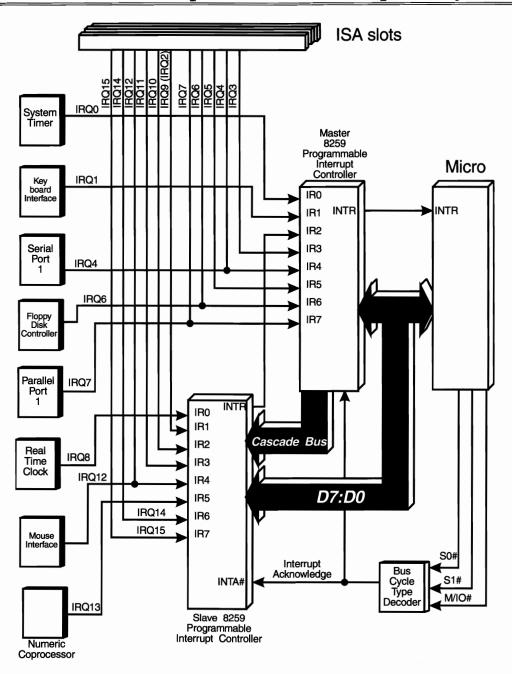

| When One 8259 Interrupt Controller Isn't Enough 383 |

| Servicing Requests to Slave Interrupt Controller    |

| Interrupt Table Entry Assignments                   |

| IRQ2 Redirect                                       |

| Shareable Interrupts in ISA Machines                |

| Generating the Interrupt Request                    |

| Interrupt Table Initialization – Add-in Devices     |

| Shared Interrupt Procedure                          |

| Phantom Interrupts                                  |

| Programming the 8259                                |

| Introduction                                        |

| Programming the Registers                           |

| Non-Maskable Interrupt Requests (NMI) 399           |

| Software Interrupts                                 |

| Software Exceptions                                 |

| Software Interrupt Instruction                      |

| Protected Mode Interrupts                           |

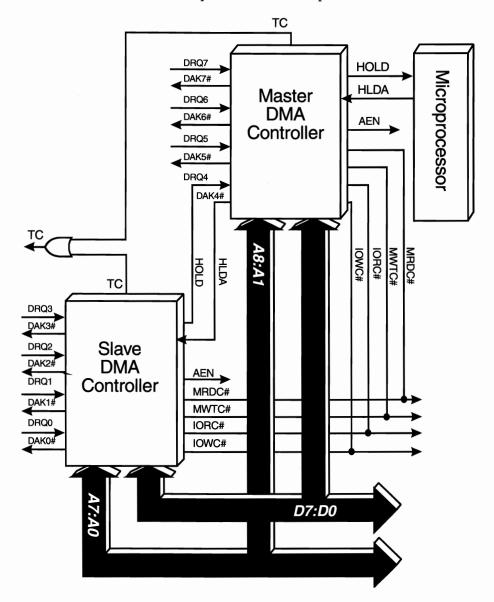

#### Chapter 19: Direct Memory Access (DMA)

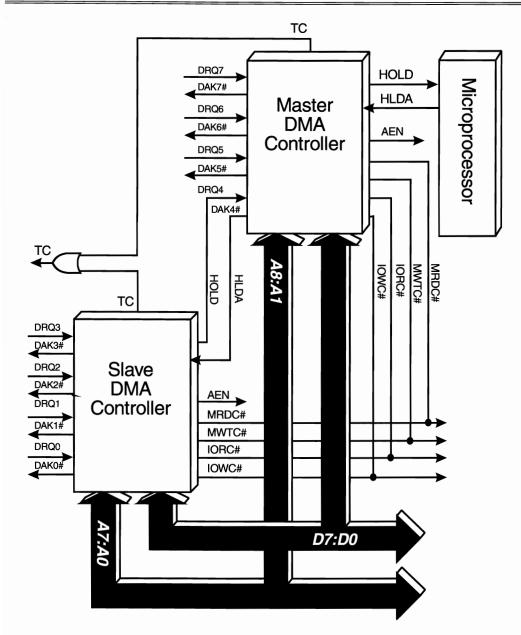

| DMA Concept                     | . 409 |

|---------------------------------|-------|

| DMA Example                     | . 410 |

| DMA Controller (DMAC)           |       |

| DMA Transfer Types              | . 414 |

| DMA Transfer Modes              |       |

| Single Transfer Mode            | . 415 |

| Block Transfer Mode             | . 416 |

| Demand Transfer Mode            | . 416 |

| Cascade Mode                    | . 417 |

| DMAC Priority Logic             | . 417 |

| DMA Bus Cycle                   |       |

| Byte or Word Transfers          |       |

| DMAC Addressing Capability      | . 423 |

| Addressing ISA Memory           |       |

| Addressing Local Bus Memory     |       |

| Address Translation             |       |

| Data Bus Steering               | . 430 |

| DMA Transfer Rate               |       |

| DMAC Initialization During POST | . 431 |

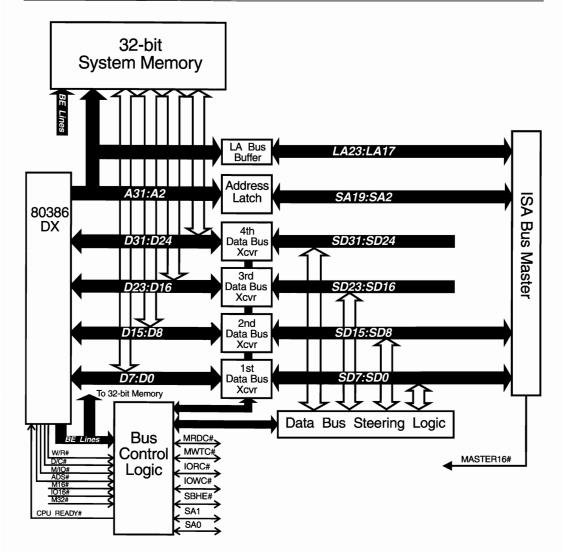

#### **Chapter 20: ISA Bus Masters**

| ISA Bus Master Capability                     |  |

|-----------------------------------------------|--|

| ISA Bus Masters in 80386DX and Higher Systems |  |

| Address Translation                           |  |

| Data Bus Steering                             |  |

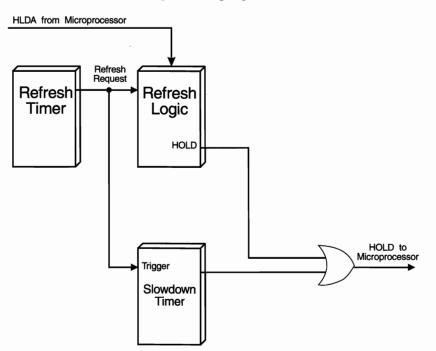

| Bus Masters and DRAM Refresh                  |  |

#### Chapter 21: RTC and Configuration RAM

| Accessing the RAM Locations           | Introduction                                 |  |

|---------------------------------------|----------------------------------------------|--|

|                                       | Accessing the RAM Locations                  |  |

| Real-Time Clock Function              | Address Decoder and RTC's Hardware Interface |  |

|                                       | Real-Time Clock Function                     |  |

| Using BIOS to Control Real-Time Clock | Using BIOS to Control Real-Time Clock        |  |

| Configuration RAM Usage               | Configuration RAM Usage                      |  |

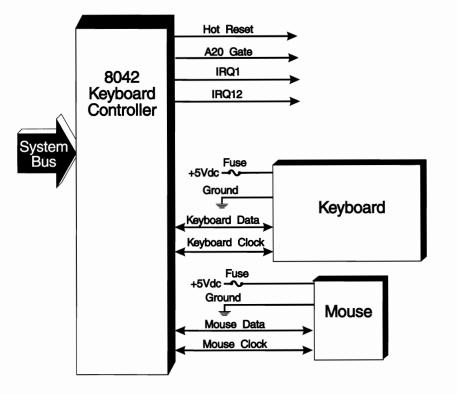

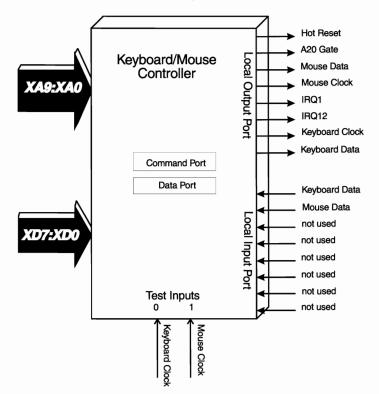

#### Chapter 22: Keyboard/Mouse Interface

| Keyboard/Mouse Interface4 | 149 |

|---------------------------|-----|

| Keyboard4                 |     |

| Mouse                     |     |

| 8042 Local I/O Ports      |     |

| Hot Reset                 |     |

### Contents

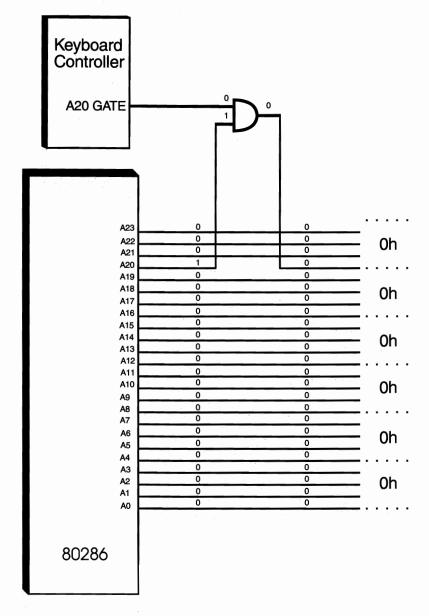

| A20 Gate              | 451 |

|-----------------------|-----|

| Local Port Definition |     |

| System Interface      |     |

| Command/Status Port   |     |

| Data Port             | 456 |

| BIOS Routine          | 457 |

### Chapter 23: Numeric Coprocessor

| Introduction                                      |     |

|---------------------------------------------------|-----|

| Setup                                             | 460 |

| With Numeric Coprocessor Installed                |     |

| Numeric Coprocessor Reset                         |     |

| Without Numeric Coprocessor Installed (Emulation) |     |

| Weitek Numeric Coprocessor                        | 467 |

| Introduction                                      |     |

| Systems Incorporating Just the Weitek             |     |

| General                                           |     |

| Weitek Handling of Intel Coprocessor Instructions |     |

| Systems Incorporating Both Coprocessor Types      |     |

## Chapter 24: ISA Timers

| 469 |

|-----|

|     |

|     |

|     |

|     |

|     |

|     |

## Appendices

| O Address Map    | '9 |

|------------------|----|

| lossary of Terms | )1 |

| -                |    |

|                  |    |

| x 507 |

|-------|

| κ     |

## Figures

| Figure 1. Simplified Block Diagram of Typical ISA System                    | 5   |

|-----------------------------------------------------------------------------|-----|

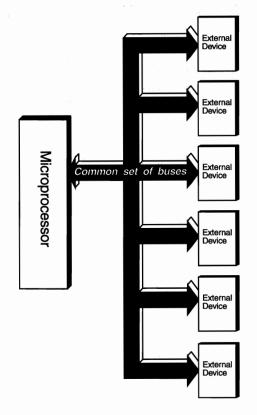

| Figure 1-1. Microprocessor's Relationship to External Devices               | .13 |

| Figure 1-2. Sample Instruction Sequence                                     |     |

| Figure 1-3. The 80286 Address Bus                                           | .18 |

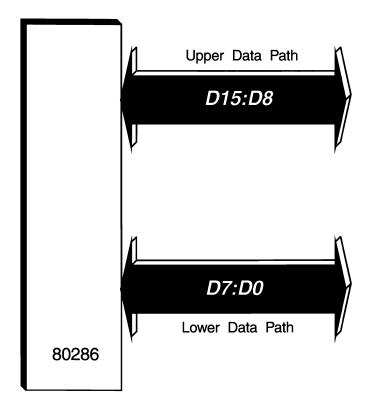

| Figure 1-4. The 80286 Data Bus                                              | .20 |

| Figure 2-1. Crystal Oscillator Output                                       | .22 |

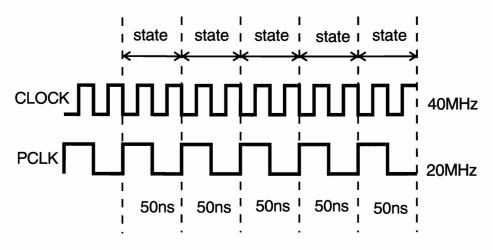

| Figure 2-2. Relationship of CLOCK and PCLK                                  | .23 |

| Figure 2-3. Each Cycle of PCLK Defines the Duration of a State              | .24 |

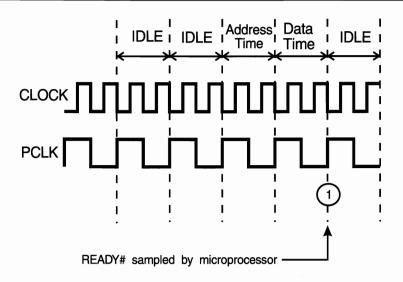

| Figure 2-4. Bus Cycle Consisting of Address Time and Data Time              |     |

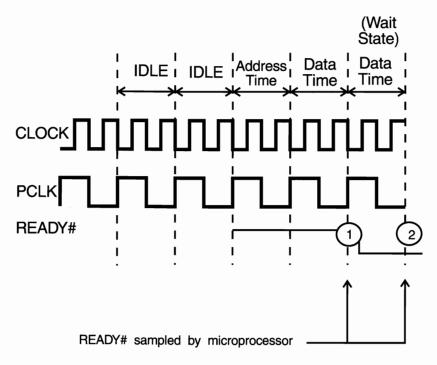

| Figure 2-5. Bus Cycle with One Wait State Inserted                          | .27 |

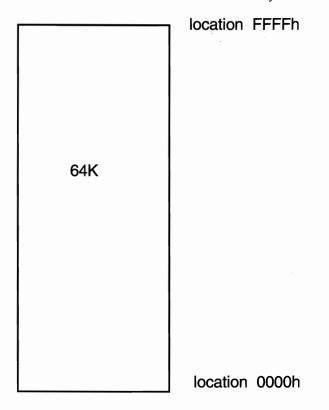

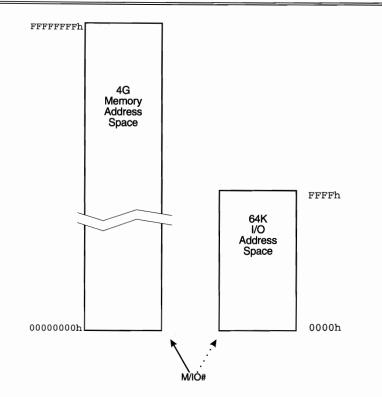

| Figure 3-1. Single 64K Address Space                                        | .30 |

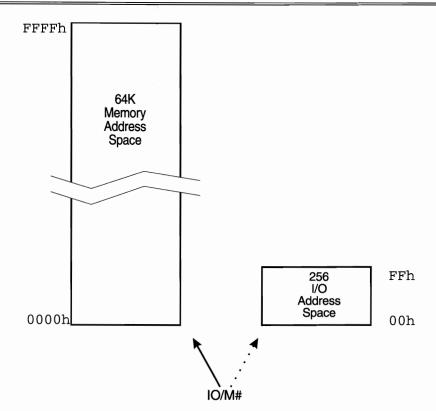

| Figure 3-2. The 8085's Memory and I/O Address Spaces                        | .32 |

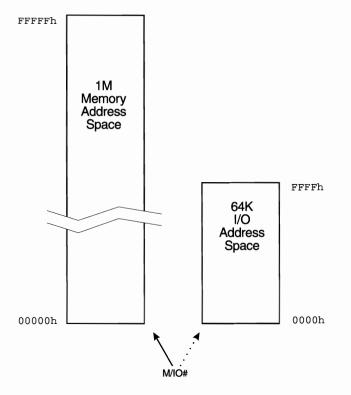

| Figure 3-3. 8086 and 8088 Memory and I/O Address Space                      | .34 |

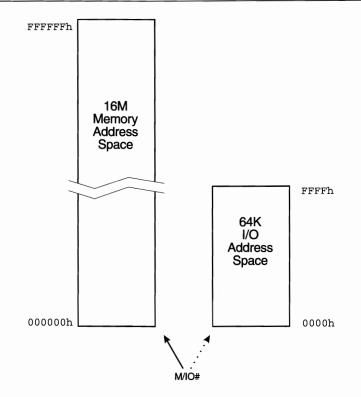

| Figure 3-4. 286 and 386SX Memory and I/O Address Space                      | .35 |

| Figure 3-5. 386/486/Pentium Processor Memory and I/O Address Space          |     |

| Figure 4-1. Relationship of Address Bus, Address Decoders and Devices       | .40 |

| Figure 4-2. PC Memory Address Map                                           |     |

| Figure 4-3. Example PC/XT ROM Address Decoder                               | .45 |

| Figure 4-4. System Board I/O Address Decoder                                | .48 |

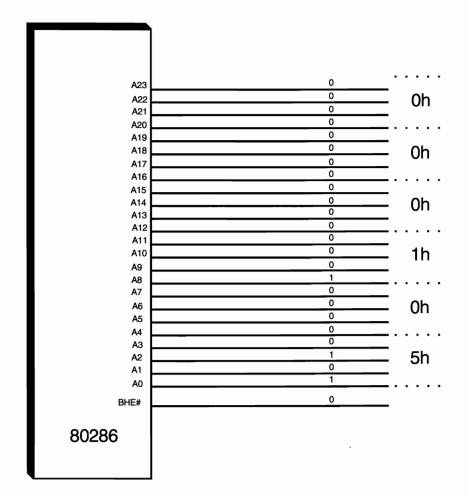

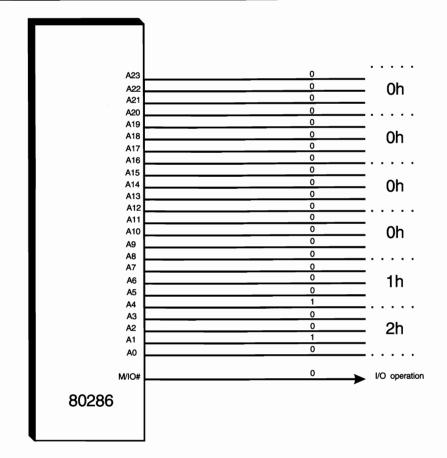

| Figure 4-5. Microprocessor Placing I/O Address 0012h on the Address Bus     | .51 |

| Figure 5-1. 80286 Microprocessor Block Diagram                              | .54 |

| Figure 5-2. The 80286 General Registers                                     | .57 |

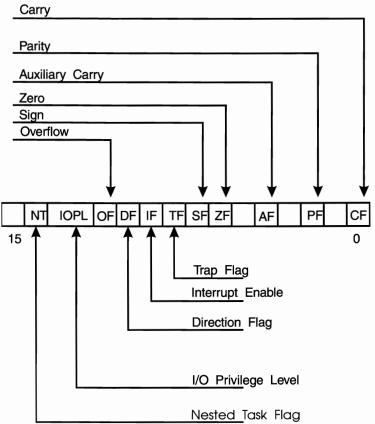

| Figure 5-3. The 80286 Status and Control Registers                          | .59 |

| Figure 5-4. The Flag Register's Status, Control and System Bits             | .60 |

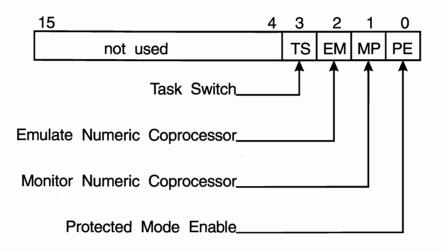

| Figure 5-5. The 80286 Machine Status Word (MSW) Register                    | .62 |

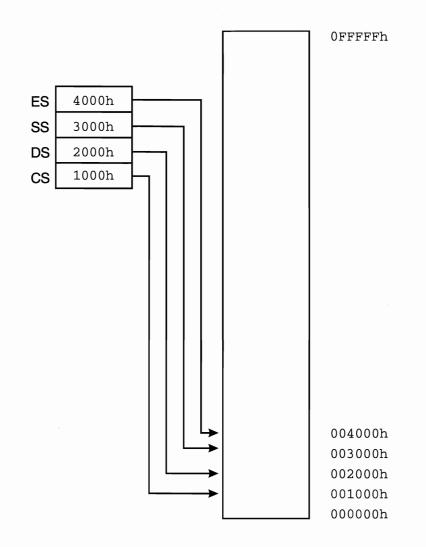

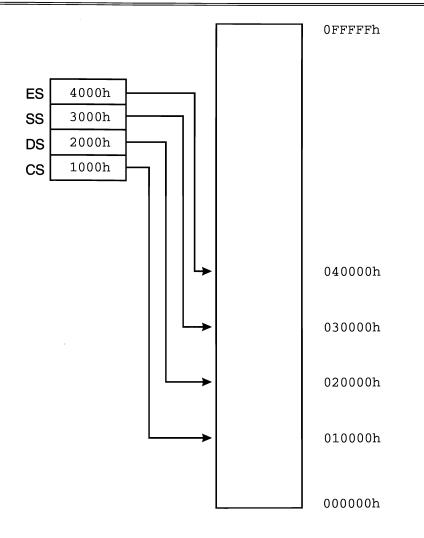

| Figure 5-6. Result If Segment Registers Were Restricted to 16 Bits          | .65 |

| Figure 5-7. Segment Registers Point to Start Address of Memory Segments     | .66 |

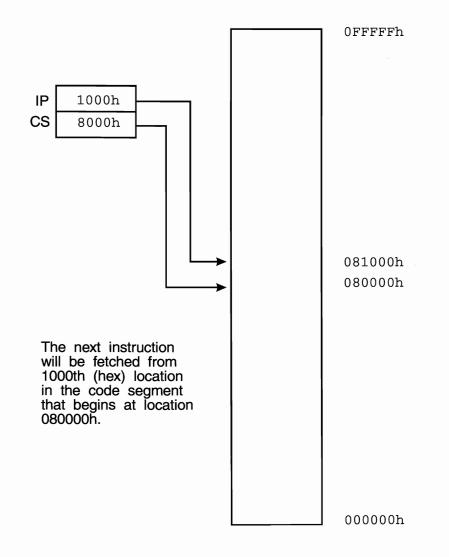

| Figure 5-8. CS and IP Registers                                             | .68 |

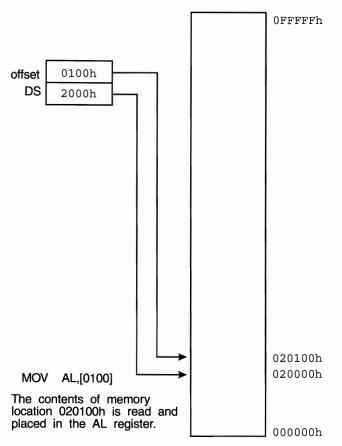

| Figure 5-9. Illustration of Location within the Data Segment                | .70 |

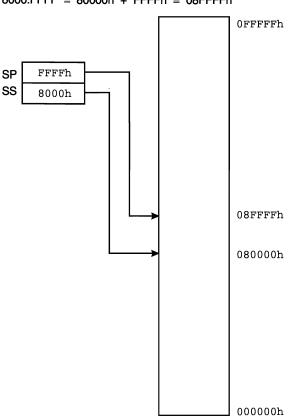

| Figure 5-10. The Stack                                                      | .72 |

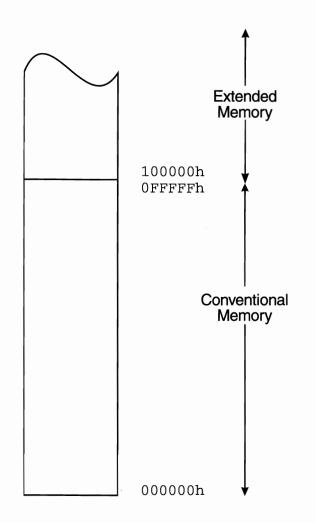

| Figure 5-11. Extended Memory                                                | .76 |

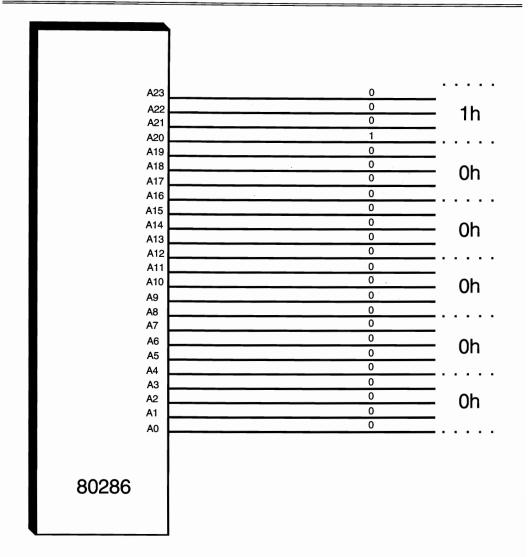

| Figure 5-12. A20 High                                                       | .78 |

| Figure 5-13. A20 Gate                                                       | .80 |

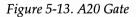

| Figure 5-14. The 80286 Address Bus                                          |     |

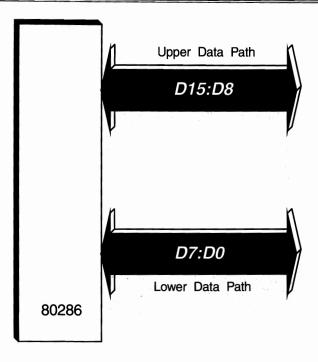

| Figure 5-15. The 80286 Data Bus                                             | .88 |

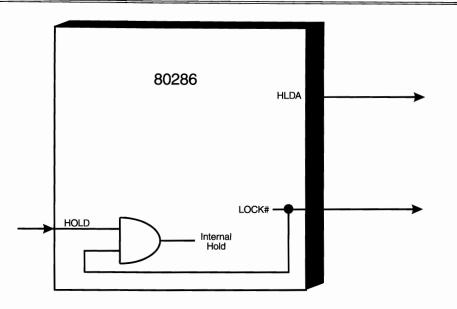

| Figure 5-16. The Lock Output                                                | .92 |

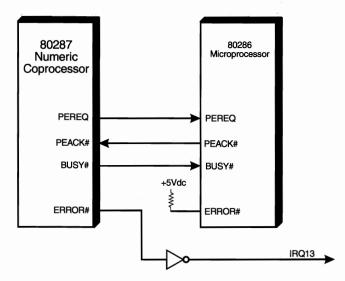

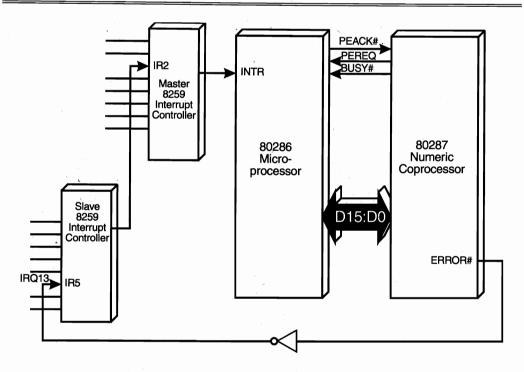

| Figure 5-17. Relationship of the Microprocessor and the Numeric Coprocessor | .96 |

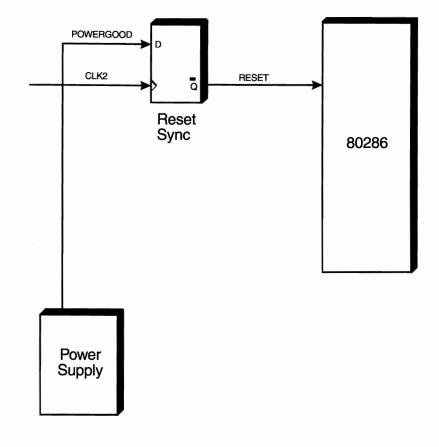

| Figure 5-18. The Reset Logic                                                | .98 |

|                                                                             |     |

## **ISA System Architecture**

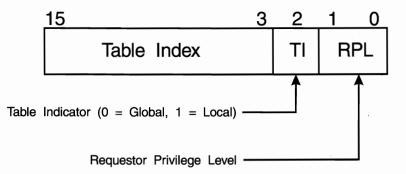

| Figure 5-19. The Segment Selector                                              | 102 |

|--------------------------------------------------------------------------------|-----|

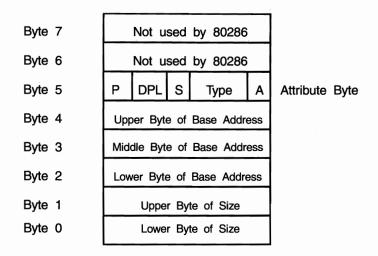

| Figure 5-20. The Segment Descriptor                                            | 104 |

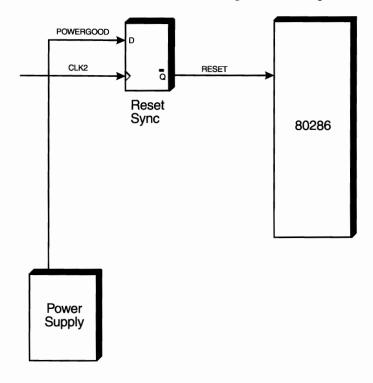

| Figure 7-1. RESET Is Derived from POWERGOOD                                    | 114 |

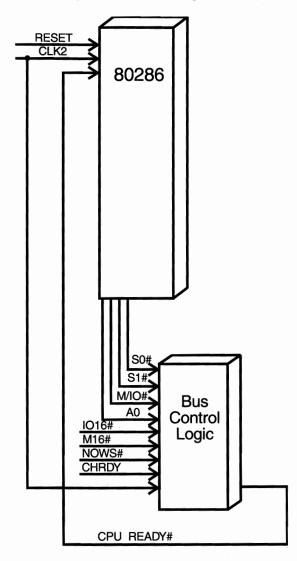

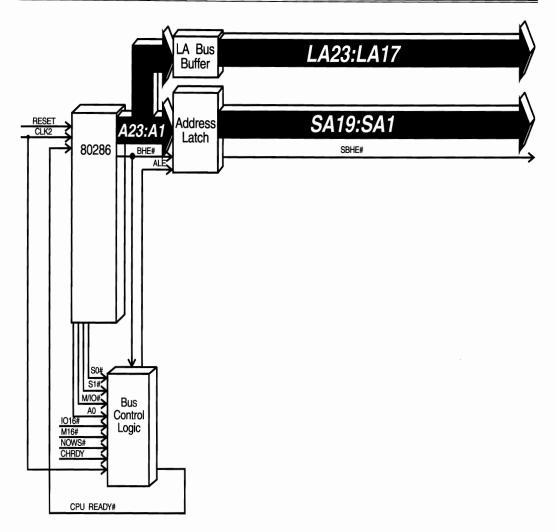

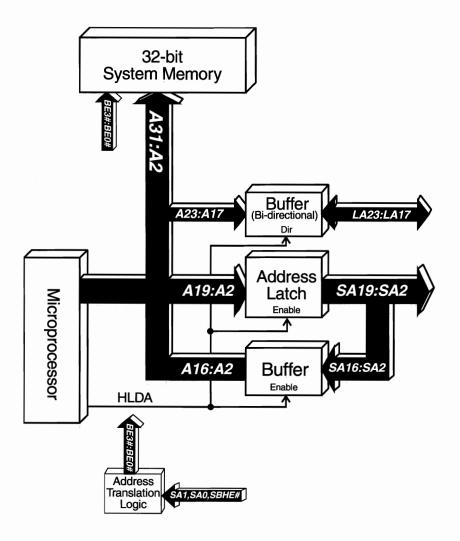

| Figure 8-1. The Bus Control Logic                                              | 120 |

| Figure 8-2. The Address Latch                                                  |     |

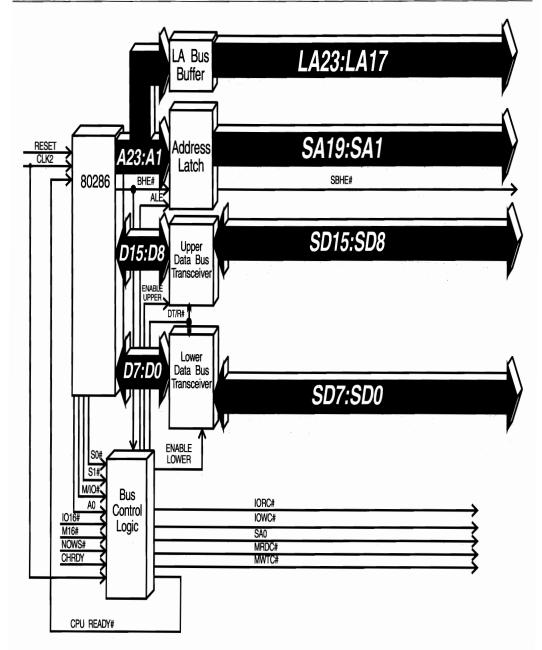

| Figure 8-3. The Data Bus Transceivers                                          |     |

| Figure 8-4. The Data Bus Steering Logic                                        |     |

| Figure 8-5. Access Time                                                        | 135 |

| Figure 8-6. Custom Ready Timer Logic                                           | 137 |

| Figure 9-1. The Read Bus Cycle                                                 | 142 |

| Figure 9-2. The 80286 System Engine                                            |     |

| Figure 9-3. The Write Bus Cycle                                                |     |

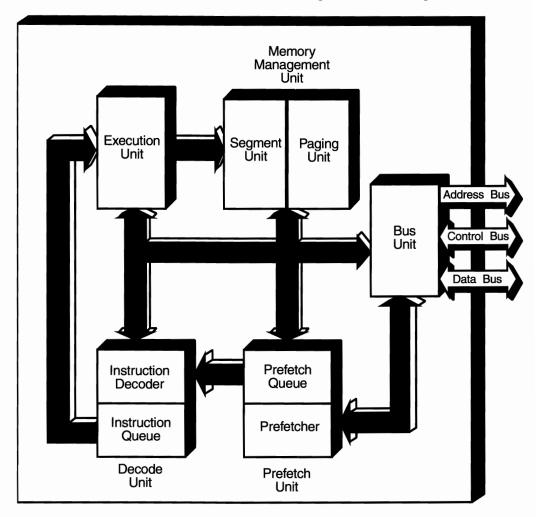

| Figure 10-1. 80386 Microprocessor Block Diagram                                |     |

| Figure 10-2. The 80386 General Registers                                       | 157 |

| Figure 10-3. The 80386 Status and Instruction Registers                        |     |

| Figure 10-4. The 80386 Debug Registers                                         |     |

| Figure 10-5. The 80386 Test Registers                                          |     |

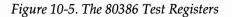

| Figure 10-6. The 80386 Segment Registers                                       |     |

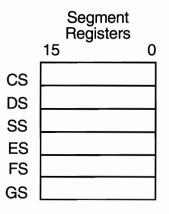

| Figure 10-7. The 80286 Segment Descriptor Format                               |     |

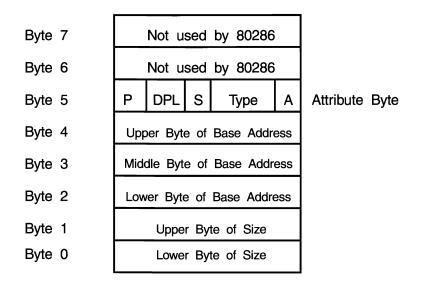

| Figure 10-8. The 80386 General Segment Descriptor Format                       |     |

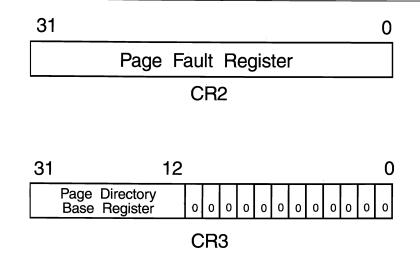

| Figure 10-9. Control Registers CR2 and CR3                                     |     |

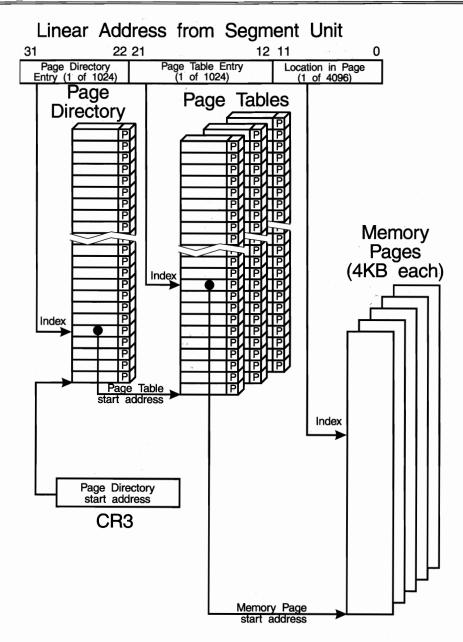

| Figure 10-10. Translation of Linear Memory Address to Physical Memory Address  |     |

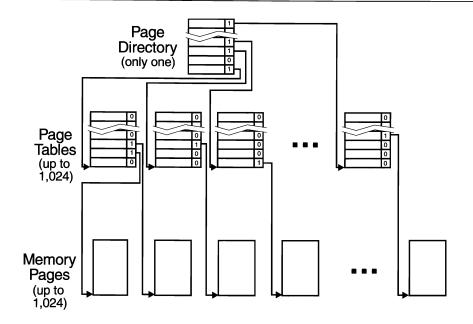

| Figure 10-11. Another View of the Page Directory, Page Tables and Memory Pages |     |

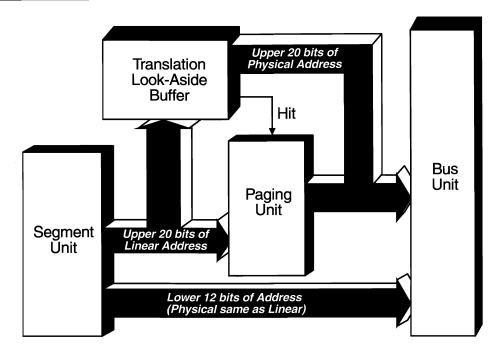

| Figure 10-12. The Translation Look-Aside Buffer                                |     |

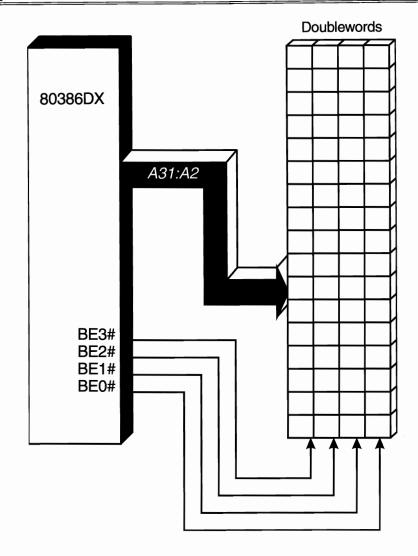

| Figure 10-13. 80386DX Address/Byte Enable Relationship                         |     |

| Figure 10-14. The 80386DX Data Bus                                             |     |

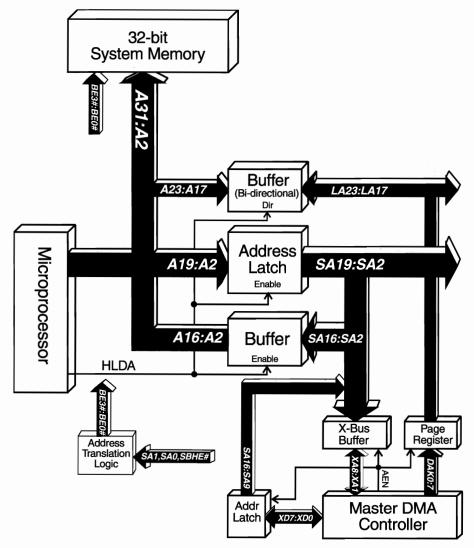

| Figure 11-1. The 80386SX-Based Kernel                                          |     |

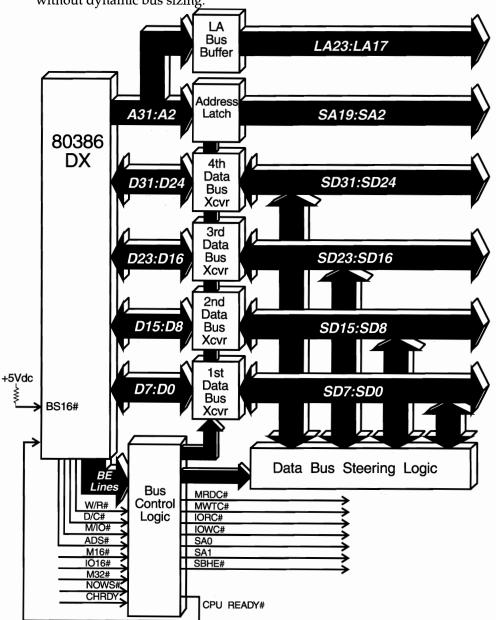

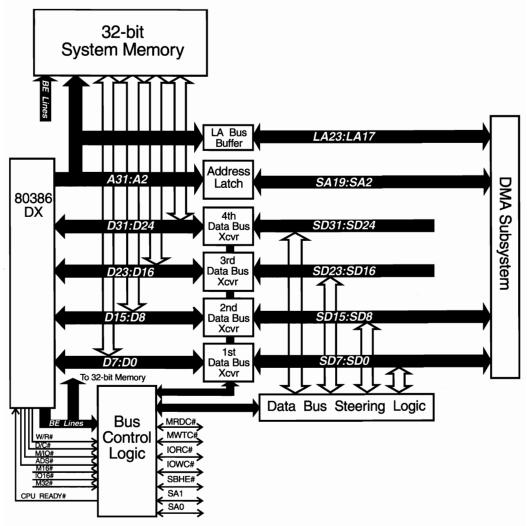

| Figure 11-2. The 80386DX-Based Kernel with Dynamic Bus Sizing Implemented      |     |

| Figure 11-3. The 80386DX-Based Kernel without Dynamic Bus Sizing Implemented   |     |

| Figure 12-1. Non-Pipelined Read Bus Cycle                                      |     |

| Figure 12-2. Non-Pipelined Write Bus Cycle                                     |     |

| Figure 12-3. Transition from Non-Pipelined to Pipelined Operation              |     |

| Figure 13-1. Block Diagram of a DRAM Memory Chip                               |     |

| Figure 13-2. The Address Output by the Current Bus Master                      | 239 |

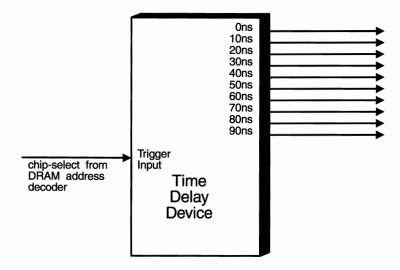

| Figure 13-3. The Time Delay Device                                             |     |

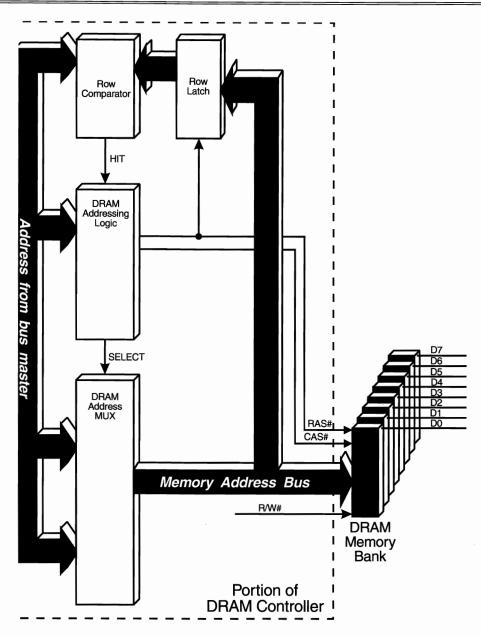

| Figure 13-4. Block Diagram of DRAM Addressing Logic                            |     |

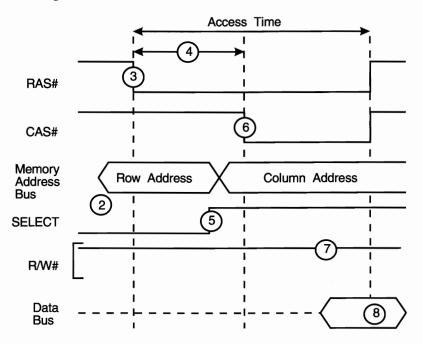

| Figure 13-5. DRAM Addressing Timing Diagram                                    |     |

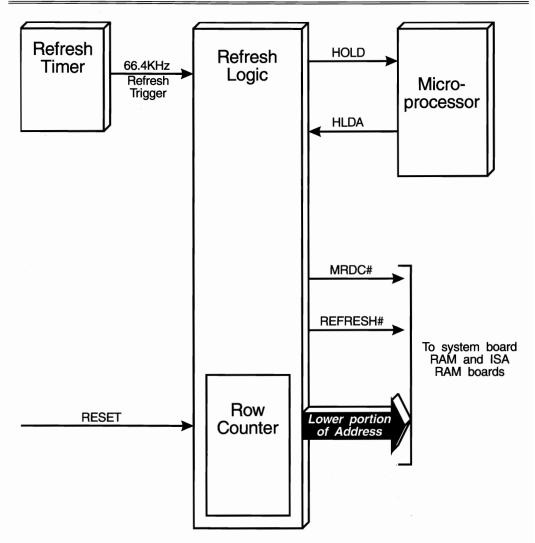

| Figure 13-6. The Refresh Logic                                                 | 246 |

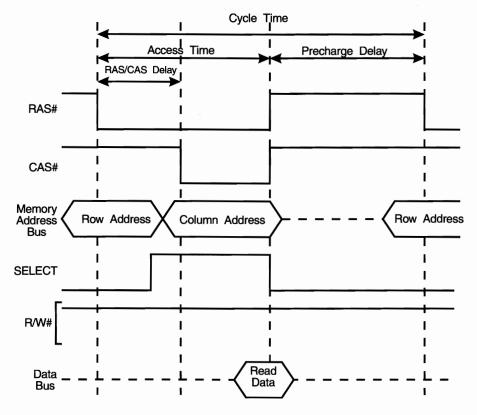

| Figure 13-7. Pre-Charge Delay and Cycle Time                                   |     |

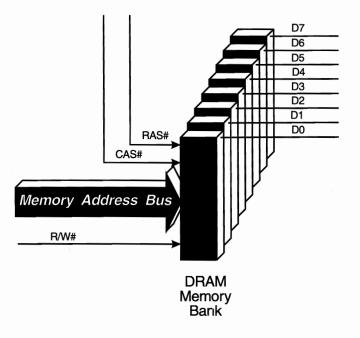

| Figure 13-8. The DRAM Bank                                                     |     |

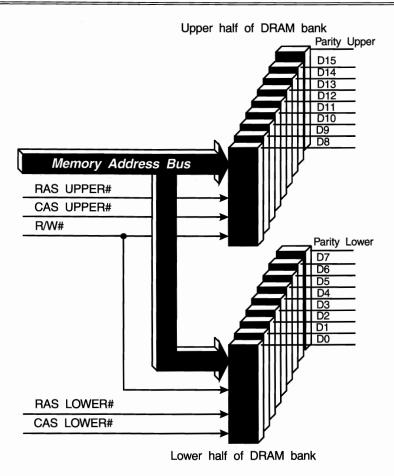

| Figure 13-9. 16-Bit DRAM Bank                                                  | 254 |

## Figures

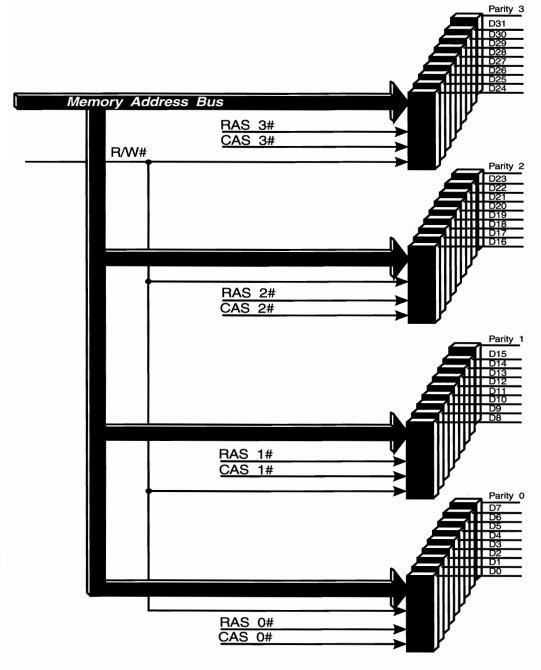

| Figure 13-10. 32-Bit DRAM Bank                                           | .255  |

|--------------------------------------------------------------------------|-------|

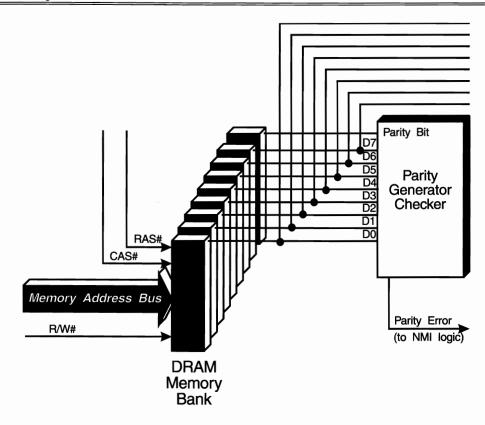

| Figure 13-11. The System Board DRAM Parity Logic                         |       |

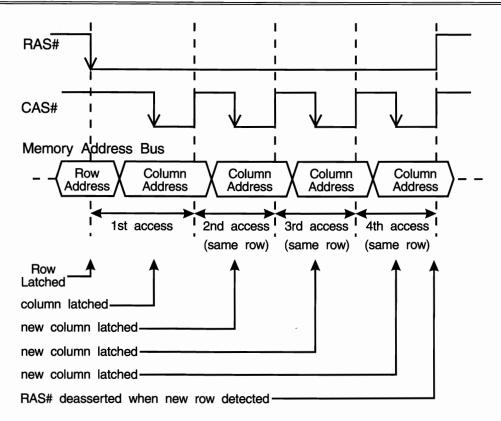

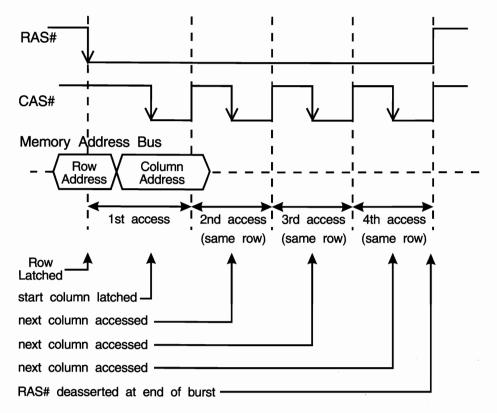

| Figure 13-12. Page Mode DRAM Support Logic                               |       |

| Figure 13-13. Page Mode DRAM RAS/CAS Timing                              |       |

| Figure 13-14. Burst Mode Access Timing                                   |       |

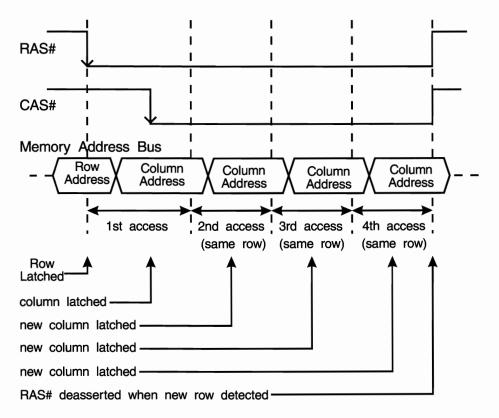

| Figure 13-15. SCRAM Access Timing                                        |       |

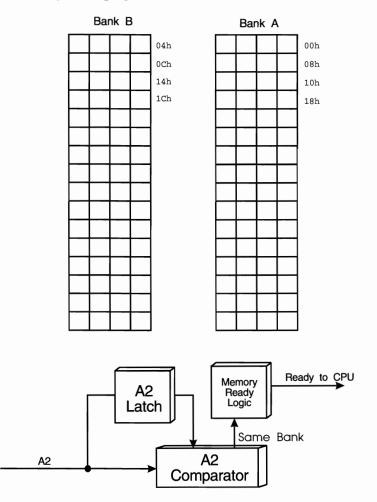

| Figure 13-16. Interleaved Memory Architecture                            |       |

| Figure 14-1. The Cache Memory Concept                                    |       |

| Figure 14-2. Cache Subsystem Components                                  |       |

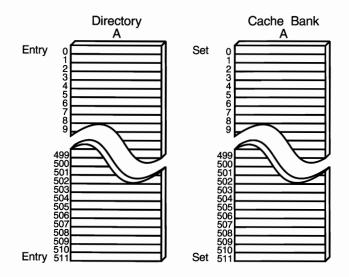

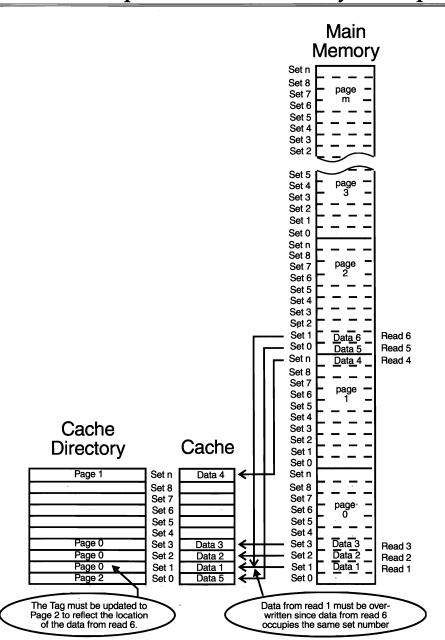

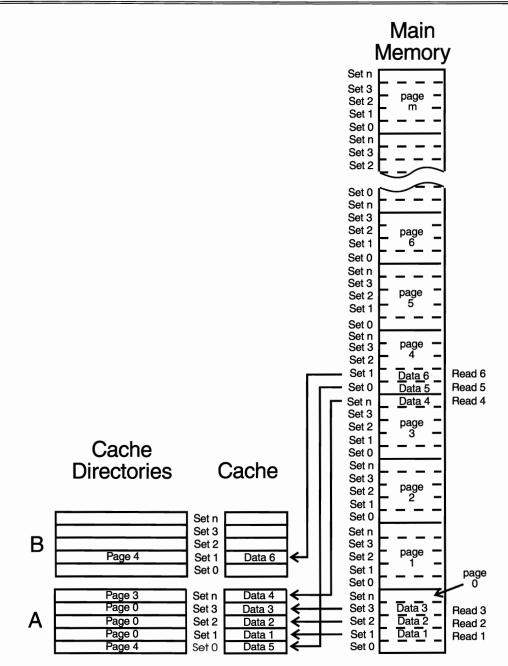

| Figure 14-3. Relationship of Cache Directory to the Cache Memory         |       |

| Figure 14-4. Look-Through Cache Architecture                             |       |

| Figure 14-5. Look-Through-Concurrent Bus Operation                       |       |

| Figure 14-6. Look-Aside Cache Architecture                               |       |

| Figure 14-7. First- and Second-Level Caches                              |       |

| Figure 14-8. Fully-Associative Cache Organization                        |       |

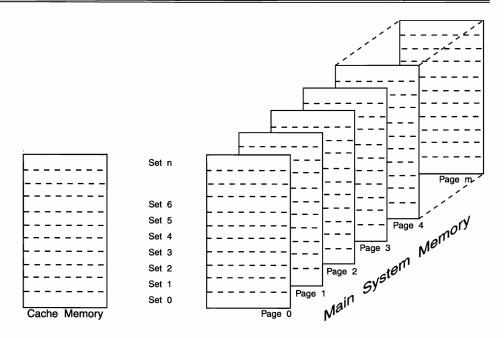

| Figure 14-9. Set-Associative Organization-Direct-Mapped                  | .302  |

| Figure 14-10. Direct-Mapped Cache Organization                           |       |

| Figure 14-11. Two-Way Set-Associative Cache Organization                 |       |

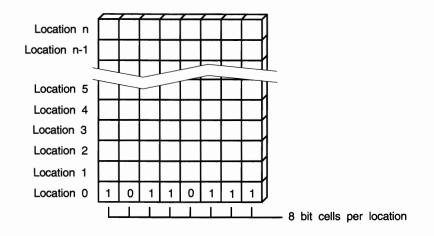

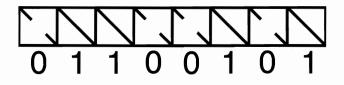

| Figure 15-1. The Bit Cell                                                |       |

| Figure 15-2. The PROM Bit Cells                                          | .317  |

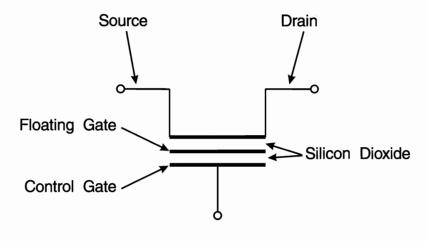

| Figure 15-3. The EPROM Bit Cell                                          |       |

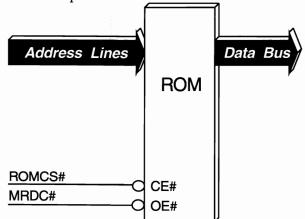

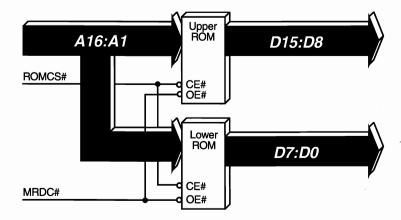

| Figure 15-4. The ROM's Interface to the System                           |       |

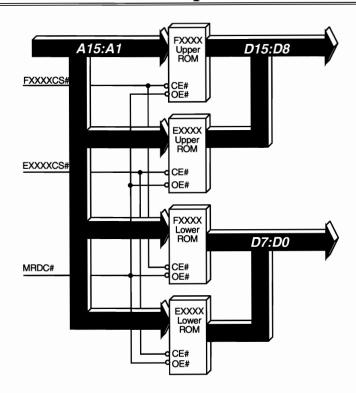

| Figure 15-5. System Board ROM Configuration with 32KB ROMs               | .329  |

| Figure 15-6. System Board ROM Configuration with 64KB ROMs               | . 330 |

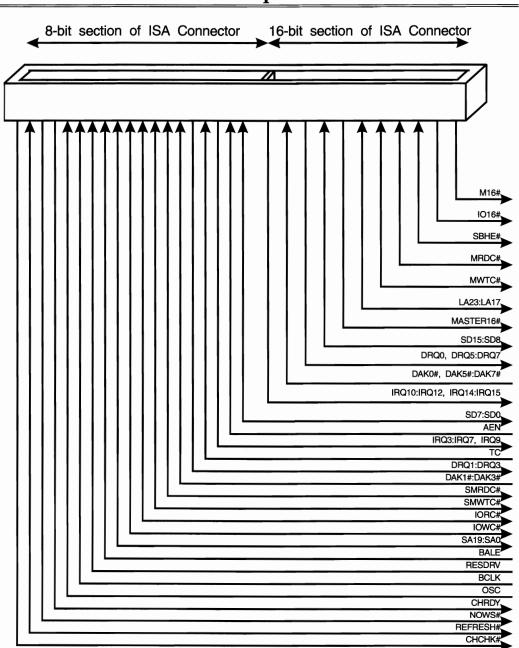

| Figure 16-1. The 8-bit Portion of the ISA Bus                            |       |

| Figure 16-2. The 16-bit Portion of the ISA Bus                           | .336  |

| Figure 16-3. The ISA Connector                                           |       |

| Figure 16-4. The ISA DMA Signals and Associated System Board Logic       | .346  |

| Figure 16-5. The ISA Interrupt Signals and Associated System Board Logic | .348  |

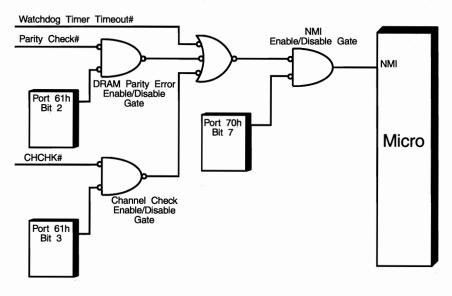

| Figure 16-6. The Channel Check Logic                                     | 349   |

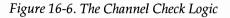

| Figure 17-1. Standard Access to an 8-bit ISA Device                      | . 353 |

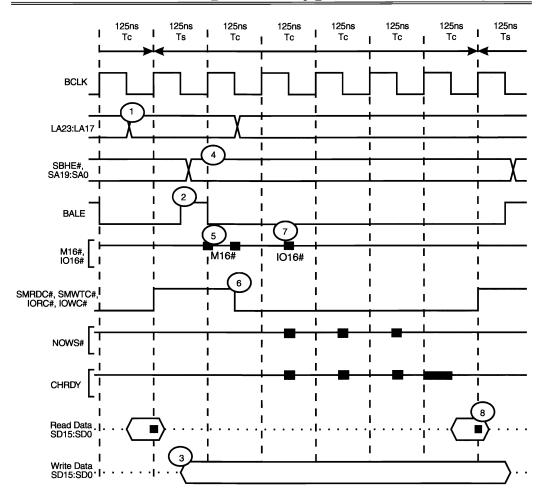

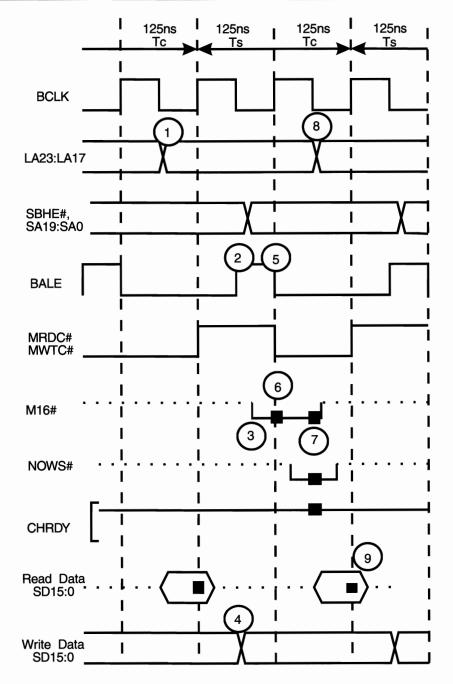

| Figure 17-2. Standard Access to a 16-bit ISA Memory Device               |       |

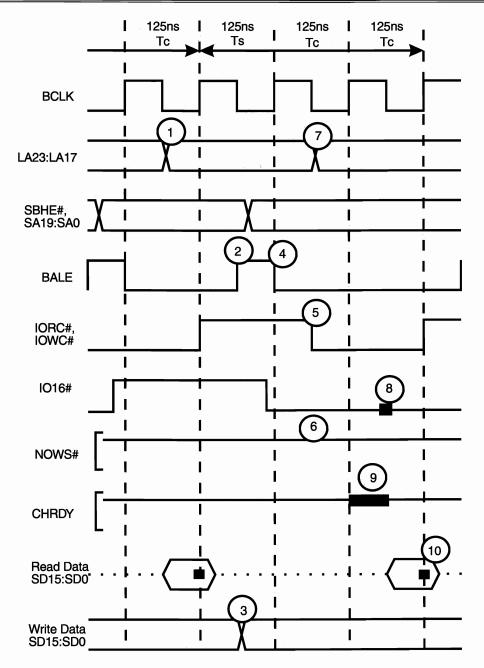

| Figure 17-3. Standard Access to 16-bit I/O device                        | 360   |

| Figure 17-4. Zero-Wait-State Access to a 16-bit ISA Memory Device        | 363   |

| Figure 18-1. Flowchart of Interrupt Servicing                            |       |

| Figure 18-2. The Intel 8259 Programmable Interrupt Controller (PIC)      | 368   |

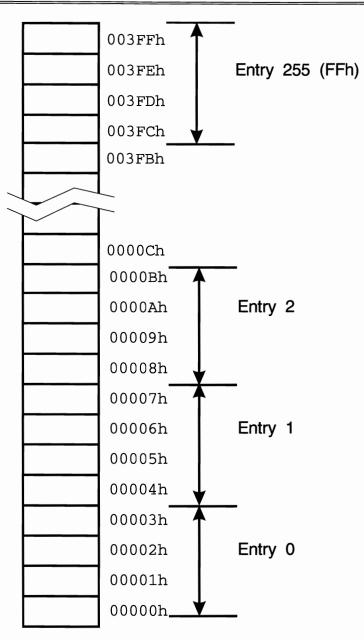

| Figure 18-3. The Interrupt Table (in Real Mode)                          | 370   |

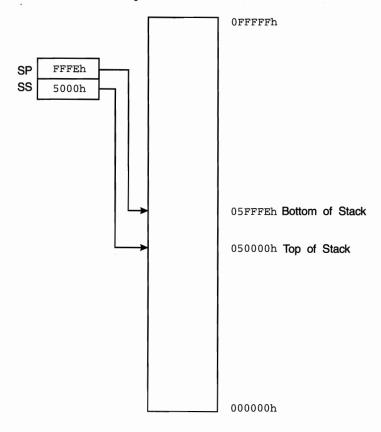

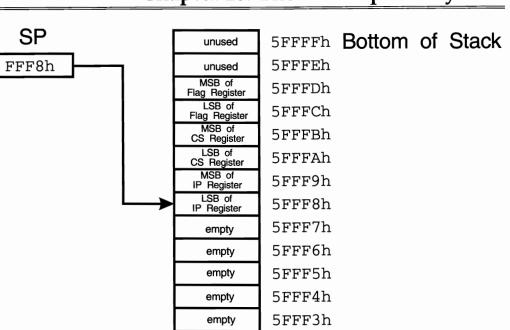

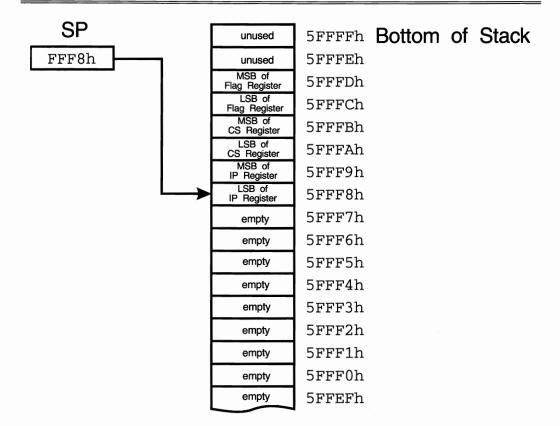

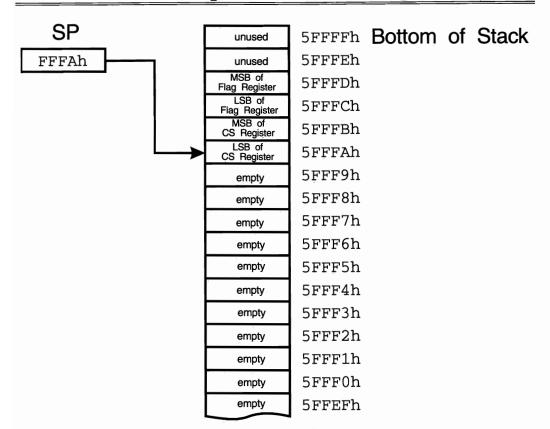

| Figure 18-4. The Stack                                                   | 373   |

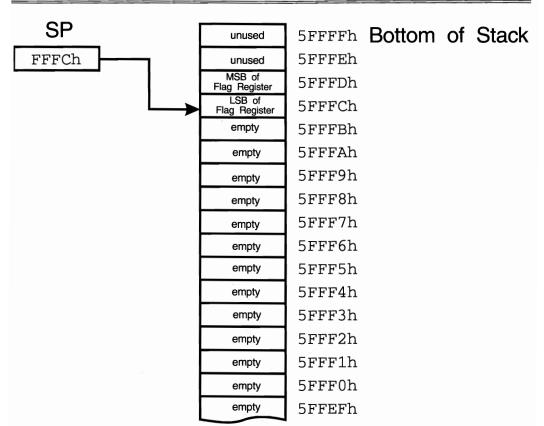

| Figure 18-5. Stack After Flag Register Push Operation                    |       |

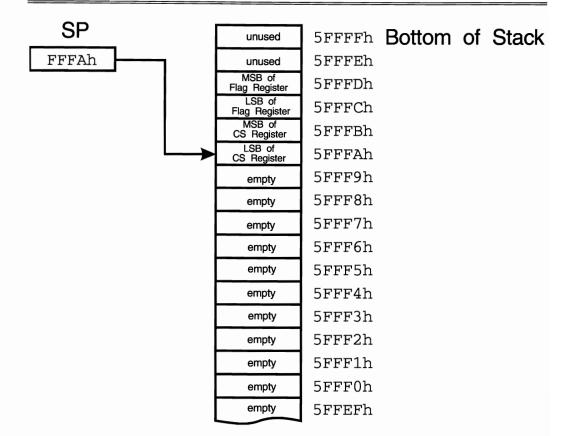

| Figure 18-6. Stack After CS Register Push Operation                      |       |

| Figure 18-7. Stack After IP Register Push Operation                      | .377  |

## ISA System Architecture

| Figure 18-8. Stack Before Pop Operation to Read IP Register       | 380 |

|-------------------------------------------------------------------|-----|

| Figure 18-9. Stack Before Pop Operation to Read CS Register       |     |

| Figure 18-10. Stack Before Pop Operation to Read Flag Register    |     |

| Figure 18-11. Cascaded Interrupt Controllers                      |     |

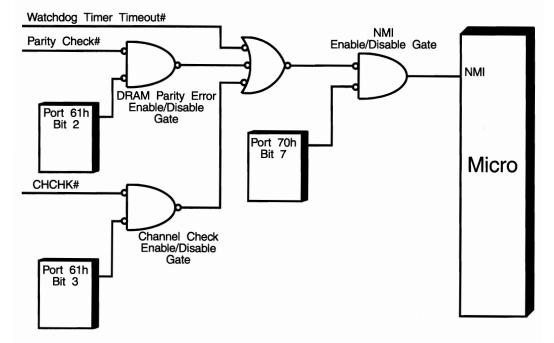

| Figure 18-12. Causes of a NMI                                     |     |

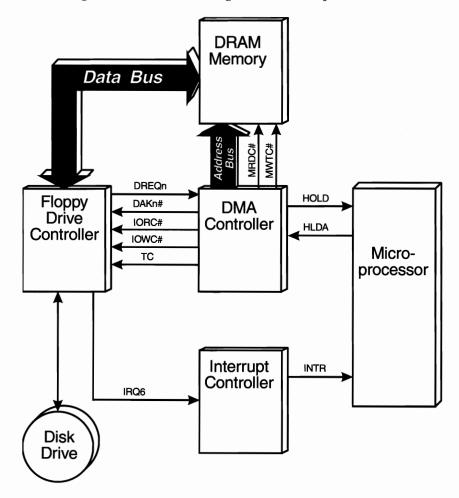

| Figure 19-1. Example Disk/DMA Hardware System                     |     |

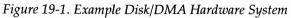

| Figure 19-2. Cascaded DMA Controllers                             |     |

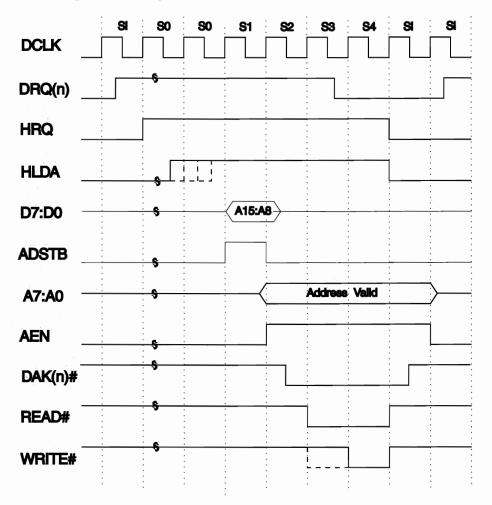

| Figure 19-3. Single Transfer Mode Timing                          |     |

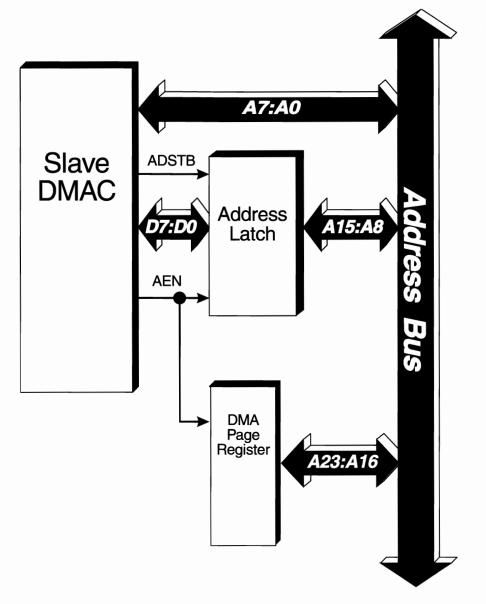

| Figure 19-4. The Slave DMAC Memory Address Logic                  |     |

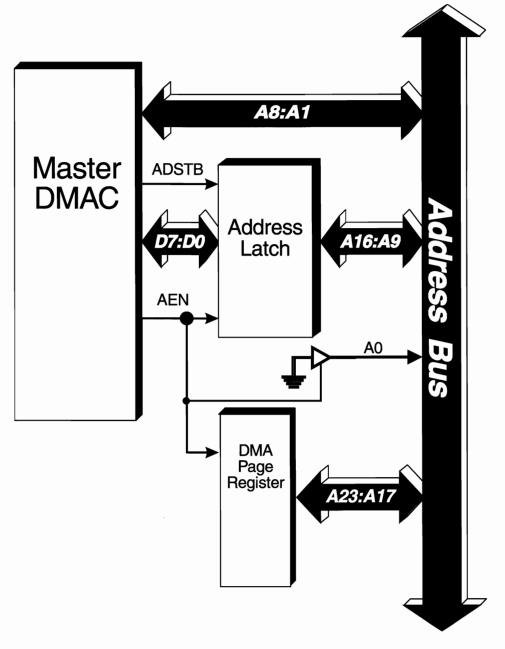

| Figure 19-5. The Master DMAC Memory Address Logic                 |     |

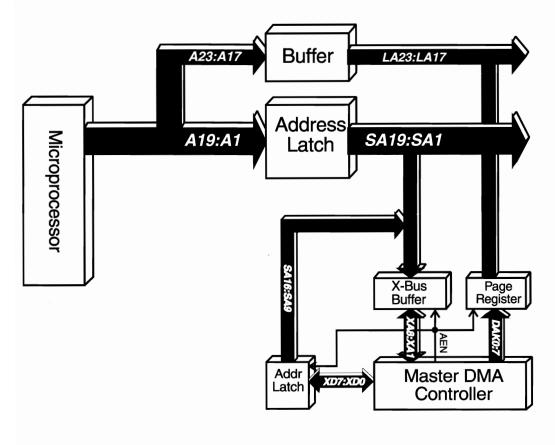

| Figure 19-6. Master DMAC Addressing 16-bit ISA Memory             | 427 |

| Figure 19-7. DMA (16-bit channel) Addressing 32-bit System Memory | 428 |

| Figure 19-8. 16-bit Access to 32-bit Memory with DMA              | 429 |

| Figure 20-1. DMA and Bus Mastering                                | 434 |

| Figure 20-2. ISA Bus Master Addressing 32-bit System Memory       | 436 |

| Figure 20-3. Addressing 32-bit Memory with ISA Bus Masters        | 437 |

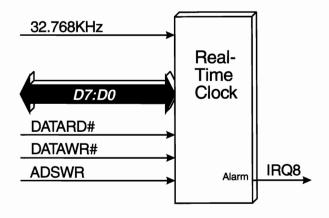

| Figure 21-1. The RTC/Configuration RAM Chip                       | 443 |

| Figure 22-1. The Keyboard Controller                              |     |

| Figure 22-2. Sample 8042 Configuration                            | 452 |

| Figure 23-1. The 80287 Numeric Coprocessor                        | 462 |

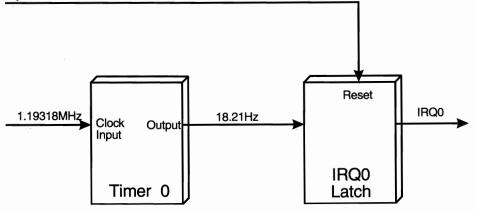

| Figure 24-1. The System Timer, Timer 0                            | 470 |

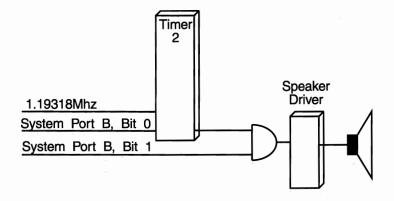

| Figure 24-2. The Speaker Timer and Associated Logic               | 472 |

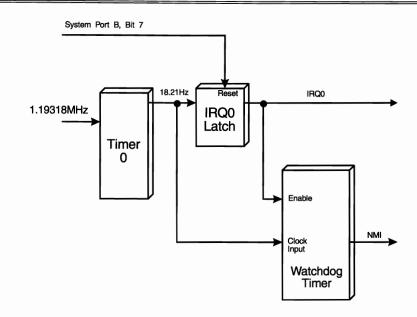

| Figure 24-3. The Watchdog Timer and Associated Logic              |     |

## Tables

| Table 4-1. State of the Address Lines When Any Memory Address in                |    |

|---------------------------------------------------------------------------------|----|

| Range F0000h to FFFFFh Is Addressed4                                            | 3  |

| Table 4-2. State of the Address Lines when any Memory Address in                |    |

| Range E0000h to EFFFFh Is Addressed4                                            | 4  |

| Table 4-3. System Board I/O Address Sub-Range Assignments4                      | 18 |

| Table 4-4. 74138 Output Selection Criteria5                                     | 50 |

| Table 4-5. I/O Address Range Assigned to Each System Board Device               | 52 |

| Table 5-1. The Flag Register's Status, Control and System Bits                  | 51 |

| Table 5-2. The 80286 MSW Register Bits6                                         | 52 |

| Table 5-3. Little-Endian Byte Ordering7                                         | ′4 |

| Table 5-4. Big-Endian Byte Ordering (not used on x86)7                          | ′4 |

| Table 5-5. Memory Contents7                                                     | 75 |

| Table 5-6. Binary Weighted Value of each Address Line8                          |    |

| Table 5-7. Transfer Size Indicated by A0 and BHE#8                              |    |

| Table 5-8. Examples of Even and Odd Addresses8                                  | 39 |

| Table 5-9. Bus Cycle Definition                                                 |    |

| Table 5-10. Attribute Byte Definition10                                         | )5 |

| Table 6-1. CMOS Reset Code Definition11                                         |    |

| Table 7-1. Values Preset Into 8086 and 8088 Microprocessor Registers by RESET11 |    |

| Table 7-2. State of 80386DX Outputs While RESET is Asserted11                   |    |

| Table 7-3. State of 80286 Outputs While RESET Is Asserted11                     |    |

| Table 8-1. Number of Wait States—Default Ready Timer13                          | 35 |

| Table 9-1. 80286 Bus Cycle Definition14                                         | 10 |

| Table 9-2. 80286 and 80386 Bus Cycle State Names14                              |    |

| Table 10-1. Format of Page Table Entry Attribute Bits16                         |    |

| Table 10-2. Signals Common to the 80286 and 80386DX Microprocessors17           |    |

| Table 10-3. Example Addresses Output by an 80386DX17                            | 77 |

| Table 10-4. Relationship of 80386DX Byte Enables, Data Paths and                |    |

| Locations in the Currently-Addressed Doubleword17                               |    |

| Table 10-5. Relationship of Addresses and Byte Enables Output by an 80386DX18   |    |

| Table 10-6. 80386DX Addressing Examples                                         |    |

| Table 10-7. 80386DX Byte Enable Combinations                                    |    |

| Table 10-8. Example Instructions and Resultant Addresses                        |    |

| Table 10-9. 80386 Bus Cycle Definition    18                                    | 35 |

| Table 10-10. Interface Signals That Differentiate the 80386SX from              |    |

| the 80386DX Microprocessor                                                      |    |

| Table 12-1. 80386 Bus Unit States                                               |    |

| Table 14-1. Cache Size vs. Hit Rate                                             | 0  |

## ISA System Architecture

| Table 15-1. The ROM's Interface Signals                                 |  |

|-------------------------------------------------------------------------|--|

| Table 16-1. The ISA Address-Related Signals                             |  |

| Table 16-2. The ISA Data Bus Paths                                      |  |

| Table 16-3. Bus Cycle Definition Line Decoding                          |  |

| Table 16-4. The ISA Command Lines                                       |  |

| Table 16-5. Bus Cycle Timing Signals                                    |  |

| Table 16-6. The Size 16 Signal Lines                                    |  |

| Table 16-7. The ISA DMA Signal Lines and Associated System Board Logic  |  |

| Table 16-8. ISA Bus Interrupt Request Line Assignment                   |  |

| Table 16-9. Interrupt Request Line Assignment, Lines Not on ISA Bus     |  |

| Table 16-10. The ISA Error Reporting Signal                             |  |

| Table 16-11. Miscellaneous ISA Signals                                  |  |

| Table 18-1. Standard ISA Interrupt Table entry number Assignments       |  |

| Table 18-2. Initialization Sequence for the Master Interrupt Controller |  |

| Table 18-3. Initialization Sequence for the Slave Interrupt Controller  |  |

| Table 18-4. System Control Port B at I/O Address 0061h (Read)           |  |

| Table 18-5. System Control Port A at I/O Address 0092h                  |  |

| Table 18-6. Interrupt Table Entry Assignment                            |  |

| Table 19-1. DMA Clock Frequency                                         |  |

| Table 19-2. DMAC States                                                 |  |

| Table 19-3. DMAC Memory Address and Page Registers—I/O Locations        |  |

| Table 19-4. ISA DMA Transfer Rates                                      |  |

| Table 19-5. Initialization of DMACs                                     |  |

| Table 21-1. The Real-Time Clock Bytes                                   |  |

| Table 21-2. RTC Status Register A                                       |  |

| Table 21-3. RTC Status Register B                                       |  |

| Table 21-4. RTC Status Register C                                       |  |

| Table 21-5. RTC Status Register D                                       |  |

| Table 21-6. Configuration RAM Usage                                     |  |

| Table 21-7. The Reset Code Byte                                         |  |

| Table 22-1. Sample Keyboard/Mouse Interface—Local Input Port            |  |

| Table 22-2. Sample Keyboard/Mouse Interface—Local Output Port           |  |

| Table 22-3. Keyboard/Mouse Interface—Test Port                          |  |

| Table 22-4. 8042 Sample Keyboard/Mouse Interface Command List           |  |

| Table 23-1. The Numeric Coprocessor Control Bits in the MSW Register    |  |

| Table 23-2. Intel Coprocessor/Processor Communication Signals           |  |

| Table 23-3. Weitek Interpretation of the Memory Address                 |  |

Have you ever started using a new tool and shortly thereafter wondered how in the world you ever got along without it? Well, that is how I feel about this book, and many of my technical compatriots here at Dell Computer Corporation would agree. Let's face it, the fast moving computer world is treacherous and follows Darwin's Law of Survival of the Fittest, where the strong survive and the weak get eaten. Don Anderson and Tom Shanley have provided you with a mechanism to maximize your chances of survival in this exciting world of computers.

ISA System Architecture is what I call the missing link. There exist many complementary tools to this book such as various chip data books, programming manuals, "light" architecture books, "how to" books, logic analyzers, scopes, debuggers, digital logic textbooks and so forth, but none that describe the AT architecture from a system point of view in such an organized and understandable fashion. All of the fundamental and critical areas of a functional ISA system are explained in detail with diagrams and examples including bus cycles, addressing, I/O and memory, decode logic, reset logic, power-up, microprocessors, the system kernel, RAM, cache, ROM, interrupts, DMA, busmastering, RTC and configuration RAM, keyboard/mouse interface, coprocessor, timers, and more. Ergo, you've got a comprehensive reference on AT system functionality; you've got the missing link.

We were fortunate to have Don and Tom conduct several training classes based on this book here at Dell (and continue to do so). Members of my group consist of engineers and technicians who are first to test systems after they leave development; we perform a variety of tests including hardware, software, and environmental tests. The information obtained from this class and book was excellent, but what was pleasantly surprising was the reaction of the folks who attended these sessions. During the classes and right after, there were people throughout the lab with big grins saying something to the effect of "This is great. I've been wanting to tie all of this information together so I could not only understand it fully, but put it to good use." And they have put the information to good use, which has helped us improve our process and test smarter.

This book is quite valuable as a training tool. The first technical literature that a new engineer or technician in my group studies is this book. This allows him or her to learn not only the system but the fundamentals required to test and troubleshoot a system in the most efficient way. Many technical managers in other groups here such as design, manufacturing, sustaining, technical support, and repair use this book in a similar manner. As a matter of fact, training classes using this book are available on a fairly regular basis within our entire organization. Not only do our technical people have a sound foundation on the building blocks of a system, but throughout the company, the terminology used is consistent. A BALE is a BALE is a BALE throughout the company.

Finally, I'd like to expand on the concept of testing smarter and improving your process. All of us in this business know that we must improve our processes to successfully compete. We need to decrease our time-to-market cycles, perform more complex processes in this shorter time period, and achieve this improvement on increasingly complex products. This is a real, not imaginary, burden to bear! However, if implemented successfully, the benefits I've mentioned can be attained in addition to improved methods and throughput, better troubleshooting techniques, reduction in field returns, and an increase in customer service quality. Quite simply, this text can be used as a part of this process.

In closing, I'd like to commend Don and Tom for a job well done. There is no doubt that their blood, sweat and tears have produced an immensely valuable technical work that they can well be proud of. The book is an invaluable tool and reference on ISA architecture and time reading it is time well spent. You might just end up wondering how you ever got along without it!

Dave Greenberg B.S.E.E, C.Q.E. Manager, Test Operations Dell Computer Corporation To Jerry Farnham for his help in editing the earlier versions of this book and for his many ideas that were incorporated.

To John Swindle for his tireless attention to detail during the editing and revision of the third edition.

#### **The MindShare Architecture Series**

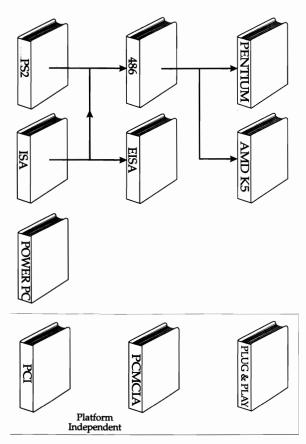

The MindShare Architecture book series includes: ISA System Architecture, EISA System Architecture, 80486 System Architecture, PCI System Architecture, Pentium System Architecture, PCMCIA System Architecture, PowerPC System Architecture, Plug-and-Play System Architecture, and AMD K5 System Architecture.

Rather than duplicating common information in each book, the series uses the building-block approach. *ISA System Architecture* is the core book upon which the others build. The figure that follows illustrates the relationship of the books to each other.

Series Organization

#### **Organization of This Book**

ISA System Architecture is divided into three parts:

- Part 1: The System Kernel. This section provides a detailed tutorial on how Intel X86 microprocessors communicate with memory and I/O devices. Included is the support logic which allows the microprocessor to communicate with 8- and 16-bit devices and detailed descriptions of the signals and timing involved in all Bus Cycle types.

- **Part 2: Memory Subsystems**. The memory section provides a detailed theory of operation of RAM and ROM devices, along with implementations commonly used in ISA systems. The section also covers the concepts and terminology related to cache memory designs.

- Part 3: The Industry Standard Architecture. This section provides a detailed discussion of the ISA Bus Architecture including ISA bus cycles and timing, along with ISA implementations of Interrupts, DMA, Real-Time Clock and Configuration RAM, Numeric Coprocessors, Keyboard/Mouse Interface, and Timers.

#### Who This Book Is For

This book is intended for use by hardware and software design and support personnel. Due to the clear, concise explanatory methods used to describe each subject, personnel outside of the design field may also find the text useful.

#### Prerequisite Knowledge

The approach taken by this book assumes moderate technical knowledge on the part of the technical audience. It is assumed that the reader has had exposure to PCs in a technical capacity (hardware designer, programmer, technical support, repair, and so on). Familiarity with the binary and hexadecimal numbering systems and their application to electronic computing is essential. To ensure an optimum level of understanding, every attempt is made to explain terminology as it is encountered and to avoid mystifying terms.

#### **Documentation Conventions**

This section defines the typographical conventions used throughout this book.

#### **Hex Notation**

All hex numbers are followed by an "h." Examples:

9A4Eh 0100h

#### **Binary Notation**

All binary numbers are followed by a "b." Examples:

0001 0101b 01b

#### **Decimal Notation**

When required for clarity, all decimal numbers are followed by a "d." Examples:

256d 128d

#### Signal Name Representation

Each signal that assumes the logic low state when asserted is followed by a pound sign (#). As an example, the REFRESH# signal is asserted low when the refresh logic runs a refresh bus cycle.

Signals that are not followed by a pound sign are asserted when they assume the logic high state. As an example, DREQ3 is asserted high to indicate that a device using DMA Channel three is ready for data to be transferred.

## Identification of Bit Fields (logical groups of bits or signals)

All bit fields are designated as follows:

[X:Y]

where "X" is the most-significant bit and "Y" is the least-significant bit of the field. As an example, the ISA data bus consists of SD[15:0], where SD15 is the most-significant and SD0 the least-significant bit of the field.

#### We Want Your Feedback

MindShare values your comments and suggestions. You can contact us via mail, phone, fax or Internet email.

Phone:

(214) 231-2216

Fax:

(214) 783-4715

Email:

mindshar@interserv.com

BBS:

(214) 705-9604

Mailing Address:

MindShare, Inc. 2202 Buttercup Drive Richardson, TX 75082 This book details the operation of ISA systems. Figure 1 below illustrates most of the subsystems covered. The book is divided into three major parts:

- The System Kernel

- Memory Subsystems

- The Industry Standard Architecture

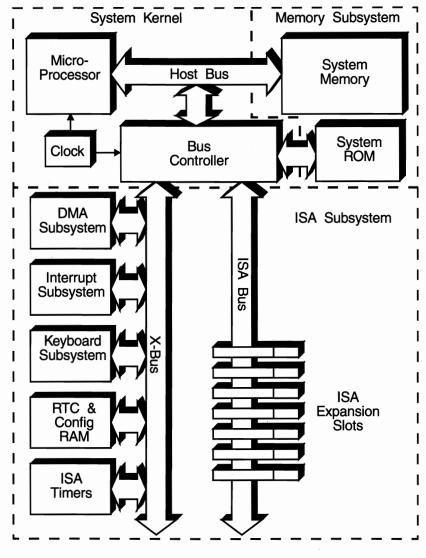

Figure 1. Simplified Block Diagram of Typical ISA System

In addition to detailed analysis of the hardware, many programming examples are covered with the purpose of tying the software and hardware together. This provides a very comprehensive understanding of system operation.

Refer to figure 1 during the following discussion of each major section.

#### System Kernel

The system kernel consists of the microprocessor and bus control logic, as well as other support circuitry not shown in figure 1. The kernel provides the basic signal, timing and protocols necessary for the microprocessor to communicate with the rest of the system.

This section provides a detailed tutorial on how Intel X86 microprocessors communicate with memory and I/O devices. Included is the support logic which allows the microprocessor to communicate with 8- and 16-bit devices and detailed descriptions of the signals and timing involved in all Bus Cycle types.

Several kernel implementations are possible with ISA systems depending on the exact processor used. Since ISA Architecture is based on the 8MHz IBM PC/AT, the initial kernel discussion is based on the Intel 80286 microprocessor running at 8MHz. 80286 microprocessors running at speeds faster than 8MHz require slight modification to the kernel. More drastic changes are required when using an 80386, 80486 or Pentium microprocessor in ISA systems. All major variations to kernel design and implementation are covered. Note that a thorough understanding of the 80286 kernel is essential before studying the 80386 kernel and that a thorough understanding of the 80386 kernel is essential before studying the 80486 and Pentium processors.

#### **Memory Subsystems**

Memory subsystems include main system memory, system ROM, and cache memory (not shown in figure 1). Design of the memory subsystem is key to obtaining maximum system performance at a reasonable price. A wide variety of memory devices are used in ISA systems to achieve high yet economical performance. Along with these devices come various memory architectures also designed to increase system performance. The memory section provides a detailed theory of operation of RAM and ROM devices, along with implementations commonly used in ISA systems. The section also covers the concepts and terminology related to cache memory designs.

#### ISA Subsystem

The ISA subsystem includes the bus structures and standard devices used in all ISA systems. The ISA buses operate at speeds of 8MHz to 8.33MHz and include ability to communicate with both 8- and 16-bit devices. By having a range of allowable bus speeds, the system designer can easily divide the microprocessor's clock frequency down to the ISA clock frequency. Specific functions common to all ISA systems include Direct Memory Access (DMA), Interrupts, Keyboard, Real-Time Clock (RTC) and Configuration RAM, and the ISA Timers. Each of these functions must operate according to ISA standards.